Процессор для цифровой обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

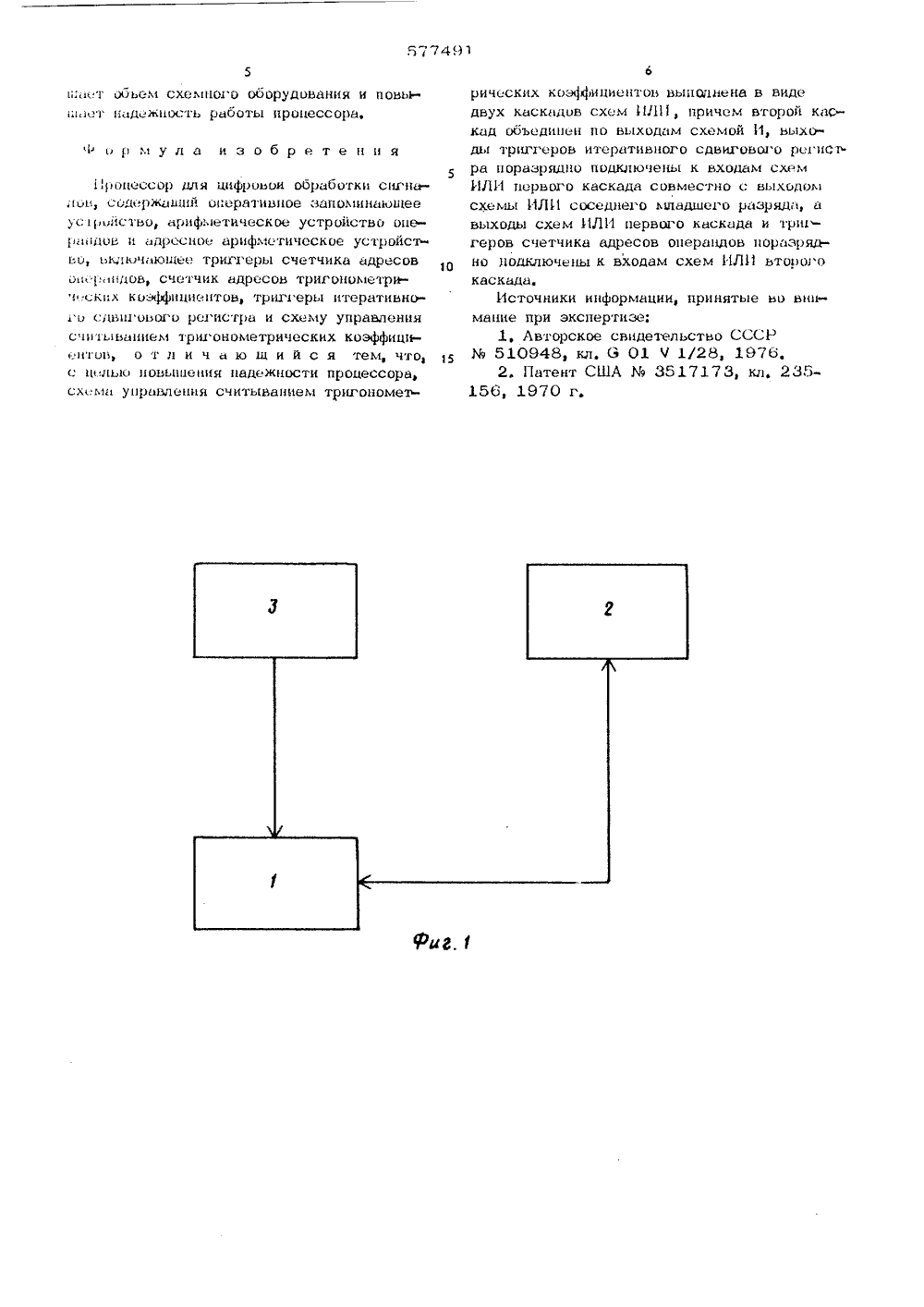

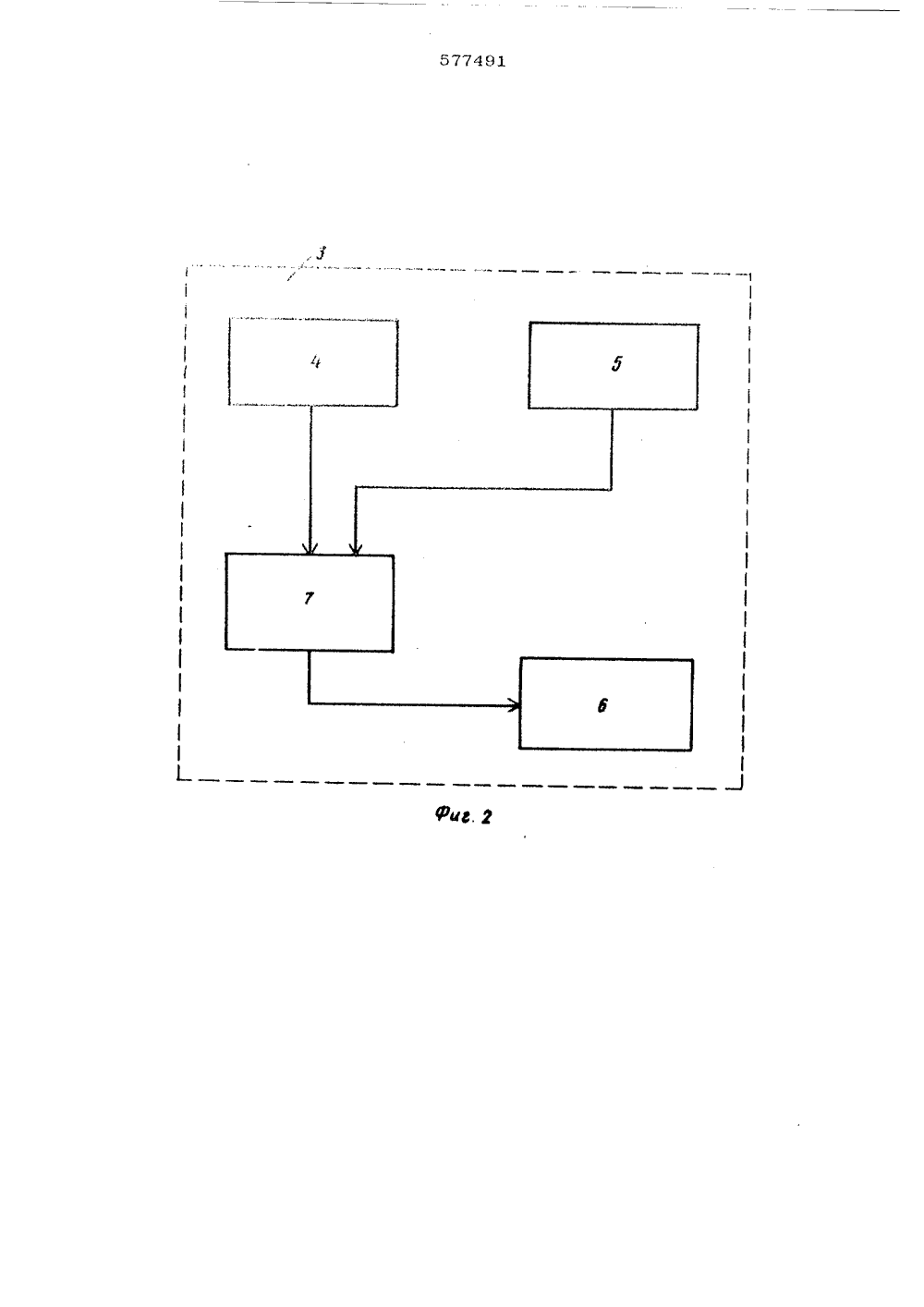

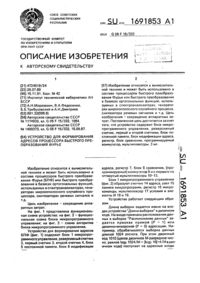

(22) Залвлено 22,01,76(21) 231579612с присоединением заявки51) Ч Кл С 01 Ч 1/28 Государственный комитет Совета Инннстраа СССР оо делам изобретений и открытий(71) Заявитель 4) ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВвый регистр, счетчик адресов тригонометрических коэффициентов и схему управления считыванием тригонометрических коэффициентов (21Одним из основных алгоритмов, реализуемых процессорами для цифровой обработки сигналов, является быстрое преобразование Фурье (БПФ), БПФ - итеративный процесс, выполняемый над массивами чисел величиной й = 2, Число итеративных циклов равно при этом показателю степени В, а номер выполняемой итерации изменяется от 1 дощВ пределах одной 1 -; 1 й итерации нас всеми данными для каждой пары точек выполняются две однотипные операции:(в ОЗУ 1 Рю созй+з 6циенты,Изобретение относится к области специализированных вычислителей для цифровой оЬ- работки сигналов, и в частности для обрабоч ки материалов сейсморазведки.Известен процессор цифровой обработки информации, содержащий регистры слагаемых, устройство умножения и суммат р,;хемы формирования переносов, предварительных и окончательных сумм, схему формирования знака результата и схему анализа знаковых разрядов слагаемых, а также связи межрч блоками (1 ), Однако известное адресное арифметическое устройство процессора не защищеноз хотя наличие его в процессорепозволяетполучить скорость вычислений, например в алгс ритме быстрое преобразование фурье (БПФ) теоретически недостижимую в универсальных ЭВМ.Наиболее близким для предлагаелюго технического решения является процессор для цифровой обработки сигналов, содержапп;й оперативное запоминающее устройство, арирметическое устройство операндов и адресное арифметическое устройство, вкпючаюшее счет чик адресов операндов, итеративный сцвиго А (к) - две исходные точки,-той итерации с адресамп К соответственно, а 8 - тригонометрические ноеффпЭти коэффициенты ддя числа точек Х расе энтывррнэтся заранее в количестве - ий2хррэнэпс:я в оперативной памяти,В каждой итерации дня вычислений пофэрэлул; м (1) необходимы значения тригонометрических коэффициентов в количествер зависящем от номера выполняемой итерации: впервой - одно значение,во второи - два, втретьей - четыре и т,дв последней итерации необходимо считать из оперативной наму ти все - значении тригонометрических козЬй2фициентов.В известном процессоре схема управления считыванием тригонометрических коэффициентов фиксирует состояние, нри которомдля расчета очередной пары точек необходимо использовать новое значение тригонометрического коэффициента, считанного в буферные регистры из оперативной памятл в предыдущем цикле смены тригонометрическогокоэффициента,В указанный момент времени значениетригонометрического коэффициента передается из буферных регистров в регистры множителя арифметического устройства операндов,5из оперативной памяти в буферные регистоысчитывается очередное значение тригонометрцчЖкихкоэффициентов и начинается цикл расчетаочередной пары точек,Недостатком описанного процессора явля- З 0ется необходимость введения в его состав убуферных регистров с управляющей логикойдля записи - считывания информации, чтоприводит к увеличению схемного оборудования и снижению надежности работы процеосора,Целью изобретения является повышениенадежности процессора,Это достигается,тем, что в предлагаемомпроцессоре схема управления считываниемтригонометрических коэффициентов содержитдва каскада схем РИР 1 р причем второй каскад объединен по выходам схемой И, выходы триггеров итеративного сдвиг ового регистра поразрядно подключены к входам45схем ИЛИ первого каскада совместно с выходом схемы ИЛИ сээреднего младшего разряда, а выходы схем ИЛИ первого каскадаи триггеров счетчика адресов операндов поразрядно подключены к входам схем ИЛИ50второго каскада,В этом случае схема управления считыванием тригонометрических коэффициентов фиксирует цикл, предшествующий циклу расчета пары точек, для которого необходимо новое значение тря онометрического коэффициента- и обеспечивает синхронизацию считывания триго нометрических коэффициентов из оперативной памяти неносгэелс твенно в регистры арифметического устройства операндов. Едагодаря этому, отпадает не обходим ость в буферных регистрах исвязанной с ними управляющей дотике, существенно сокращается объемсхемного оборудованияи повышается надежность работы процессора.На фиг, 1 изображена блок-схема предлагаемого процессора; на фиг, 2 - блочная схема адресного арифметичеСкого устройства;на фиг, 3 - схема управления считываниемтригонометрических коэффициентов,Процессор содержит оперативное запоминающее устройство 1, арифметическое устройство операндов 2 и адресное арифметическоеустройство 3.,Адресное арифметическое устройство 3"одержит счетчик адресов операндов 4, итеративный сдвиговый регистр 5, счетчик адресов тригонометрических коэффициентов 6и схему управления считыванием,тригономет.рических коэффициентов 7,Схема управления считыванием тригонометрических коэффициентов 7 для случая,например, четырехразрядного (четырехбитного) адреса содержит схемь ИЛИ 12 р 13 р 14 р 15второго каскада, объединенные по выходамсхемой И 16,Схема управления считьвянием тригонометрических коэффициентов для адресов сбольшей разрядностью строится аналогичносхемер приведенной на фиг, 3, путем добавления в каждом каскаде одной деухвходовой,схемы ИЛИ и добавлением одного входа всхеме И на каждый дополнительный двоичный разряд адреса,Входь. триггеров 17,18,19,20 итеративного сдвигового регистра 5 подключены ксоответствующим входам схем ИЛИ 8,9,10,11, ко вторым входам которых подключенывыходы схем ИЛИ соседних младших разрядов, выходы схем ИЛИ 8,9,10,11 подключны соответственно к входам схем ИЛИ 12,13,14,15, ко вторым вхоцам которых подключены выходы триггеров 21,22,23,24,соответствующих разрядов счетчика адресовоперандов 4,Всякий раз в -той итерацииединичноесостоянле на выходе схемы э 1 указывает нанеобходимость считывания нового тригонометрического коэффициента в регистры множителя арифметического устройства операндов,Примененле в предлагаемом процессоревышеприведенной схемы управления считыванием тригонометрическихкоэффициентов обеопечило считывание тригонометрических коэффициентов непосредственно в рабочие регистр.ры арифметического устройства операндов,что чсключает в процессоре буферные регистры с управляющей логикой, используемые впрактике, и за счет этого существенно уменьц; ы объем схемцк о оборудования и поьыц 1. надежность работы процессо 13 аФ ар мула изобретенияроцессор для ццфроьои обработки сцгнс- ;о, содржаццш оперативное задолнаюцее ус 1 йстьо, арифметическое устройство опер цоь и адресное арифметическое устройст ьо, ьк;юаюшее триггеры счетчика адресов оц 1 дов, счеик адресов тригоцометри.скцх коэффициентов, триг еры итеративного свигооого регистра и схелу управления счиыьацием тригонометрических коэффициецо, отличающийся тем,что, с цяью поьыцения надежности процессора, схема управления считыванием тригонометрических коэффициентов выпсйнена в видедвух каскадов схем 11 Л 11, причем второй каскад объединен по выходам схемой И, выходы триггеров итеративного сдвигового регцСт.ра поразрядно подкпюецъ к входам схмИЛИ первого каскада совместно с выходомсхемы ИЛИ соседнего лцтадшего разряда, авыходы схем ИЛИ первого каскада и ригеров счетчика адресов операндов поразрядно подключены к входам схем ИЛИ второгокаскада.Источники информации, принятые ьо вцчмание при экспертизе;1, Авторское свидетельство СССРЪ 510948, кл. Ь 01 Ч 1/28, 1976,2, Патент США М 3517173, кл, 235156, 1970 г,577491 аказ 3677l 34ОНИИПИ Гос Составитель В, Зверево Н, Хл дова Техред Н. Андрейчук Ко вкоо С, Шекма аж 717 Подписноеого комитета Совета Министров СССРизобретений и открытийква, Ж, Раушская наб д, 4/5 Тир ударствен по делам 035, Мос

СмотретьЗаявка

2315796, 22.01.1976

ЮЖНОЕ МОРСКОЕ НАУЧНО-ПРОИЗВОДСТВЕННОЕ ГЕОЛОГО-ГЕОФИЗИЧЕСКОЕ ОБЪЕДИНЕНИЕ "ЮЖМОРГЕО"

ГУЛЬМАН МАРК БОРИСОВИЧ, ЖБАНКОВ АЛЕКСАНДР ИВАНОВИЧ, МИРОНЮК АЛЕКСАНДР ГРИГОРЬЕВИЧ, АМИНЕВА ДИНА СЕРГЕЕВНА

МПК / Метки

МПК: G01V 1/32

Метки: процессор, сигналов, цифровой

Опубликовано: 25.10.1977

Код ссылки

<a href="https://patents.su/5-577491-processor-dlya-cifrovojj-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для цифровой обработки сигналов</a>

Предыдущий патент: Сейсмометр

Следующий патент: Устройство слежения за произвольной фазой сигнала при акустическом каротаже

Случайный патент: Устройство для определения средних моментов прохождений звезд при фотоэлектрических измерениях