Дискриминатор логических сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

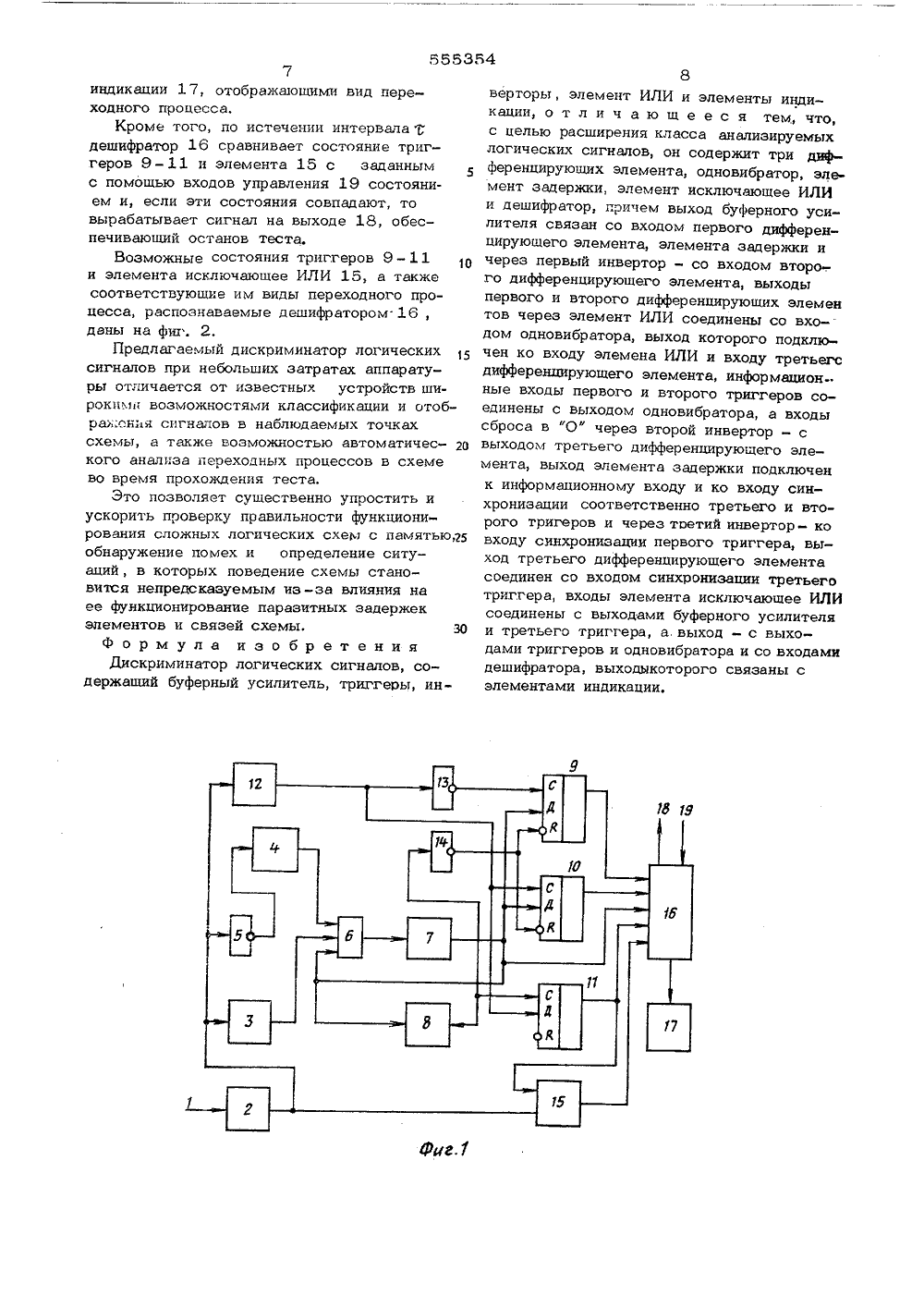

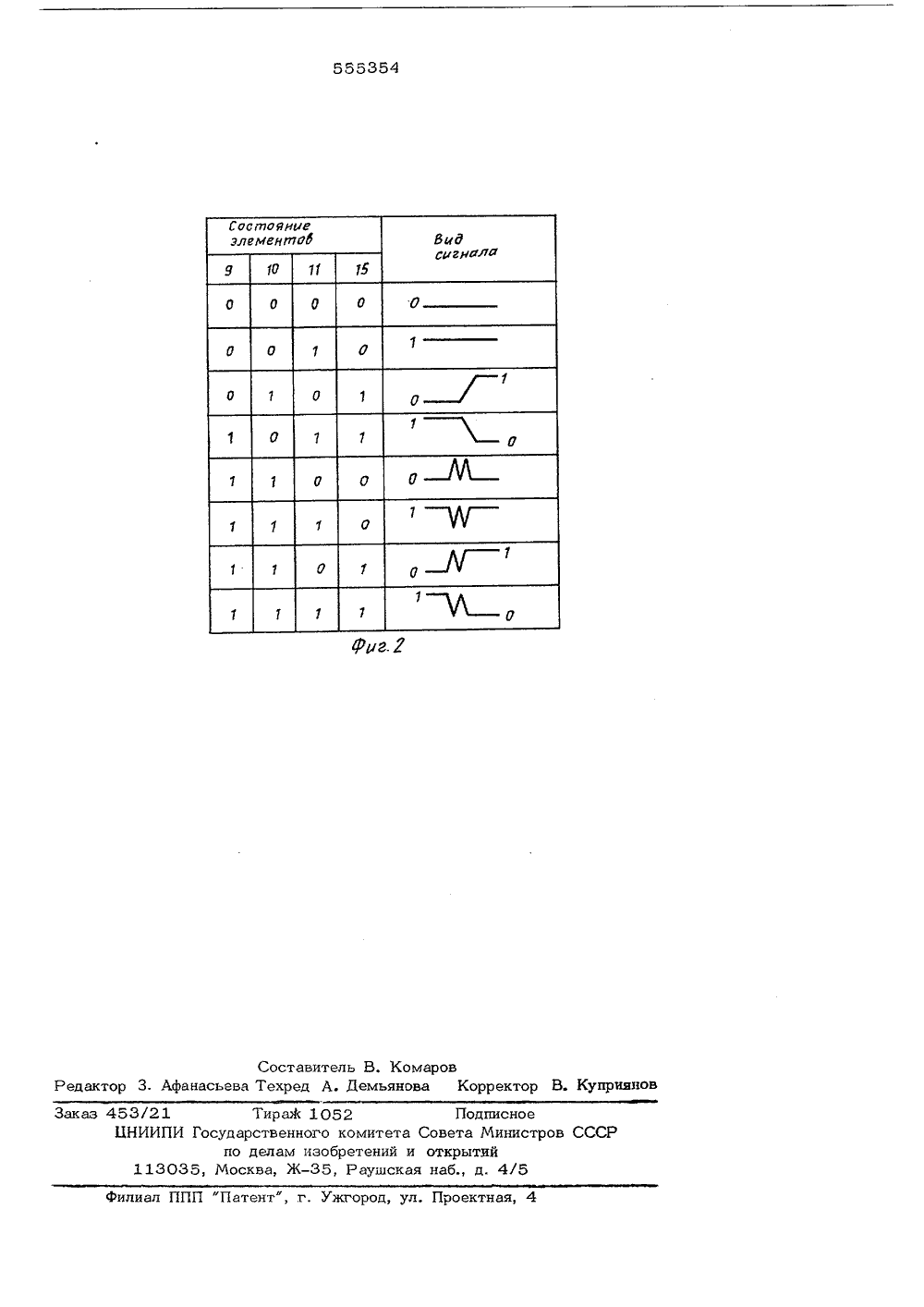

Союз СоветскихСоциалистическихРеспублик ОП ИСАЙ ИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(51) Цй=Кл,еС 01 Я 31/2 5 06 Е .1 г 0 22) Заявлено 16,0 5 (21) 214512 с присоединением заявкисударственный номитеавета Нинистроа ССС 9по делам изооретенийи открытий) Дата опубликования нил 28,05,77(72) Авторы изобретен Сергеев Д. М. Гробман и Заявитель нститут электронных управлявших маши ГИЧЕСКИ СИГНАЛОВ(54 ) ДИСКРИМИНАТ наченными для приема стробирующ налов ( например, от других точек х сиг- контролируемои схемы). Данное устройство позволяе вать статические значения "1" налов и число их изменений. О возможностей оказывается нед для поиска неисправностей в сл ческих схемах с память Кооме того, оно не иксироО" сигоиэти льсных сигнало таточножных лог мпаракотогической схем оры потенциало ых соединяются ю.озволяет людается сигнал кладываеносятся из ить,к како логикомпа ого к контрол енения сигнал том инточ мент й в схемемким процес льтате п 15 оказывается с сом. во вляются ограниченнь икации и отображен Это связано с тем, что для схем с памятью существенными являются не только статические значения0 такте работы, но и в са при смене одного м гналов о процес- значения переходи атическог ы переходных процес другим. Некоторые висов в определенных тоются недопустимыми,зависимости установив азыва ах схемь дят гося состояни Изобретение относится к области вычилительной техники и, в частности, к средствам контроля и диагностики неисправно тей логических схем. Известно устройство, предназначенное для анализа и индикации потенциальных ив в контролируемои лооторое содержит ко "1" и "О", входы с точкой схемы, где наби триггеры, входы котоых непосредственно или че элементы связаны с выходамиров, а выходы подключены к эдикации.Недостатком я можности классиф ия логических сигналов.Известно устройство, содержащее буферный усилитель, триггеры, инверторы и элемент ИЛИ, элемент индикации, выход которого соединен со входами триггеров, а вхо ды - с выходом буферного усилителя и инверторов, входы которых связаны с дополнительными входами устройства, предназтакту теста, прируемой схеме,а в наблюдаемоск неисправностожным и трудоементов лм ятй от конкретных значений паразитных задержек элементов и связей схемы и, следовательно, делают ее поведение непредсказуемым, Причем для разных конфигураций схем, разных типов элементов 5 памяти и разных внутренних состояний схемы недопустимыМи могут быть совершенно различные виды переходных процессов,Если ограничиться наиболее широко распространенными на практике потенциальны ми логическими схемами, то для проверки правильности функционирования схемы на прикладываемой к ее входам последовательности сигналов и фиксации всех ситуаций, в которых поведение схемы непредсказуемо, 15 оказывается необходимым различать следующие виды сигналов неизменное состояние "О", неизменное состояние "1", однократное изменение (гладкий фронт) с "О" на "1", однократное изменение (гладкий 20 фронт) с "1" на "О"; положительные выбросы в состоянии "О" (статический риск в "О" ); отрицательные выбросы в состоянии 1 ф (статический риск "1"), многократное изменение при переходе с "1" на 25 "О" (динамический риск в "1"); многократное изменение при переходе с фОф на ф 1 ф (динамический риск в фОф ) .Известное устройство не обеспечивает в полном объеме различение указанных видов З 0 сигналов и, таким образом, оказывается малопригодным для контроля сложных логических схем с памятью.Поскольку в устройстве отсутствуют средства для автоматического обнуления триггеров перед началом каждого такта теста и средства анализа состояния этих триггеров, оно не позволяет определить, к какому такту относятся зафиксированные изменения сигнала. Поэтому те ограниченные возмож ности классификации переходных процессов, которые имеются у устройства, могут быть реализованы только в неавтоматическом режиме, а именно путем наблюдения за индикацией при ручном запуске приложения к45 контролируемой схеме каждого очередного такта теста и ручном сбросе перед запуском каждого такта. Это делает процесс анализа сигнала в схеме ( и в частности, недопустимых их изменений, вызывающих неп 50 редсказуемое поведение) очень трудоемким.Белью изобретения является расширение класса анализируемых логических сигналов.Это достигается тем, что дискриминатор "одержит три дифференцируюших элемента,55 оцновибратор, элемент задержки, элементисключаюшее ИЛИ и дешифратор, Причем выход буферного усилителя связан со входом перв:го дифференцирующего элемента, элемен 60 та,з;держки и через первый инвертор со входом второго дифференцируюшего элемента. Выходы первого и второго дифференцируюших элементов через элемент ИЛИ соединены со входом одновибраторавыход которого подключен ко входу элемента ИЛИи входу третьего дифференцирующего элемента. Информационные входы первого ивторого триггеров соединены с выходом одновибратора, а входы сброса в "О" через второй инвертор - с выходом третьего дифференцирующего элемента. Выход элементазадержки подключен к информационномувходу и ко входу синхронизации соответственно третьего и второго триггера и черезтретий инвертор - ко входу синхронизациипервого триггера, Выход третьего дифференцирующего элемента соединен со входомсинхронизации третьего триггера, входыэлемента исключающее ИЛИ соединены свыходами буферного усилителя и третьеготриггера, а выход - с выходами триггерови одновибратора и со входами дешифратора,выходы которого связаны с элементами индикации.На фиг. 1 изображен дискриминатор;на фиг. 2 - распознаваемые виды переходных процессов и соответствующие им состояния триггеров.Дискриминатор содержит вход 1 устройства, буферный усилитель 2, первый дифференцируюший элемент 3, второй дифференцируюший элемент 4, первый инвертор 5,элемент ИЛИ 6, одновибратор 7, третийдифференцируюший элемент 8, первый триггер 9, второй триггер 10, третий триггер11, элемент задержки 12, третий инвертор 13, второй инвертор 14, элемент исключающее ИЛИ 15, дешифратор 16, элементы индикации 17, выход 18 прерываниятеста, входы 19 управления,Вход 1 устройства связан с остальнымиего элементами через буферный усилитель2, который предотвращает искажение формы сигнала в исследуемой точке логической схемы при подключении к ней дискриминатора, Выход элемента 2 связан с первыми вторым дифференцируюшими элементами3 и 4, причем связь со вторыми из этихэлементов осуществляется через первыйинвертор 5, Выходы дифференцирующих элементов 3 и 4 через элемент ИЛИ 6 соединены со входом одновибратора 7, на выходе которого включен третий дифференцируюший элемент 8, Выход одновибратора7 подключен ко входу элемента ИЛИ 6.Перечисленные элементы и связи предназначены для обнаружения на входе 1 первого изменения сигнала, соответствующегоначалу очередного такта работы схемы (этифункции выполняют элементы 3-6, формирования временного интервала (одновибратор 7,), определяющего максимально всзможную длительность переходного процесса, в каждом такте, и формирования сигнала (дифференцируюший элемент 8), обеспечивающего приведение устройства в исходное состояние в начале каждого такта.Для фиксации различных видов изменения сигнала на входе 1 устройство содержит первый, второй и третий триггеры 9- 10 11. Информационные входы (Д) триггеров 9,10 соединены с выходом одновибратора 7. Информационный вход триггера 11 и вход синхронизации (С) триггера 10 связаны через элемент задержки 12 с выхо дом буферного усилителя 2, вход синхронизации триггера 9 соединен с выходом элемента задержки 12 через третий инвертор 13.Вход синхронизации триггера 11 непос редственно и входы сброса (Б ) триггеров 9 и 10 через второй инвертор 14 подключены к выходу третьего дифференцируюшего элемента 8.Выходы буферного усилителя 2 и третье го триггера 1 1 соединены со входами элемента исключающее ИЛИ 15, который служит для сравнения состояния входа 1 до первого его изменения в текущем такте и установнвшегося состояния входа в конце З 0 этого такта.Выходы элемента 15, триггеров 9 - 11 и одновибратора 7 связаны со входами дешифратора 16, который предназначен для преобразования состояния указанных тригге- З 5 ров в сигналы, соответствующ.;е определенным видам переходного процесса в исследуемой точке логической схемы (см. фиг.2). Выходы дешифратора 16 служат для визуального отображения переходного процесса, 40 Дополнительный выход 18 предназначен для выдачи сигнала прерывания (останова), прикладываемого к анализируемой схеме теста в том его такте, в котором в исследуемой точке схемы обнаружен определенный вид переходного процесса. Вид переходного процесса (например, статический риск или динамический риск), при котором вырабатывается сигнал на выходе 18, задается с помощью входов управления 19. В качестве триггеров 9 - 11 могут быть использованы обычные управляемые фронтом триггеры типа Д.55Устройство работает следующим образом.После подключения входа 1 к исследуемой точке логической схемы ко входам схемы прикладывается тест. Длительность так 60 та Т теста (т,е, интервала между двумяЧс соседни,ш по времени изменениям входных сигналов схемы) и длительность Г интервала, формируемого одновибратором 7, выбираются из условияГтгде- максимально возможная продолижительность переходного процесса в схеме.Длительность интервала Т устанавливается путем регулировки времязадающих цепей одновибратора 7.Каждое очередное изменение сигнала в исследуемой точке схемы, возникающее в результате приложения теста, фиксируется дифференцирующими элементами 3 и 4, пер вый из которых распознает изменение с "О" на "1", а второй - с "1" на "О".Первое в очередном такте теста изменение сигнала в исследуемой точке вызы - вает появление импульса на выходе элемента ИЛИ 6, который производит запуск одновибратора 7. При этом за счет обратной связи с выхода одновибратора на одном из входов элемента ИЛИ 6 устанавливается сигнал ф 1", который в течение интерваладелает этот элемент нечувствительным ко всем последующим изменениям сигнала на входе 1 дискриминатора.На переднем фронте вырабатываемого оцновибратором 7 импульса длительностьюГ дифференцирующий элемент 8 выдает короткий импульс, который обеспечивает приведение в исходное состояние триггеров 9 - 11, При этом триггеры 9,10 устанавливаются в "О", а триггер 11-в состояние, которое имело место в исследуемой точке схемы до первого его изменения в очередном такте. Далее задержанный элементом 12 (на время действия импульса начачьной установки триггеров 9,10,11) сигнал со входа 1 передается на входы синхронизации триггеров 9,10, на информационных входах которых одновибратор 7 поддерживает сигнал "1 ф в течение всего интервала Т , Если внутри этого интервала происходит хотя бы одно изменение сиг. нала на входе 1 с "1" на "О" то первый триггер 9 устанавливается в "1 ", если происходит хотя бы одно изменение с "0" на "1", то устанавливается в ф 1" второйтриггер 10.После окончания переходного процесса на входе 1 элемент исключающее ИЛИ 15 производит сравнение предшествующего (до первого изменения) состояния этого входа, зафиксированное третьим триггером 11, и установившегося состояния входа. При равенстве этих состояний выход элемента 15 имеет значение фО", при неравенстве - "1", Далее состояние триггеров 9-11 и элемента 15 анализируется дешифратором 16, который управляет элементами7индикации 17, отображающими вид переходного процесса.Кроме того, по истечении интервала Т дешифратор 16 сравнивает состояние триггеров 9 - 11 и элемента 15 с заданным с помощью входов управления 19 состоянием и, если эти состояния совпадают, то вырабатывает сигнал на выходе 18, обеспечивающий останов теста.Возможные состояния триггеров 9- 11 и элемента исключающее ИЛИ 15, а также соответствующие им виды переходного процесса, распознаваемые дешифратором. 16, даны на фиг. 2.Предлагаемый дискриминатор логических сигналов при небольших затратах аппаратуры отличается от известных устройств широкимл возможностями классификации и отобрал;онпя сигналов в наблюдаемых точках схемы, а также возможностью автоматичес кого анализа переходных процессов в схеме во время прохождения теста.Это позволяет существенно упростить и ускорить проверку правильности функционирования сложных логических схем с памятью,2 обнаружение помех и определение ситуаций, в которых поведение схемы становится непредсказуемым из-за влияния на ее функционирование паразитных задержек элементов и связей схемы. 30Формула изобретенияДискриминатор логических сигналов, содержащий буферный усилитель, триггеры, ин 8верторы, элемент ИЛИ и элементы индикации, о т л и ч а ю щ е е с я тем, что, с целью расширения класса анализируемых логических сигналов, он содержит три дифференцируюших элемента, одновибратор, элемент задержки, элемент исключающее ИЛИ и дешифратор, гричем выход буферного усилителя связан со входом первого дифференцирующего элемента, элемента задержки и через первый инвертор - со входом второ-. го дифференцирующего элемента, выходы первого и второго дифференцируюших элемен тов через элемент ИЛИ соединены со входом одновибратора, выход которого подключен ко входу элемена ИЛИ и входу третьегс дифферендирующего элемента, информационные входы первого и второго триггеров соединены с выходом одновибратора, а входы сброса в "0" через второй инвертор - с выходом третьего дифференцирующего элемента, выход элемента задержки подключен к информационному входу и ко входу синхронизации соответственно третьего и второго тригеров и через тоетий инвертор- ко входу синхронизации первого триггера, выход третьего дифференцирующего элемента соединен со входом синхронизации третьего триггера, входы элемента исключающее ИЛИ соединены с выходами буферного усилителя и третьего триггера, а. выход - с выходами триггеров и одновибратора и со входами дешифратора, выходакоторого связаны с элементами индикации.Заказ 453/21 Тирай 1052 Подписное БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5 филиал ППП "Патент", г, Ужгород, ул. Проектная, 4

СмотретьЗаявка

2145121, 16.06.1975

ИНСТИТУТ ЭЛЕКТРОННЫХ УПРАВЛЯЮЩИХ МАШИН

ГРОБМАН ДАВИД МАТВЕЕВИЧ, СЕРГЕЕВ БОРИС ГЕОРГИЕВИЧ

МПК / Метки

МПК: G01R 31/3177

Метки: дискриминатор, логических, сигналов

Опубликовано: 25.04.1977

Код ссылки

<a href="https://patents.su/5-555354-diskriminator-logicheskikh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Дискриминатор логических сигналов</a>

Предыдущий патент: Устройство для измерения области работоспособности электронных схем

Следующий патент: Способ измерения коэрцитивной силы цилиндрических тонких магнитных пленок

Случайный патент: Центробежная машина