Устройство измерения отклонения сопротивления от заданного значения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

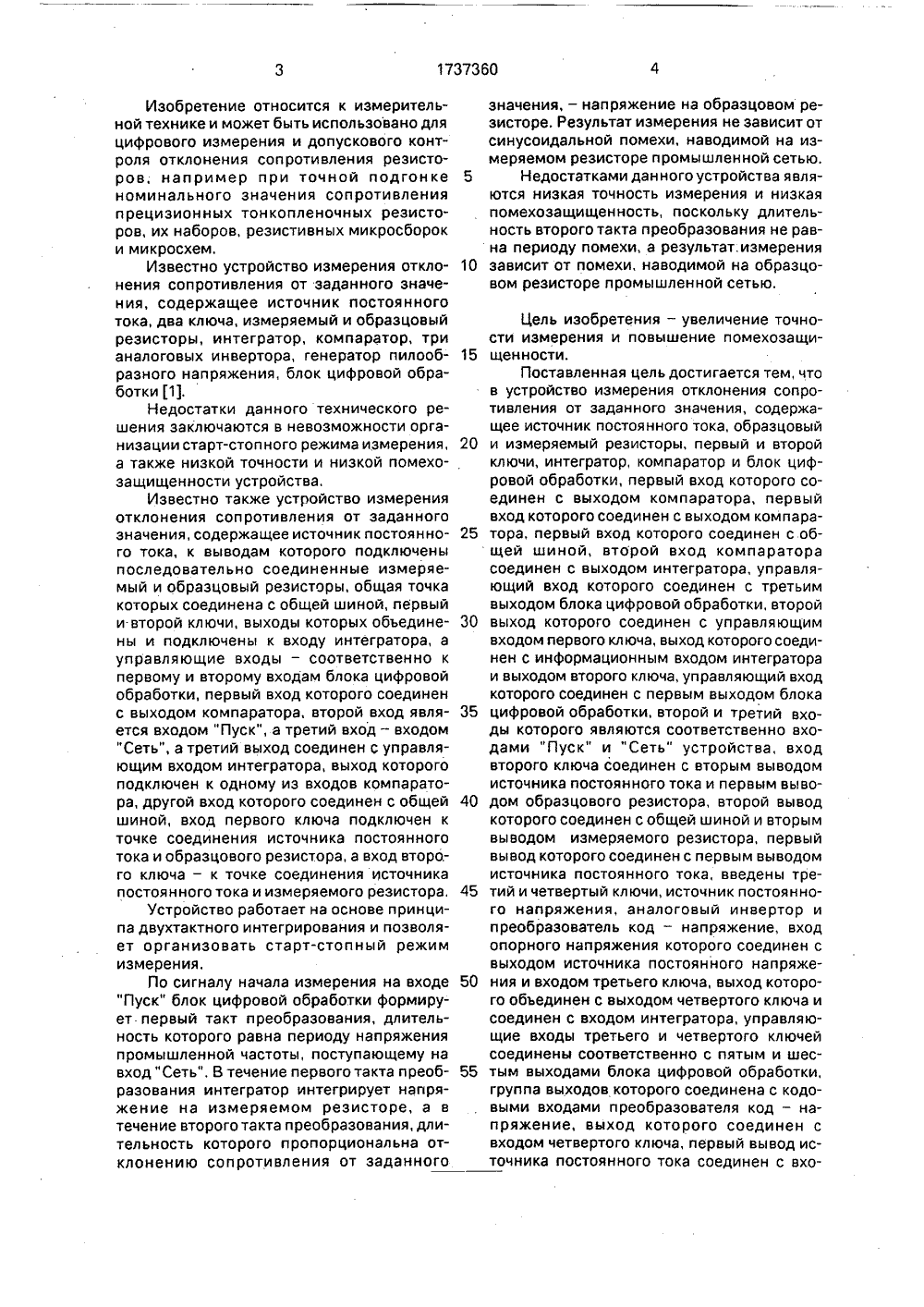

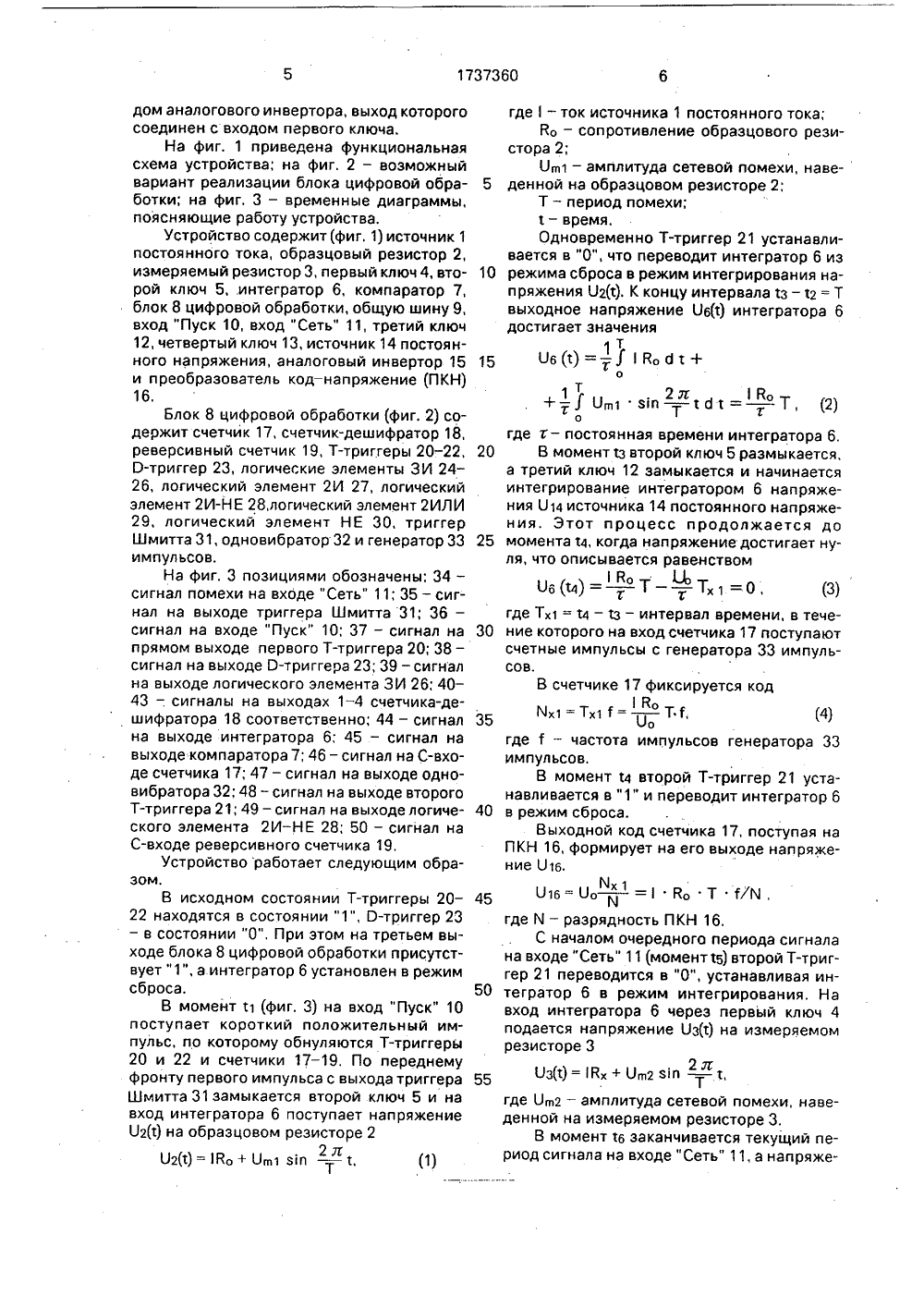

(19 01 й 27 0 ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИРИ ГКНТ СССР ПИСАНИЕ ИЗОБРЕТЕНАВТОРСКОМУ СВИДЕТЕЛЬСТВУ кии институтиборов ов, Вик,А, Ба М 1402698,96,ИЯ ОТКЛОНЕ- ЗАДАННОГО иэмерительльзовано для скового контния резисто 3(54) УСТРОЙСТВО ИЗМЕРЕННИЯ СОПРОТИВЛЕНИЯ ОТЗНАЧЕНИЯ(57) Изобретение относитсяной технике и может быть испцифрового измерения и допуроля отклонения сопротивл ров, например при точной под нального значения сопротивлен онных пленочных резисторов, резистивных микросборок и Целью изобретения является точности измерений и повыше защищенности. Устройство из клонения сопротивления от значения содержит источник 1 тока, измерительный 2 и образ зисторы, второй 5 и первый 4 к ратор 6, блок 8 цифровой о компаратор 7. В ведение в устро его 12 и четвертого 13 ключей, и постоянного напряжения, анал вертора 15 и преобразователя пряжение позволило исключи помехи, наводимые как на изме и на образцовом резисторах. 3 гонке номиия прециэиих наборов, микросхем, увеличение ние помехомерения отзаданного постОЯнНОГО цовыи 3 ре лючи, интегбработки и йство третьсточника 14 ОГОВОГО ИН код - нать сетевые ряемом, так ил,5 10 15 20 25 30 35 40 45 50 55 Изобретение относится к измерительной технике и может быть использовано для цифрового измерения и допускового контроля отклонения сопротивления резисторов, например при точной подгонке номинального значения сопротивления прецизионных тонкопленочных резисторов, их наборов, резистивных микросборок и микросхем.Известно устройство измерения отклонения сопротивления от заданного значения, содержащее источник постоянного тока, два ключа, измеряемый и образцовый резисторы, интегратор, компаратор, три аналоговых инвертора, генератор пилообразного напряжения, блок цифровой обработки 1.Недостатки данного технического решения заключаются в невозможности организации старт-стоп ного режима измерения, а также низкой точности и низкой помехозащищенности устройства,Известно также устройство измерения отклонения сопротивления от заданного значения, содержащее источник постоянного тока, к выводам которого подключены последовательно соединенные измеряемый и образцовый резисторы, общая точка которых соединена с общей шиной, первый и второй ключи, выходы которых объединены и подключены к входу интегратора, а управляющие входы - соответственно к первому и второму входам блока цифровой обработки, первый вход которого соединен с выходом компаратора, второй вход является входом "Пуск", а третий вход - входом "Сеть", а третий выход соединен с управляющим входом интегратора, выход которого подключен к одному из входов компаратора, другой вход которого соединен с общей шиной, вход первого ключа подключен к точке соединения источника постоянного тока и образцового резистора, а вход второ. - го ключа - к точке соединения источника постоянного тока и измеряемого резистора,Устройство работает на основе принципа двухтактного интегрирования и позволяет организовать старт-стопный режим измерения.По сигналу начала измерения на входе "Пуск" блок цифровой обработки формирует первый такт преобразования, длительность которого равна периоду напряжения промышленной частоты, поступающему на вход "Сеть". В течение первого такта и реобразования интегратор интегрирует напряжение на измеряемом резисторе, а в течение второго такта преобразования, длительностьь которого пропорциональна отклонению сопротивления от заданного значения, - напряжение на образцовом резисторе. Результат измерения не зависит от синусоидальной помехи, наводимой на измеряемом резисторе промышленной сетью.Недостатками данногоустройства являются низкая точность измерения и низкая помехозащищенность, поскольку длительность второго такта преобразования не равна периоду помехи, а результат. измерения зависит от помехи, наводимой на образцовом резисторе промышленной сетью. Цель изобретения - увеличение точности измерения и повышение помехозащищен ности.Поставленная цель достигается тем, что в устройство измерения отклонения сопротивления от заданного значения, содержащее источник постоянного тока, образцовый и измеряемый резисторы, первый и второй ключи, интегратор, компаратор и блок цифровой обработки, первый вход которого соединен с выходом компаратора, первый вход которого соединен с выходом компаратора, первый вход которого соединен с общей шиной, второй вход компаратора соединен с выходом интегратора, управляющий вход которого соединен с третьим выходом блока цифровой обработки, второй выход которого соединен с управляющим входом первого ключа, выход которого соединен с информационным входом интегратора и выходом второго ключа, управляющий вход которого соединен с первым выходом блока цифровой обработки, второй и третий входы которого являются соответственно входами "Пуск" и "Сеть" устройства, вход второго ключа соединен с вторым выводом источника постоянного тока и первым выводом образцового резистора, второй вывод которого соединен с общей шиной и вторым выводом измеряемого резистора, первый вывод которого соединен с первым выводом источника постоянного тока, введены третий и четвертый ключи, источник постоянного напряжения, аналоговый инвертор и преобразователь код - напряжение, вход опорного напряжения которого соединен с выходом источника постоянного напряжения и входом третьего ключа, выход которого объединен с выходом четвертого ключа и соединен с входом интегратора, управляющие входы третьего и четвертого ключей соединены соответственно с пятым и шестым выходами блока цифровой обработки, группа выходов которого соединена с кодовыми входами преобразователя код - напряжение, выход которого соединен с входом четвертого ключа, первый вывод источника постоянного тока соединен с входом аналогового инвертора, выход которого соединен с входом первого ключа.На фиг, 1 приведена функциональная схема устройства, на фиг, 2 - возможный вариант реализации блока цифровой обработки; на фиг. 3 - временные диаграммы, поясняющие работу устройства.Устройство содержит (фиг. 1) источник 1 постоянного тока, образцовый резистор 2, измеряемый резистор 3, первый ключ 4, второй ключ 5, .интегратор 6, компаратор 7, блок 8 цифровой обработки, общую шину 9, вход "Пуск 10, вход "Сеть" 11, третий ключ 12, четвертый ключ 13, источник 14 постоянного напряжения, аналоговый инвертор 15 и преобразователь код - напряжение (ПКН) 16.Блок 8 цифровой обработки (фиг. 2) содержит счетчик 17, счетчик-дешифратор 18, реверсивный счетчик 19, Т-триггеры 20 - 22, О-триггер 23, логические элементы ЗИ 24 - 26, логический элемент 2 И 27, логический элемент 2 И-НЕ 28,логический элемент 2 ИЛИ 29, логический элемент НЕ 30, триггер Шмитта 31, одновибратор 32 и генератор 33 импульсов,На фиг, 3 позициями обозначены: 34 - сигнал помехи на входе "Сеть" 11; 35 - сигнал на выходе триггера Шмитта 31; 36 - сигнал на входе "Пуск" 10; 37 - сигнал на прямом выходе первого Т-триггера 20; 38 - сигнал на выходе О-триггера 23; 39 - сигнал на выходе логического элемента ЗИ 26; 40 - 43 - сигналы на выходах 1 - 4 счетчика-дешифратора 18 соответственно; 44 - сигнал на выходе интегратора 6; 45 - сигнал на выходе компаратора 7; 46 - сигнал на С-входе счетчика 17; 47 - сигнал на выходе одновибратора 32; 48 - сигнал на выходе второго Т-триггера 21; 49 - сигнал на выходе логического элемента 2 И - НЕ 28; 50 - сигнал на С-входе реверсивного счетчика 19,Устройство работает следующим образом,В исходном состоянии Т-триггеры 20 - 22 находятся в состоянии "1", О-триггер 23 - в состоянии "0", При этом на третьем выходе блока 8 цифровой обработки присутствует "1", а интегратор 6 установлен в режим сброса.В момент 11(фиг. 3) на вход "Пуск" 10 поступает короткий положительный импульс, по которому обнуляются Т-триггеры 20 и 22 и счетчики 17 - 19, По переднему фронту первого импульса с выхода триггера Шмитта 31 замыкается второй ключ 5 и на вход интегратора 6 поступает напряжение О 2(с) на образцовом резисторе 2О 2(т) = Йо+ ОГп 1 3 П т, (1)2 УгТ где- ток источника 1 постоянного тока;йо - сопротивление образцового резистора 2;Оп 1 - амплитуда сетевой помехи, наве 5 денной на образцовом резисторе 2;Т - период помехи;1 - время.Одновременно Т-триггер 21 устанавливается в "0", что переводит интегратор 6 из10 режима сброса в режим интегрирования напряженияя 02(с). К концу интервала 1 з - (2 = Твыходное напряжение Оф) интегратора 6достигает значения1 тО 6 = - 3Во+о+уХ Ощ 1 3 и габт = Т (2)2 л ягде т - постоянная времени интегратора 6.20 В момент тз второй ключ 5 размыкается,а третий ключ 12 замыкается и начинаетсяинтегрирование интегратором 6 напряжения О 14 источника 14 постоянного напряжения. Этот процесс продолжается до25 момента т 4, когда напряжение достигает нуля, что описывается равенствомО-(т 4) = Т -- Т 1 =О, (3)Во ОоГдЕ Тх 1 = та - тЗ - ИНтЕреаЛ ВРЕМЕНИ, В ТЕЧЕ 30 ние которого на вход счетчика 17 поступаютсчетные импульсы с генератора 33 импульсов.В счетчике 17 фиксируется кодЯо35(4)Оогде 1 - частота импульсов генератора 33импульсов.В момент 14 второй Т-триггер 21 устанавливается в "1" и переводит интегратор 640 в режим сброса,Выходной код счетчика 17, поступая наПКН 16, формирует на его выходе напряжение О 16.х 145 О 16=Оо = Йо Т 1/М,йгде И - разрядность ПКН 16,С началом очередного периода сигналана входе "Сеть" 11 (момент 5) второй Т-триггер 21 переводится в "0", устанавливая ин 50 тегратор 6 в режим интегрирования. Навход интегратора 6 через первый ключ 4подается напряжение Оз(т) на измеряемомрезисторе 3Оз(1) - Кх + Ощ 2 з2где Оп 2 - амплитуда сетевой помехи, наведенной на измеряемом резисторе 3.В момент т 6 заканчивается текущий период сигнала на входе "Сеть" 11, а напряжение Оф) на выходе интегратора 6 достигаетзначенияОб (тб) - 3Вх б т + 2 т 1 ЗТ5+ - 3 Опг за тджх= "Т.В момент тб первый ключ 4 размыкается,а четвертый ключ 13 замыкается и интегратор 6 начинает интегрировать напряжение 10О 16 с ПКН 16. Этот процесс продолжаетсядо момента т 7, когда напряжение О 6(т) достигает нуля, что описывается равенствомО 6(т 7) Т -- Тх 2 = О,1 Вх 01 БХ 15где Тх = т 7 - Ь - интервал времени, в течениекоторого на реверсивный счетчик 19, работающий в режиме вычитания, поступаютсчетные импульсы.20Разрядность реверсивного счетчика 19 выбирается равной разрядности ПКН 16.При ВоВх в реверсивном счетчике 19 фиксируется кодМх=й-Тх 21 -25ВоПри ВоВо ТхТ и в некоторый момент времени реверсивный счетчик 19 обнуляется. Возникающий сигнал переноса переводит третий Т-триггер 22 в "1", а счет чик 19 - в режим сложения, и счет импульсов продолжается. К концу интервала Тх 2 в счетчике 19 фиксируется кодВ, - Во,.чВо 35 Таким образом, код М, зафиксированный в реверсивном счетчике 19, соответствует процентному отклонению сопротивления измеряемого резистора 3 от номинального значения, задаваемого сопротивлением Во 40 образцового резистора 2.Знак отклонения формируется третьимТ-триггером 22; при ВхВо после окончанияцикла измерения он остается в "0"; при Вх45Во - в "1",Результат измерения не подвержен влиянию сетевых помех, наводимых на измеряемом и образцовом резисторах. 50 Формула изобретения Устройство измерения отклонения сопротивления от заданного значения, содержащее источник постоянного тока, образцовый и измеряемый резисторы, первый и второй ключи, интегратор, компаратор и блок цифровой обработки, первый вход которого соединен с выходом компаратора, первый вход которого соединен с общей шиной, второй вход компаратора соединен с выходом интегратора, управляющий вход которого соединен с третьим выходом блока цифровой обработки, второй выходкоторогосоединен суправляющим входом первого ключа, выход которого соединен с информационным входом интегратора и выходом второго ключа, управляющий вход которого соединен с первым выходом блока цифровой обработки, второй и третий входы которого являются соответственно входами "Пуск" и "Сеть" устройства, информационный выход блока цифровой обработки является выходом устройства, вход второго ключа соединен с вторым выводом источника постоянного тока и первым выводом образцового резистора., второй вывод которого соединен с общей шиной и вторым выводом измеряемого резистора, первый вывод которого соединен с первым выводом источника постоянного тока, о т л и ч а ю щ е е с я тем, что, с целью увеличения точности измерений и повышения помехозащищенности, в него введены третий и четвертый ключи, источник постоянного напряжения, аналоговый инвертор и преобразователь. код - напряжение, вход опорного напряжения которого соединен с выходом источника постоянного напряжения и входом третьего ключа, выход которого объединен с выходом четвертого ключа и соединен с входом интегратора, управляющие входы третьего и четвертого ключей соединены соответственно с пятым и шестым выходами блока цифровой обработки, группа выходов которого соединена с кодовыми входами преобразователя код - напряжение, выход которого соединен с входом четвертого ключа, первый вывод источника постоянного тока соединен с входом аналогового инвертора, выход которого соединен с входом первого ключа,.5 Уг ув УУ вв оставитель В.Барановехред М,Моргентал Редактор М,Келемеш орректор О,Кундр Заказ 1888 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб., 4/5 зводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 1

СмотретьЗаявка

4786706, 25.01.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ЭЛЕКТРОННО-МЕХАНИЧЕСКИХ ПРИБОРОВ

АНДРЕЕВ АНАТОЛИЙ БОРИСОВИЧ, БАРАНОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, БАРАНОВ ВИКТОР АЛЕКСЕЕВИЧ, ЕРМОЛАЕВ НИКОЛАЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G01R 27/02

Метки: заданного, значения, отклонения, сопротивления

Опубликовано: 30.05.1992

Код ссылки

<a href="https://patents.su/5-1737360-ustrojjstvo-izmereniya-otkloneniya-soprotivleniya-ot-zadannogo-znacheniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство измерения отклонения сопротивления от заданного значения</a>

Предыдущий патент: Фазометр

Следующий патент: Устройство для измерения параметров сигнала, отраженного от входа свч-элемента

Случайный патент: Кошельковый невод