Устройство для контроля времени выключения тиристоров

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

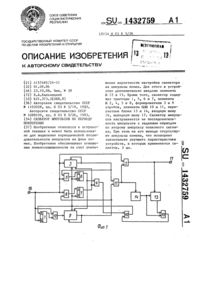

Цель изобретения - повышение надежности устройства и расширение области его использования.Поставленная цель достигается тем, что в устройство контроля времени выключения тиристоров введены триггер; два элемента задержки, два элемента совпадения, две дифференцирующие цепи, два блока измерения длительности импульсов, триггер "защелка" и задатчик порогового значения, а в качестве датчика состояния тиристоров использован преобразователь обратного запирающего напряжения в прямоугольные импульсы, причем вход преобразователя обратного запирающего напряжения в прямоугольные импульсы предназначен для подключения параллельно тиристорам, а выход под ключен к. входам первого и второго элементов задержки и к счетному входу триггера, прямой выход которого под. ключен к первому входу первого элемента совпадения. и к входу первой дифференцирующей цепи, а инверсный выход триггера подключен к первому входу второго элемента совпадения, к входу второй дифференцирующей цепи и к входу триггера "защелка",выходы 30 первого и второго элементов задержки подключены к вторым входам, соответственно, первого и второго элементов совпадения, выходы которых подключе-: ны к управляющим входам соответствен- .35 но первого и второго блоков измерения длительности импульсов, входы сброса которых подключены соответст- . венно к выходам первой и второй дифФеренцирующих цепей, а выходы перво го и второго блоков измерения длительности импульсов и прямой выход триггера "защелка" подключены к пер вому входу элемента сравнения, второй вход которого через задатчик порого вого значения подключен к инверсному выходу триггера "защелка", а выход элемента сравнения подключен к входу исполнительного элемента.На фиг 1 представлено предлагае", 50 мое устройство контроля времени выключения тиристоров; на, фиг. 2- временные диаграммы выходных сигна" .лов элементов схемы с соответствующими цифровыми индексами. 55Устройство предназначено для контроля схемного времени выключения силовых тиристоров, то есть времени, в течение которого тиристоры находятся под обратным запирающим напряжением и может быть использованонапример, в параллельном инверторе 1 тока.Преобразователь 2 обратного запирающего напряжения в прямоугольные импульсы, являющийся датчиком состояния тиристоров, осуществляет ог" раничение величины напряжения, гальваническую развязку с силовыми цепями инвертора и формирование прямоугольных импульсов, равных по.длительности. соответствующим интерваламвремени пребывания. тиристорных групппод обратным отрицательным напряжением.Коммутатор 3 каналов измерения предназначен для обеспечения очередности включения каждого из двух каналов измерения длительности импульсов и для формирования сигнала сброса результата измерения. Он содержиттриггер 6 со счетным входом, управляющий двумя элементами ) и 1 О совпадения, На вторые входы элементов совпадения поступают импульсы, длительность которых необходимо измерить.Изменение состояния триггера происхо-:, дит каждый раз по спаду входного им-пульса. Элементы 4 и 5 задержки син-" хронизируют появление импульсов на входах элементов совпадения, компенсируя задержку срабатывания триггераво времени. Сигнал сброса результата измерений формируется дифференцирующими цепями 8 и 9.Блок 11 измерения и памяти длитель-,ности импульсов содержит два идентичных блока 12 и 13 для измерения дли-, тельности импульсов,. в качестве ко" тооых могут быть использованы неин"вертирующие интеграторы., выполненныена операциожных усилителях с высоким, входным сопротивлением и содержащие разрядные ключи для сброса резуль" тата интегрирования. Диодные ключи 14 и 15 предотвращают взаимное шунтирование выходных цепей интеграторов.Блок 21 Формирования сигнала управления и защиты осуществляет сравнение измеренного значения времени выключения, представленного в качестве выходного напряжения интеграторов, с допустимым пороговым значением данного параметра, .устанавливаемымО задатчиком 19 порогового значенияи в случае уменьшения напряжения интеграторов до уровня ниже порогового,выдает сигнал на исполнительный элемент 20. В качестве элемента 17 срав 5нения может быть использован компаратор.Триггер 16 однократного срабатывания типа "защелка" служит для блокирования устройства сравнения и задатчика порогового значения с цельюпредотвращения срабатывания исполнительного устройства до включенияинвертора и появления импульсов навыходе преобразователя 2. Он изменя-ет свое состояние на разрешающеетолько после того, как проинтегрирован второй по счету импульс. Послесрабатывания триггер сохраняет свое 20состояние неизменным. При этом диод"ный.ключ 18 исключает влияние триггера "защелка" на входные цепи устройства сравнения,Использование выходного сигналатриггера "защелка" в качестве сигнала запрета для задатчика 19 допустимого порогового значения позволяет.исключить появление выбросов напряже"ния на выходе устройства сравнения 30при включении источника питания,Устройство работает следующим об"разом.После подключения устройства к.источнику питания при неработающем 35параллельном инверторе тока 1. триггеры 6 и 16 устанавливаются в состоя-.ние с логической единицей на верхних(фиг. 1) выходах. Продифференцированный цепью 8 фронт выходного им- : 40пульса триггера 6 открывает разрядныйключ интегратора 12, разряжая егозарядную емкость. Триггер 16 устанавли"вает на сигнальном входе элемента17 сравнения уровень напряжения логи 45ческой единицы и отключает задатчиклогическим нулем. На всех остальныхвходах и выходах элементов схемы присутствует логический ноль.После запуска параллельного ин- . 50вертора 1 тока на входе преобразователя 2 обратного запирающего напряженияпоявляется напряжение, снимаемое с.мо"ста инвертора. Это напряжение преобразуется в прямоугольные импульсы постоянной амплитуды, длительность. ка" .. торых равна времени пребывания тирис-,торов под обратным напряжением, которые поступают на счетный вход триггера 6 и через элементы 4 и 5 задержки - на входы двухвходовых элементов 7 и 10 совпаденияУсловие совпадения при поступлении первого импульса выполняется навходах элемента 7, следовательно, на выходе элемента 7 появится высокий логический уровень напряжения, который поступитна вход интегратора 12. Нацнется процесс заряда емкости интегратора 12 и на выходе его появится напряжение, которое с достаточной сте-. пенью точности может быть записано, как Б, =1 с С , где 1 с - коэффициент, определяемйй постоянной времени интегратора;- время действия импульса, равное времени выключения группы тиристоров.По спаду первого входного импульса триггер 6 изменит свое состояние.На верхнем по схеме выходе триггера появится логический ноль, на нижнем - логическая единица, Под воздействием продифференцированного цепью 9 фронта выходного импульса (с нижнего по схеме выхода триггера 6) откроется разрядный ключ интегратора 13 и разрядится его зарядная емкость, Интегратор 13 готов .к интегрированию очередного импульсапоступившего на его вход с выхода блока 2 через элемент. 5 задержки и элемент 1 О совпадения.В результате .интегрирования на выходе интегратора появится напряже- ние 0 =Ь е, зависящее,. от времени выключения очередной группы тиристоров.Затем по спаду второго входного. импульса произойдет изменение состояния триггеров, а по спаду его выходного импульса на нижнем по схеме выхода - изменение состояния триггера 16. На верхнем по схеме выходе триггера 6 установится логическая единица, на нижнем " логический ноль.Триггер 16 придет в состояние, соответствующее логическому нулю на верхнем по схеме выходе,единице на нижнем и установится на "защелку", В результате этого снимается блокировка с элемента. 17 сравнения и происходит включение задатчика 19 допустимого,порогового значения, т.е. элемент сравнения начинает осуществлять операцию сравнения напряжений, 1725316поступающих на его выходы. При этомреализуется операция вычитания=11( в-зт.е. измеренное значение схемного5 времени выключения сравнивается с допустимым значением данного параметра и происходит срабатывание исполнительного устройства, Кроме того, 10 выходной сигнал. устройства 0 И ),Э практически линейно зависящий от времени выключения тиристоров, в дальнейшем может быть использован в системе управления и регулирования 15 инвертором (на фиг, 1 не показана), что, в конечном счете, позволяет не допускать режима опрокидывания инвер-, тора при приближении времени выключения тиристоров к предельно допу- . 20 стимому его значению.Технико-экономическая эффектив" ность устройства обеспечивается полу- чением непрерывного во времени. линейно 25 изменяющегося сигнала контроля времени выключения тиристорных групп с возможностью использования его. для уп-. равления и регулирования режимом рабо", ты преобразовательных устройств, в ЗО частности, параллельных инверторов тока, что в конечном итоге позволяет избежать аварийных режимов опрокиды" вания и повысить надежность работы преобразователей в целом. 33формула изобретенияУстройство для контроля времени выключения тиристоров, содержащее40 датчик состояния тиристоров, элемент . сравнения и исполнительный элемент, о т л и ч а ю щ е е с я тем, юо, с целью повышения надежности и расширения области использования, в него 4 введены триггер, два элемента задержки, два элемента совпадения, две дифференцирующие цепи, два блока измерения длительности импульсов, триггерЗащелка и задатчик порогового значения, а в качестве датчика состояния тиристоров использован преобразователь обратного запирающего напря" жения в. прямоугольные импульсы, причем вход преобразователя обратного запирающего напряжения в прямоугольные импульсы предназначен для под. ключения параллельно тиристорам, а выход подключен к входам первого и второго элементов задержки,. и к счетному входу триггера, прямой выход которого подключен к первому входу первого элемента совпадения и к вхо" ду первой дифференцирующей цепи, а инверсный выход триггера подключен к первому входу второго элемента совпадения, к входу второй дифференцирующей цепи и к входу триггера "За" щелка", выходы первого и второго элементов задержки подключены ко вторым . входам соответственно первого и вто" рого элементов совпадения, выходы которых подключены к управляющим вхо" дам, соответственно, первого и второго блоков измерения длительности импульсов, входы сброса которых под" ключены, соответственно, к выходам первой и второй дифференцирующих це" пей, а выходы первого и второго блоков, измерения длительности импульсов и прямой выход триггера "защелка" подключены к первому входу элемента срав нения, инверсный выход триггера "эа" щелка" соединен с управляющим входом задатчика порогового значения, вйход которого соединен с вторым входом эле" мента сравнения, а выход элементасравнения подключен к .входу испол нительного элемента.-35Рауш изводственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,10 Заказ 1181ВЧИИПИ Госу Тираж твенного комитет 113035, Москва, ин.Корр Подписноеенням и открытиям .при ГКНТ СССР , кая наб., д. 4/5

СмотретьЗаявка

4812310, 02.03.1990

СТАХАНОВСКИЙ ФИЛИАЛ КОММУНАРСКОГО ГОРНО-МЕТАЛЛУРГИЧЕСКОГО ИНСТИТУТА

ГЛЕБИН АНАТОЛИЙ ГЕОРГИЕВИЧ, БОРИСОВ ПЕТР НИКОЛАЕВИЧ

МПК / Метки

МПК: H02H 7/12

Метки: времени, выключения, тиристоров

Опубликовано: 07.04.1992

Код ссылки

<a href="https://patents.su/5-1725316-ustrojjstvo-dlya-kontrolya-vremeni-vyklyucheniya-tiristorov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля времени выключения тиристоров</a>

Предыдущий патент: Устройство для защиты тиристорного импульсного преобразователя постоянного напряжения от коммутационных перегрузок

Следующий патент: Магнитопровод электрической машины

Случайный патент: Способ обратного цементирования обсадных колонн