Устройство для формирования контрольных тестов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1605208

Авторы: Бельских, Грабовский, Михайлович, Романов, Фомичев

Текст

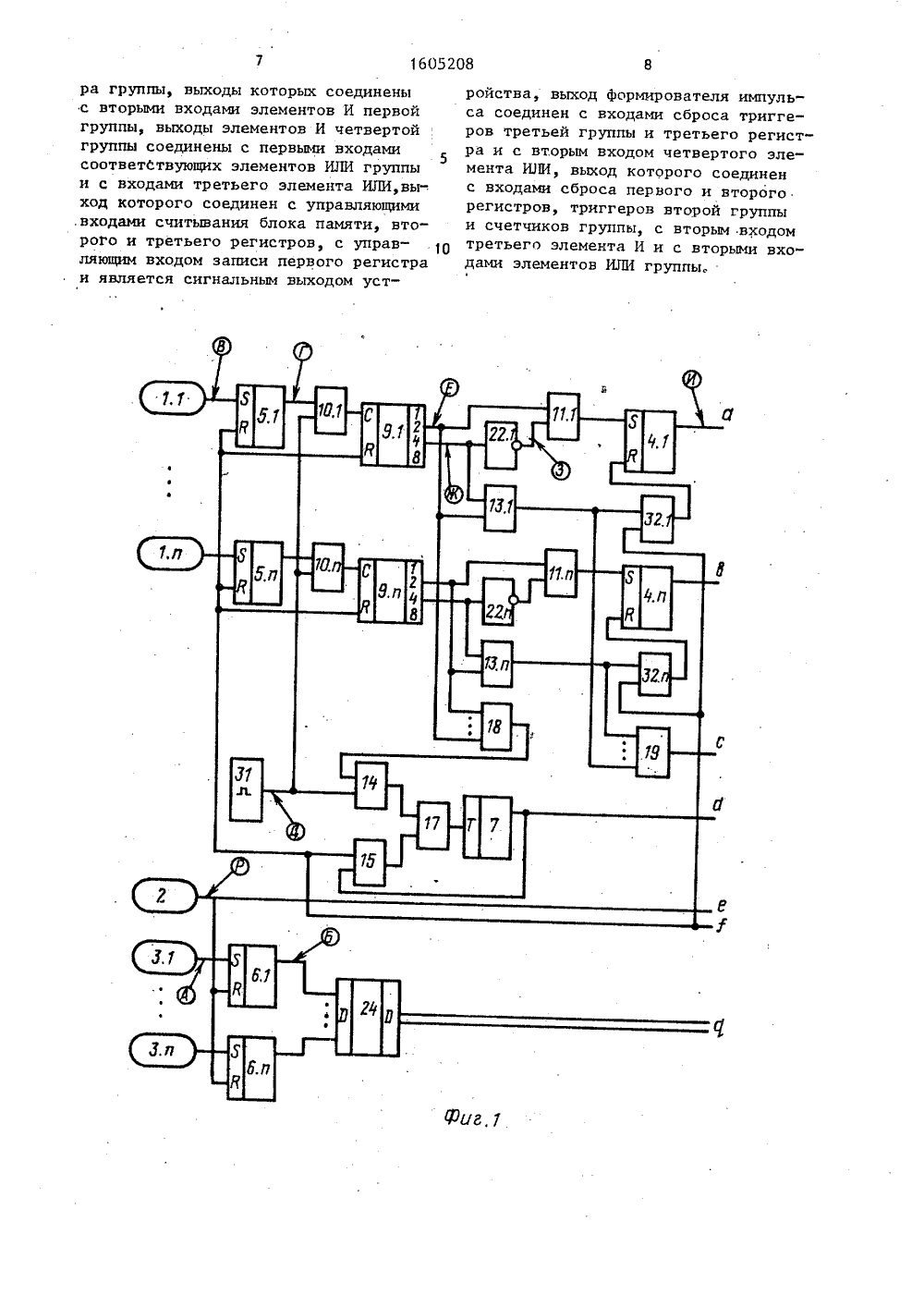

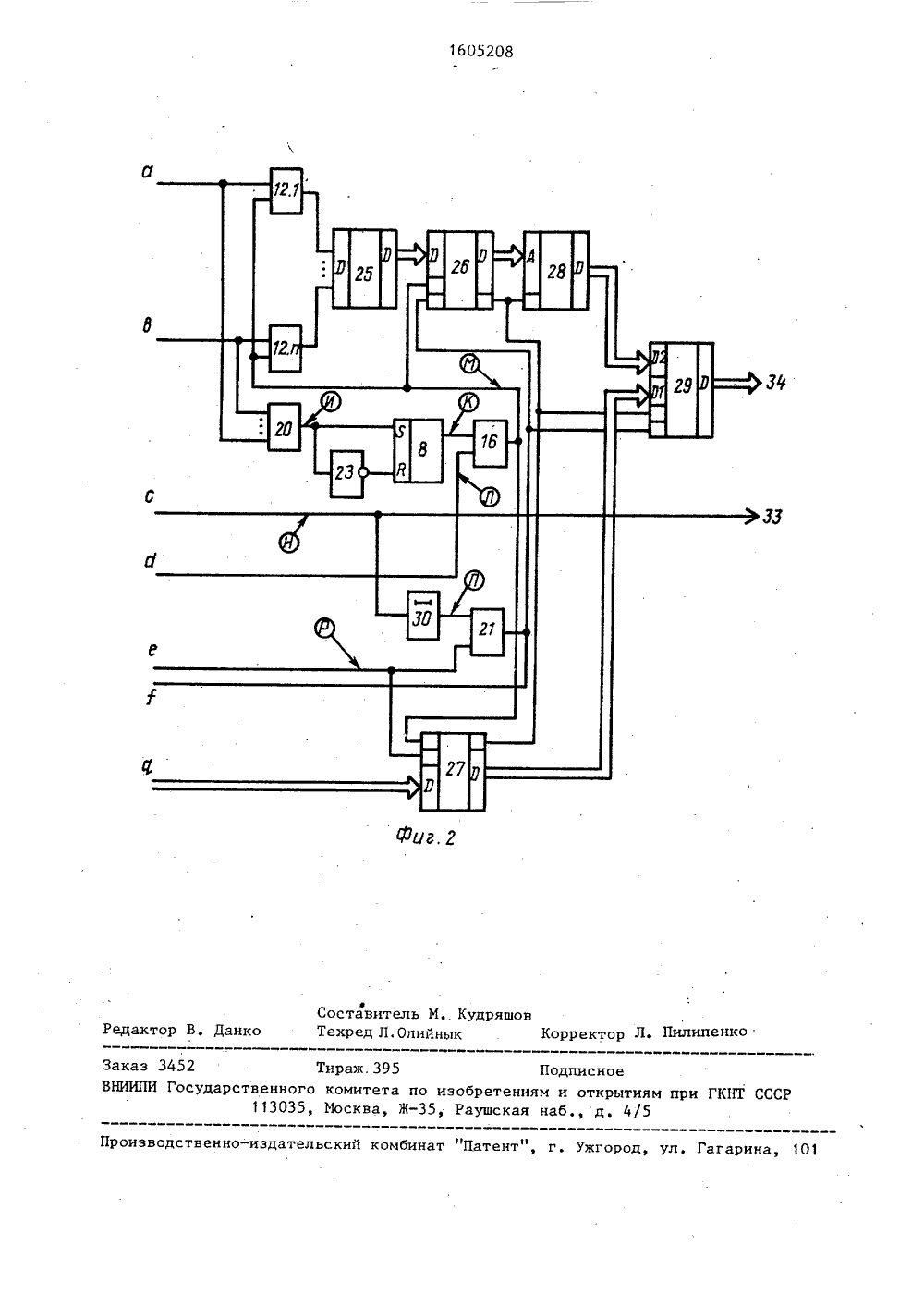

После включения устройства оно ус"танавливается в исходное состояниеформирователем 2, который устанавливает в нулевое состояние триггеры 6,обнуляет регистр 27, через элементИЛИ 21 обнуляет регистры 26 и 29,триггеры 5, счетчики 9 группы и через элементы ИЛИ 32 - триггеры 4.В исходном состоянии на прямом выходе триггера 7 устанавливается низкий потенциал (логический "0").Еслипо каким-либо причинам после включения устройства на вьгходе триггера 7будет высокий потенциал (логическая1"), то импульс "Сброс", пройдя через открытьп элемент И 15 и элементИЛИ 17, поступит на счетный вход триггера 7 и установит его в исходное состояние. 20Весь цикл Формирования устройствомтестового сообщения можно условно разделить на два этапа: первый - формирование кода адреса теста записанно:го в блоке 28 памяти, и кода адреса 25контролируемого объекта; второй -выборка из блока 28 памяти кода теста, запись в регистр 29 кода тестаи кода адреса объекта, выдача тесто,вого.сообщения.30Устройство может работать в двухрежимах: первый - тестирование одного объекта; второй - тестированиеобъектов в любой последовательности.В первом режиме оператор нажимает клавишу соответствующего Формирователя3, а затем в необходимой последовательности клавиши формирователей 1.Второй режим аналогичен первому, только при переходе к работе с новым объектом необходимо осуществлять сбростриггеров 6 группы нажатием клавишиФормирователя 2.В процессе работы, при необходимости выдачи на объект тестового сообщения, оператор нажимает клавишусоответствующего формирователя 3 иклавишу соответствующего Формирователя 1.Импульс с выхода соответствующегоформирователя 3 поступает на устано 50вочньп "вход соответствующего триггера 6, устанавливая его в состояние,при котором на его прямом выходе появится высокий потенциал. Шифраторпреобразует код, поступающий на его55входы с выходов триггеров 6, в кодадреса контролируемого объекта, который поступает на информационные входырегистра 27,Импульс с выхода соответствующегоформирователя 1 поступает на установочньп вход триггера 5, устанавливаяего в состояние, при котором на егопрямом выходе появится высокий потенциал, которым открывается соответствующий элемент И 10,Тактовые импульсы с выхода генератора 31 импульсов поступают через соответствующий элемент И 10 на счетныйвход соответствующего счетчика 9. Вмомент поступления второго тактовогоимпульса на счетный вход счетчика 9на его выходе "2" появится импульс,который через элемент И 11.1 поступаетна установочньп вход триггера 4.1, устанавливая его в единичное состояние.Элемент И 11.1 открыт высоким потенциалом, поступающим на него с выходаинвертора 22.1, на вход которого подается низкий потенциал с выхода "4"счетчика 9.1.Импульс с выхода триггера 4.1 через элемент ИЛИ 20 устанавливает вединичное состояние триггер 8, который открывает по одному входу элементИ 16, на другой вход которого поступают импульсы с выхода триггера 7.Первый импульс с выхода триггера 7,пройдя элемент И 16, поступает на входы элементов И 12, но проходит толькочерез открытый элемент И 12.1 и поступает на первый вход шифратора 25, наостальных входах шифратора 25 логические "0", На выходах шифратора 25 формируется код адреса теста, записанногов блоке 28 памяти. Кроме того, по импульсу с выхода элемента И 16 осуществляется запись кода адреса теста икода адреса контролируемого объектас выхода шифраторов 25 и 24 в соответствующие регистры 26 и 27При поступлении четвертого тактового импульса на счетный вход счетчика9,1 с генератора 31 на выходе "4"счетчика 9,1 Формируется импульс, покоторому закрывается элемент И 11.1 иоткрывается по одному входу элементИ 13.1,С поступлением шестого тактовогоимпульса на счетный вход счетчика 9.1на его выходе "2" появляется второйимпульс, которым сбрасывается черезэлемент И 13,1 и элемент ИЛИ 32.1триггер 4,1 и триггер 8, запускаетсячерез элемент ИЛИ 19 элемент 30 задержки, осуществляется считывание изблока 28 памяти кода теста по соот 1605208ветствующему адресу и запись в регистр 29 кода теста и кода адреса контролируемого объекта.1Код тестового сообщения с информа 5 ционных выходов выкодного регистра 29 по информационной шине поступает на выход 34 устройства. С выхода 34 тестовое сообщение поступает в каналообразующее устройство, прием сообщения синхронизируется импульсом, поступающим с выхода 33 устройства.Следует отметить, что информационные выходы регистра 29 не блокируются при записи в него информации, а следовательно, уже при записи сообщения в регистр 29 на его выходах будет присутствовать информация.После окончания процесса перезаписи кодов в регистр 29 и выдачи со общения импульс с выхода элемента 30 задержки проходит через элемент ИЛИ 21 и устанавливает соответствующие элементы устройства в исходное состояние. Устройство готово к выдаче но вого тестового сообщения, но по адресу объекта, который был набран. Формула изобретения30Устройство для Формирования контрольных тестов, содержащее первую и вторую группы Формирователей импульсов, Формирователь импульсов, первую группу триггеров, два триггера, три группы элементов И, первый элемент И, пять элементов ИЛИ, блок памяти, первый регистр, элемент задержки и генератор импульсов, выход которого соединен с первым входом первого элемен та И, выход первого элемента ИЛИ соединен со счетным входом первого триггера, выходы элементов И первой группы соединены с единичными входами триггеров первой группы, прямые выхо ды которых соединены с первыми входами элементов И второй группы, выход второго элемента ИЛИ соединен с единичным входом второго триггера, выход третьего элемента ИЛИ соединен с входом элемента задержки, выход которого соединен с первым входом четвертого элемента ИЛИинформационные выходы блока памяти соединены с первой группой информационных входов первого регистра, информационные вьгходы которого являются информационными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения Функциональной надежности устройства за счетснижения вероятности ложной выдачисообщения на объект, в него введенывторая и третья группы триггеров,группа счетчиков, четвертая группаэлементов И, второй и третий элементы И, группа инверторов, инвертор,первый и второй шифраторы, второй итретий регистры и группа элементовИЛИ, выходы которых соединены соответственно с входами сброса триггеровпервой группы, прямые выходы которыхсоединены с входами второго элементаИЛИ, выход которого через инверторсоединен с входом сброса второго триггера, прямой выход которого соединен спервым входом второго элемента И, выход которого соединен с управляющими1 входами записи второго и третьего регистров и с вторыми входами элементовИ второй группы, выходы которых соединены с входами первого шифратора,выходы которого соединены с информационными входами второго регистра, информационные выходы которого соедине.ны с адресными входами блока памяти,выходы Формирователей импульсов первой и второй групп соединены соответственно с единичными входами триггероввторой и третьей групп, прямые выходытриггеров третьей группы соединены свходами второго шифратора, выходы которого соединены с информационнымивходами третьего регистра, выходы которого соединены с первой группой информационных входов первого регистра,прямые выходы триггеров второй группысоединены с первыми входами элементовИ третьей группы, выходы которых соединены со счетными входами соответствующих счетчиков, группы, первые информационные выходы которых соединеныс первыми входами элементов И первойи четвертой групп и с входами пятогоэлемента ИЛИ, выход которого соединенс вторым входом первого элемента И,выход которого соединен с первым входом первого элемента ИЛИ, второй входкоторого соединен с выходом третьегоэлемента И, первый вход которого соединен с выходом первого триггера и свторым входом второго элемента И, выход генератора импульсов соединен свторыми входами элементов И третьейгруппы, вторые информационные выходысчетчиков группы соединены с вторымивходами соответствующих элементов Ичетвертой группы и с входами инверто 1 б 05208 8ра группы, выходы которых соединеныс вторыми входами элементов И первойгруппы, выходы элементов И четвертойгруппы соединены с первыми входамисоответСтвующих элементов ИЛИ группыи с входами третьего элемента ИЛИ,выход которого соединен с управляющими,входами считывания блока памяти, второго и третьего регистров, с управляющим входом записи первого регистраи является сигнальным выходом устройства, выход Формирователя импульса соединен с входами сброса триггеров третьей группы и третьего регистра и с вторым входом четвертого элемента ИЛИ, выход которого соединенс входами сброса первого и второгорегистров, триггеров второй группыи счетчиков группы, с вторым .входомтретьего элемента И и с вторыми входами элементов ИЛИ группы,1 б 05208 г,Г Составитель М Кудряш Техред Л.Олийнык рректор Л. Пилипенко нк едактор В оизводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 10 аказ 3452НИИПИ Госуда Тираж.395венного комитета по113035, Москва, Жэобрете Раушск Подписноеям и открытиям при ГКНТ СССнаб., д, 4/5

СмотретьЗаявка

4456332, 19.07.1988

ПРЕДПРИЯТИЕ ПЯ А-3706

ФОМИЧЕВ ОЛЕГ КИМОВИЧ, ГРАБОВСКИЙ ОЛЕГ БОРИСОВИЧ, МИХАЙЛОВИЧ МАРИНА ВИКТОРОВНА, РОМАНОВ АНАТОЛИЙ НИКОЛАЕВИЧ, БЕЛЬСКИХ ЮРИЙ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 11/26, G09G 1/00

Метки: контрольных, тестов, формирования

Опубликовано: 07.11.1990

Код ссылки

<a href="https://patents.su/5-1605208-ustrojjstvo-dlya-formirovaniya-kontrolnykh-testov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования контрольных тестов</a>

Предыдущий патент: Устройство для контроля параметров линейных фазированных антенных решеток

Следующий патент: Оптическая система для электрофотографических аппаратов

Случайный патент: Способ очистки масляных фракций нефти