Демодулятор дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

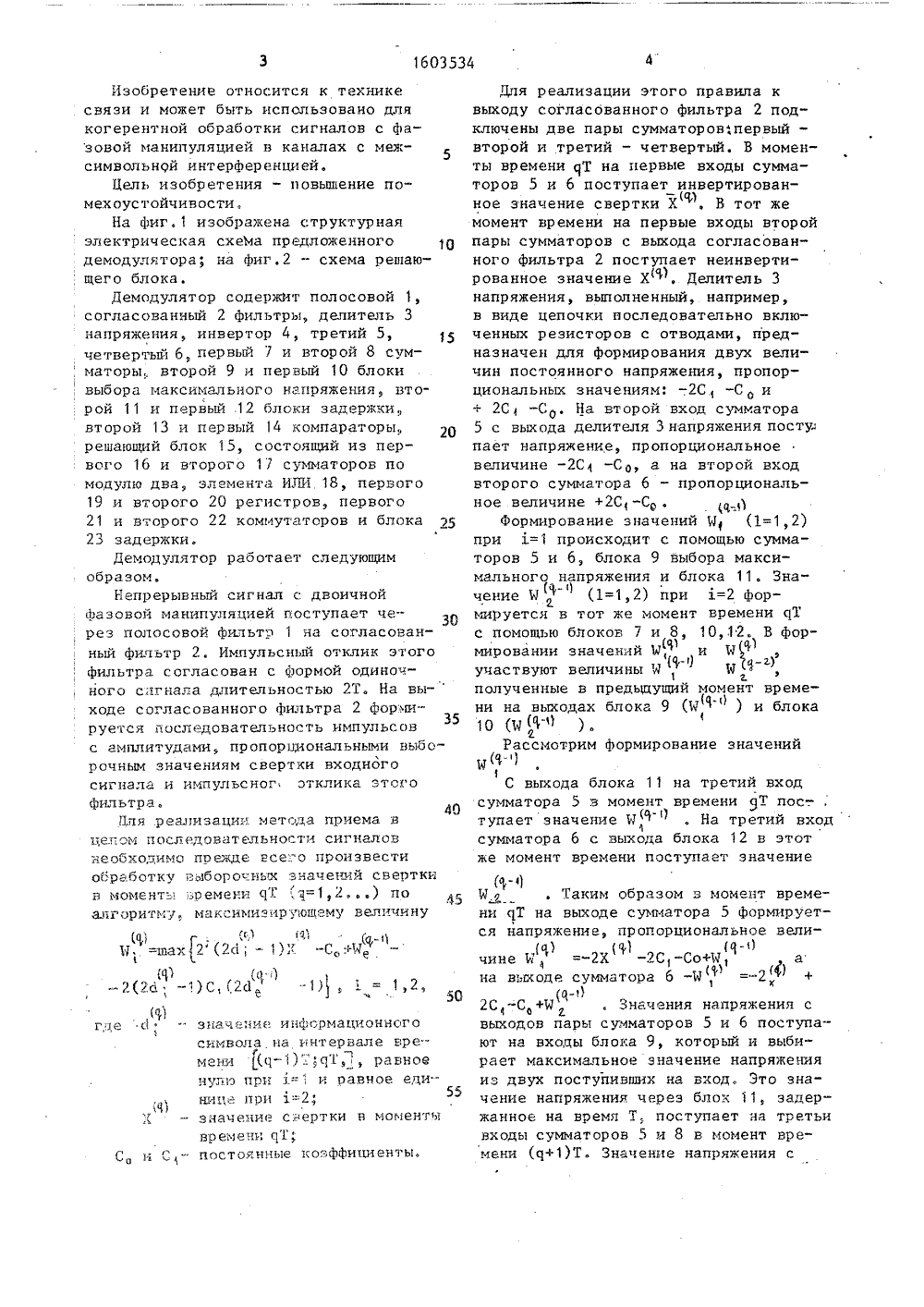

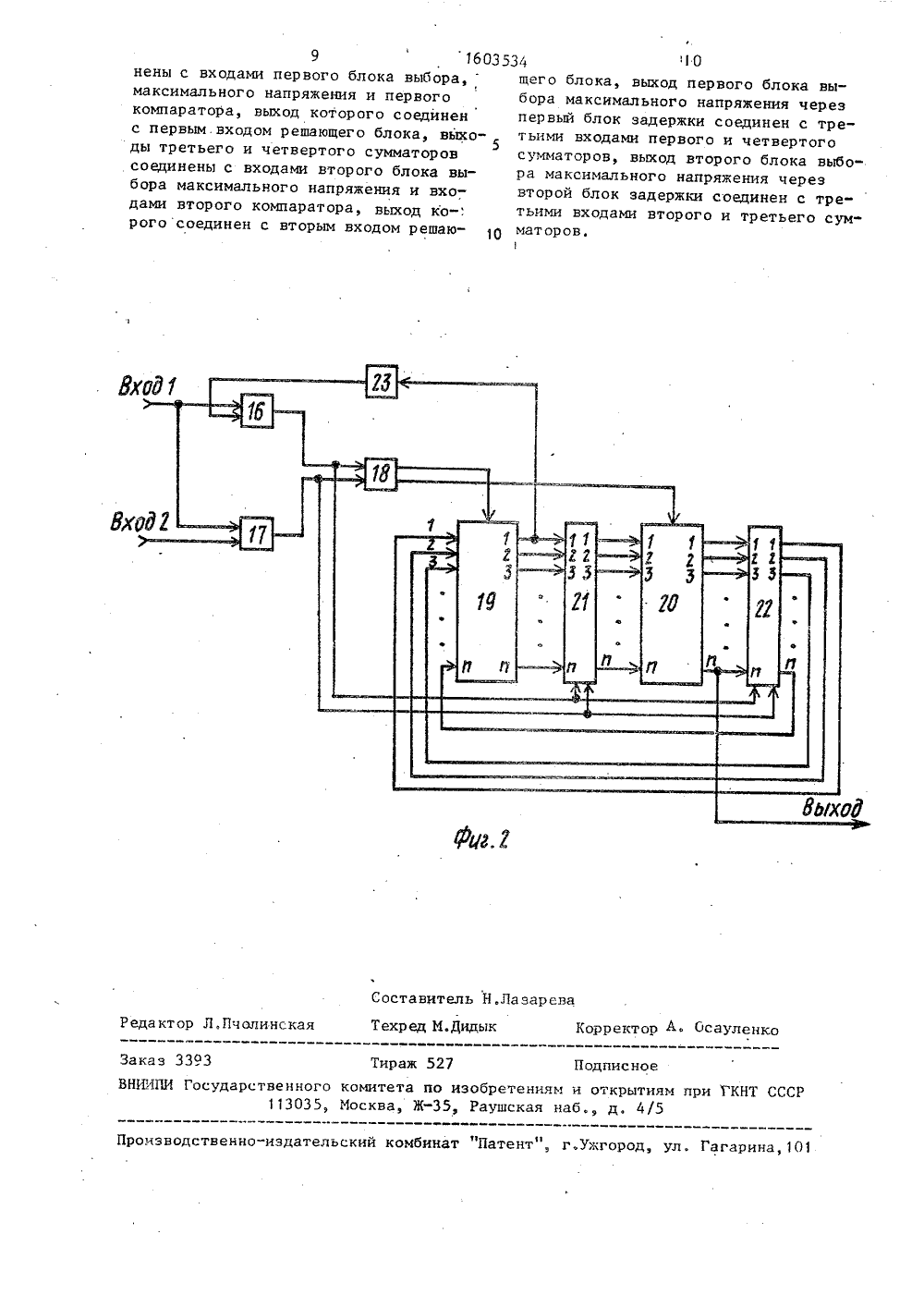

ц)5 Н 04 1 27/ НИ САНИЕ Мд 40политехничининаВ.К.Ядыкин8.8)етельство1 27/20,к ССР982,СКРЕТНЫХ СИГНАЛОВ носится к технике использовано дп ки сигнал каналах с азомей ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЩРЫГИЯПРИ ГКНТ СССР(57) Изобретениесвязи и может быткогерентной обрабвой манипуляцией вольной интерференцией. Цель изобретения - повышение помехоустойчивости, Демодулятор содержит полосовой Фильтрсогласованный Фильтр 2, делитель 3 напряжения, инвертор 4,сумматоры 5-8, блоки 9 и 10 выбора максимального напряжения, блоки задержки 11 и 12 компараторы 13 и 14 и решающий блок 15. Повышение помехоустойчивости приема сигналов с фазовой манипуля" цией в условиях межсимвольной интерференции достигается за счет использования в устройстве метода приема сигналов в целом. Дана ил.выполнения решающего блока 15. 2 ил.С, и значение информационног о символа. на интервале времени (41-"1)1 с)Т 44 равное нулю при з) и равное еди 21значение свертки в моменты времени с)Тпостоянные коэффициенты. Изобретение относится к технике связи и может быть использовано для когерентной обработки сигналов с Фазовой манипуляцией в каналах с меж 5 символьной интерференцией.Цель изобретения - повышение помехоустойчивости.На Фиг.1 изображена структурная электрическая схема предложенного демодулятора; на фиг.2 - схема решающего блока.Демодулятор содержит полосовой 1, согласованный 2 фильтры, делитель 3 напряжения, инвертор 4, третий 5, четвертый 6, первый 7 и второй 8 сумматоры второй 9 и первый 10 блоки выбора максимального напряжения, второй 11 и первый 1.2 блоки задержки второй 13 и первый )4 компараторы решающий блок 15, состоящий из первого 16 и второго 17 сумматоров по модулю два, элемента И)П 1 18, первого 19 и второго 20 регистров, первого 21 и второго 22 коммутаторов и блока 23 задержки.Демодулятор работает следующим образом.Непрерывный сигнал с двоичной Фазовой манипуляцией поступает через полосовой Фильтр 1 на согласованный фильтр 2. Импульсный отклик этого фильтра согласован с Формой одиночного сигнала длительностью 2 Т. На выходе согласованного фильтра 2 форми 35 руется последовательность импульсов с амплитудами, пропорщлональными выборочным значениям свертки входного сигнала и импульсног отклика этого Фильтра.40Бля реализации. метода приема в цепом последовательно т;л сигналов необходимо прежде все:.о произвести обработку выборо ных значеилй свертки Б мом нт." эремени Я - , 1=1 у 2 е в в) по,5 алгоритму 4 максимизируюшему величинуИ =шах 2" (2 а; - 1)Х -С,+Я-2(2 а -1) С, (2 йДля реализации этого правила к выходу согласованного фильтра 2 подключены две пары сумматоров,первый- второй и третий - четвертый. В моменты времени 4 Т на первые входы сумматоров 5 и 6 поступает инвертирован - (ное значение свертки Х . В тот же момент времени на первые входы второй пары сумма т ор ов с выхода с оглас ованного фильтра 2 поступает неинвертированное значение Х. Делитель 3 напряжения, выполненный, например, в виде цепочки последовательно включенных резисторов с отводами, предназначен для формирования двух величин постоянного напряжения, пропорциональных значениям: в ,2 С, -Си + 2 С 4 -СО. На второй вход сумматора 5 с выхода делителя 3 напряжения посту. пает напряжение, пропорциональное величине -2 С 4 -Со, а на второй вход второго сумматора 6 - пропорциональное величине +2 С 4 С .Формирование значений И (1=1,2) при =1 происходит с помощью сумматоров 5 и 6, блока 9 выбора максимального напряжения и блока 11. Значение и " (1=1,2) при х=2 Формируется в тот же момент времени )Т с помощью блоков 7 и 8, 10,12. В Формировании значений )4), и И, (М (а - а) участвуют величины И, Ыполученные в предыдущий момент времени на выходах блока 9 (Ы) и блока 10 (Ч (" ) ) .2Рассмотрим Формирование значений у И)1С выхода блока 11 на третий вход сумматора 5 в момент времени уТ пос-. тупает значение И" ) . На третий вход сумматора 6 с выхода блока 12 в этот же момент времени поступает значение(- 41Ыд . Таким образом в момент времени пТ на выходе сумлатора 5 Формируется напряжение, пропорциональное велид),и-чине Ы, =-2 Х -2 С 1-Со+Я, а(р)2 С,-С +1) . Значения напряжения с выходов пары сумматоров 5 и 6 поступают на входы блока 9, который и выбирает максимальное значение напряжееия из двух поступивших на вход, Это значение напряжения через блок 11, задержанное на время Т поступает на третьи входы сумматоров 5 и 8 в момент времени (Ч+1)Т. Значение напряжения свыходов сумматоров 5 и 6 поступают,кроме того, на входы компаратора 13,на выходе которого Формируется напряжение, соответствующее либо "0", либо"1". При этом "0" соответствует ситу 5ации, когда значение напряжения навыходе сумматора 5 больше значениянапряжения на выходе сумматора 6.Аналогично Формируется значениеИ . На второй вход сумматора 8 с2выхода делителя 3 поступает напряжение, пропорциональное величине +2 С-С, а на второй вход сумматора 7 -напряжение пропорциональное величине-2 С -С . Таким образом, на выходесумматора 8 в момент времени оТ Формируется напряжение, пропорциональ -ное величине И 1 Ч =2 Хф +2 С-С +Ъ+ 1), ,а на выходе сумматора 7 н этотже момент времени - напряжение, пропорциональное величине УЧ =2 Х фй)р )-2 С,-С+Ы 2 . С выходов сумматоров8 и 7 на входы блока 10 поступают 25напряжения, пропорциональные значениям И . Максимальное из двух поса.).2тупивших на вход блока 10 значенийнапряжения через блок 12 поступаетна третьи входы сумматоров 6 и 7.Значения напряжений с выходов этихсумматоров поступают на входы компаратора 14, на выходе которого формируется напряжение, соответствующеелибо "0", либо "1", причем "0" соответствует ситуации, когда значениенапряжения на выходе сумматора 8 больше значения напряжения на выходесумматора 7. Логические напряженияс выходов комк 13 и 14 поступают соответственно на втсрой и первый входы решающего блока 15,Две последовательности импульсов,которые получаются ка выходе компараторов 13 и 14, определяют воз- " 45можные сочетания переданных инфор",мационных символов Так, "0" на выходе компаратора 13 на интервалевремени (ц)Т; сТ ., соотнетствуетпаре инфо;,макионных символов50Я Ч- с)й, Й 1 (О; О), а "1" единицана выходе компаратора 13 - пареи. ) и)02 Й, 1;О). В свою очередь, ."0" ка вьжоде компаратора 14 на томже интервале времени соответствуетпаре икФормационных символовИ)й, 62 (О;1), а "1" на выходе(Ч) 4 компаратора 14 - паре й 2 д 2 1;1) . Решающий блок 15 производит последовательный анализ этих пар инФормационных символов и определяет наиболее достоверную последовательность переданных символов в соответствии с алгоритмом приема в целом. Рассмотрим два случая, В первом предпоЛагается, что на интервале времени(ц) Т; 1 Т на ныходах обоих компараторов 13 и 14 напряжения по своей полярности совпадают, т,е, имеется либо "1", что соответствует(Ч-) ситуации когда символ й ", предешествующий данному Й , однозначно определен и ранен единице, либо 0", что соответствует ситуации,(Ч "когда Йе равен нулю. Для опредеЧ- )ления с)необходимо учесть значения пары символов с 1" 2),1 щ- (Р1=1,2),полученных на предыдущем интервале времени (Ч)Т; (с)-1)ТДалее требуется на каждом интервале Ь)-1)Т; оТ определить из пар сим(Ч)1)волов Й Йтакую В которой посл едоки символ(Ч- )совпадает по значению с первйм символом следую(Ч-) (Ч)щей пары Й е й . Во втором предполагается, что напряжения на выходах компараторон 13 и 14 на интервале времени-1)Т;с)Т по своим значениям различаются, к в этих условиях значение символа однозначноопределить невозможно.Решающий блок 15 работает следующим образомВ первом случае ка выходе сумматора по модулю два 1 Формируется "1", которая через элемент ИЛИ 18 поступает на последовательные входы регистров 19 и 20, ко,ка регистр 20 с инверсией. Кроме того, эта "1" поступает на управляющие входы коммутаторов 21 и 22. На второй вход сумматора 16 поступает задержаккое на время Т с помощью блока 23 значение симвоИ.)ла Йе, находящееся в регистре .19. Для первого случая возможны две; ситуации:- значение символа Йе совпадает со значением логического уровня, поступающего с выхода компаратора 13. Тогда на выходе сумматора 16 Форми 1603534руется "1", поступающая как на первый вход элемента ИЗИ 18, так и на управляющие входы коммутаторов 21 и 22, При этом коммутатор 21 подключает и выходов первого регистра 19 к и параллельным входам регистра 20," происходит перезапись значений символов из регистра 19 в регистр 20. В этой Ситуации содержимое обоих регистров19 и 20 оказывается оцинаковым, При Этом перезаписи через коммутатор 22 не происходит. Далее происходит Перезапись значения символа Фф чеРез последовательные входы в регистр 19 и 20; В-значение символа д . не совейадает со значением логического уровня, поступающего с выхода компаратора13. На выходе сумматора 16 формируют ся "О", который поступает как на первый вход элемента ИЛИ 18, так ина управляюшие входы коммутаторов 21 и 22. При этом через коммутатор 22осуществляется перезапись значений 25символов из регистра 20 в регистр 19. Через коммутатор 21 перезаписи непроисходит. В этой ситуации содержимое обоих регистров 19 и 20 оказывается также одинаковым. 30Во втором случае на выходе сумматора 17 Формируется "0", который поступает как на второй вход элементаЮИ 18, так и на управляющие входыкоммутаторов 21 и 22. Через оба коммутатора 21 и 22 перезаписи не происходит, и, таким образом, осуществляется лишь последовательная записьзначений символов через последовательные входы в регистры 19 и 20, Ка пос- АО ледоватсльный вход регистра 19 с пер- вого неинверсного, выхода элементаИЛИ 18 поступает либо "О", либов зависимости от значения символа ."е , поступающего с выхода регистра 19 через блок 23 на второйвход сумм"тора 16, и значения логи ческого уровня,. поступающего на пер"вый вход сумматора 16, Уровень "О"на последовательном входе регистра 5019 соответствует ситуации когда на. -пряжени;: на входах сумматора ,6 различны, т.е. на выходе сумматора 16 имеется "О". Уровень "1" на последовательном вхоце регистра 19 соот-:гветствует ситуации когда уровни логических напряжений на входах сумматора 16 одинаковы, т,е, на его выходе Формируется "1", Заметим, что последовательный вход регистра 20подключен, как и в первом случае, квторому, инверсному, выходу элементаИЛИ 18.Обобщая оба случая работы решающего блока 15 видно, что когда наинтервале (Ч)Т; ЧТ значения напряжения на входе решающего блока 15одинаковы, тогда в регистрах 19 и 20получаются одинаковые значения символов, исключая последний 0 символ, При различных значениях напряжения на входе решающего блока 15 натом же интервале времени значенияЮ 8-Рсимволов д , и Йе в р.егистрах19 и 20 различны. Число интерваловвремени Т, в течение которых значениясимволов в регистрах 19 и 20 различны, определяется интервалом междудвумя ближайшими состояниями решающего блока 15, когда значения напряжения на этих входах оказывались одинаковыми. Величина Ь должна быть меньше и. Тогда с последнего отвода регистров 19 и 20 считывается последовательность принимаемых символов,Как видно из работы решающего блока15 каждое решение по принимаемомусимволу оказывает влияние на решениео своей предыдущей последовательности, что и является реализацией метода приема в целом,Формула изобретенияДемодулятор дискретных сигналов содержащий последовательно соединенные полосовой фильтр, вход которого является входом демодулятора, и согласованный фильтр, инвертор, четыре сумматора, два блока выбора максимального напряжения, первый блок за. держки и решающий блок, о т л и ч а - ю щ и й с я тем, что, с целью повышения помехоустойчивости, в него введены второй блок задержки, два компаратора и,целитель напряжения, причем выход согласованного Фильтра соединен с первыми входами первого и втор ого сумматоров и чер ез инвертор с первыми входами третьего и четвертого сумматоров, первый выход делителя напряжения соединен с вторыми входами первого и третьего сумматоров, второй выход делителя напряжения соединен с вторыми входами второго и четвертого сумматоров, выходы первого и второго сумматоров соедиН,Лазаре тани Техред М.Дндык Корректор А. Осауленко Редактор Л.Пчолинск Тираж 5 Подписное Зо ака омитета по изобретениям и открытиям лри ГКНТ СССРосква, Ж, Раушская наб., д. 4/5 сударствеиног 1 13035енио-издательский комбинат Патент", г.ужгород, ул . Гагарина,Произв 9 1603534Оиены с входами первого блока выбора, щего блока, выход первого блока вымаксимального напряжения и первого бора максимального напряжения через компаратора, выход которого соединен первый блок задержки соединен с трес первым. входом решающего блока выхо" тьими входами первого и четвертогоУды третьего и четвертого сумматоров сумматоров, выход второго блока выбосоединены с входами второго блока вы- ра максимального напряжения через бора максимального напряжения и вхо- второй блок задержки соединен с тре" дами второго компаратора, выход ко-. тьими входами второго и третьего сумрого соединен с вторым входом решаю- о маторов.

СмотретьЗаявка

4628847, 29.12.1988

ЛЕНИНГРАДСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

МАКАРОВ СЕРГЕЙ БОРИСОВИЧ, ЯДЫКИН ВЛАДИМИР КОНСТАНТИНОВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, дискретных, сигналов

Опубликовано: 30.10.1990

Код ссылки

<a href="https://patents.su/5-1603534-demodulyator-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор дискретных сигналов</a>

Предыдущий патент: Устройство для имитации искажений двоичного сигнала

Следующий патент: Интегрирующий усилитель тока развертки

Случайный патент: Установка для нагрева металлавснсоюанаяпщнтш-тех: "ееыбиблиотека