Приемник м-ичных дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1497746

Авторы: Абрамов, Шахгильдян

Текст

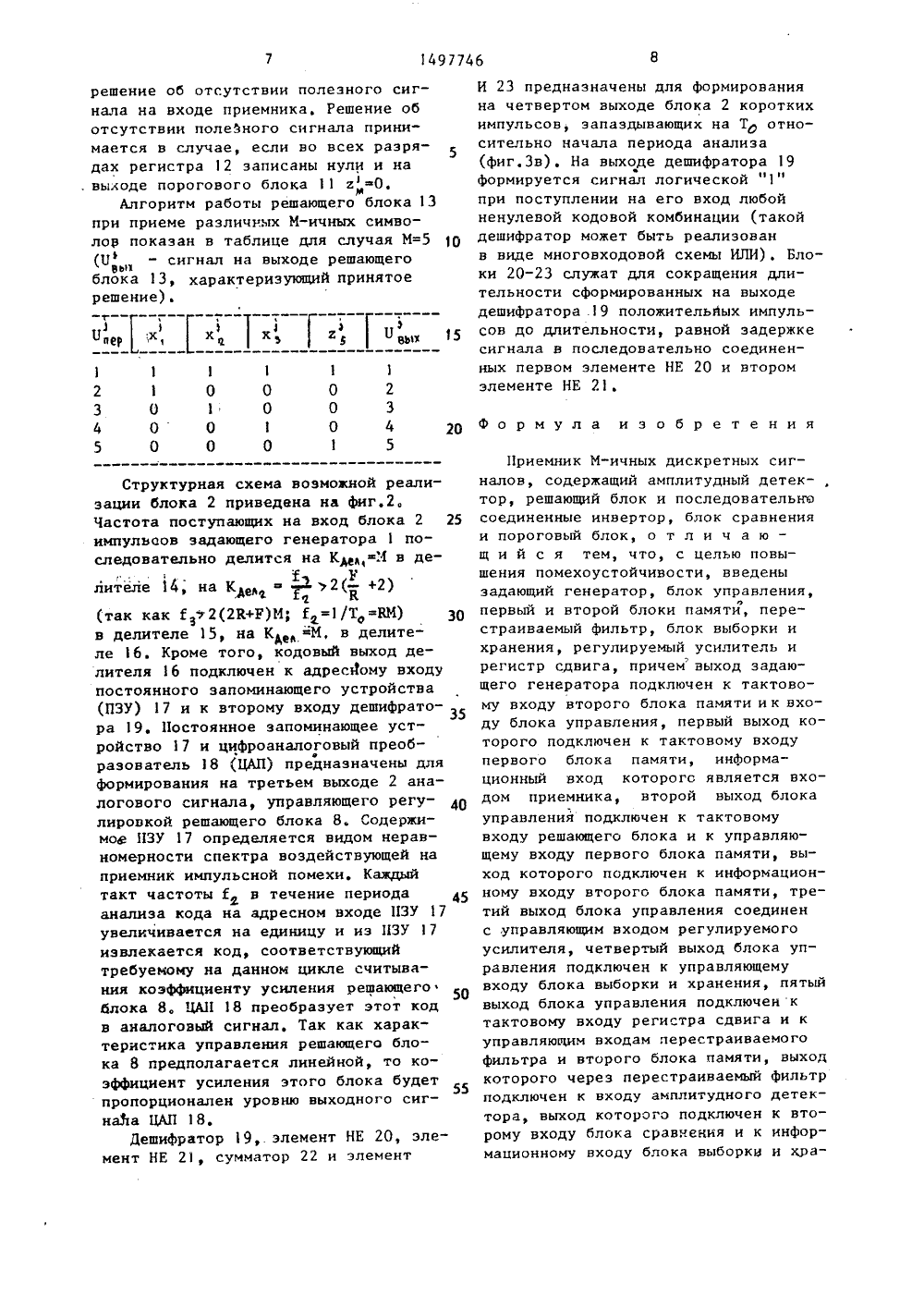

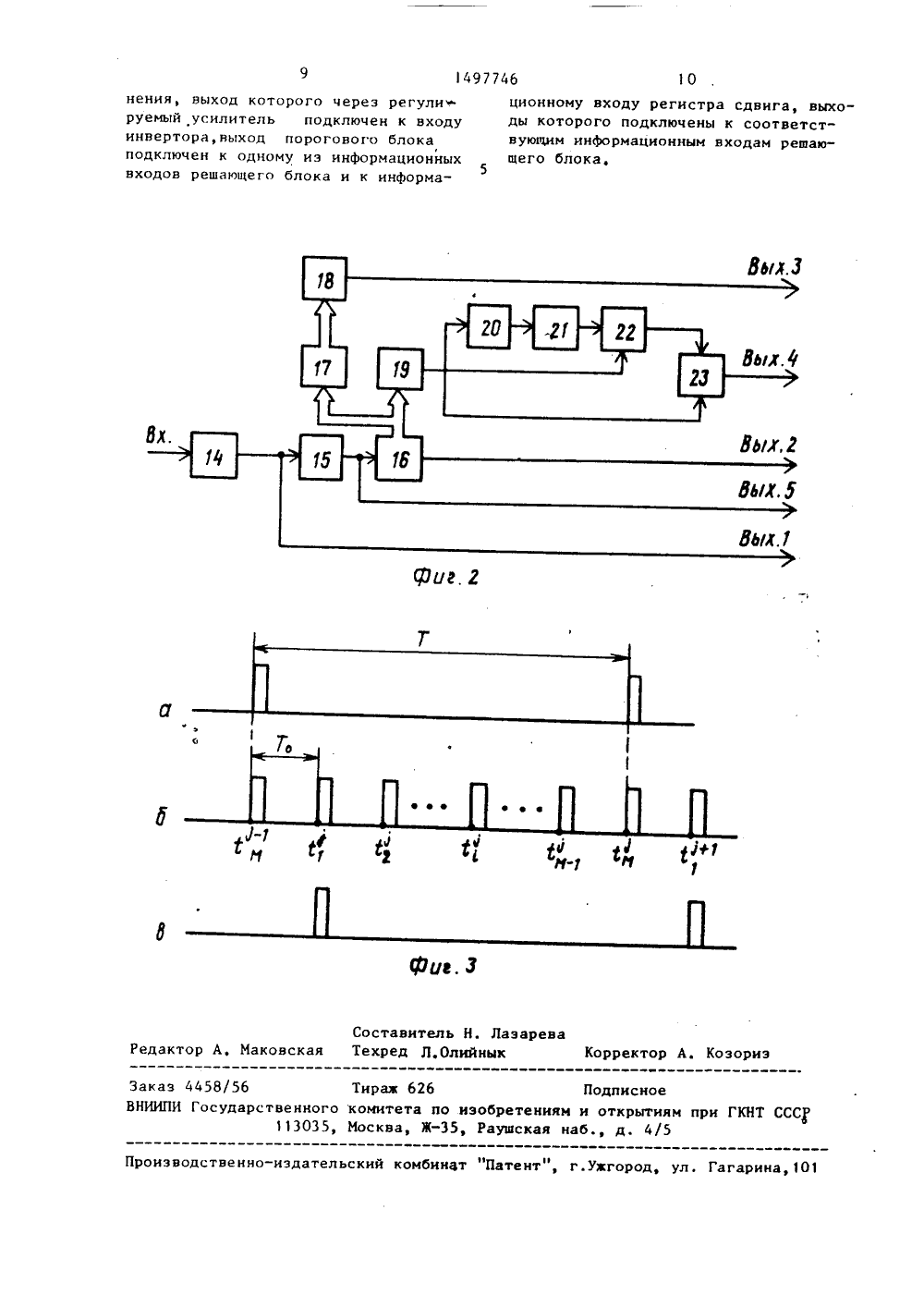

(19) 4 В 1/ вйЕСОВЗНМАТЕЙТКЭ. ГОМяЧЕСЙЯ БИБЛИОи А ПИ ИЗОБРЕТЕНИЯ К АВТОРСКОМ ИДЕТ ЕЛЬСТВ сиг мех,сле за блокступает си и 1,фо амят 4 блок пацияде форУ 28ный электротех сдвимирув Мвход Н. Абрамо(57) Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости, Приемник содержит задающий г-р 1, блок управления 2, блоки Зи 4, перестраиваемый фильтр 5, амплитудный детектор 6, блок 7 выработки и хранения, регулируемый усилитель 8, инвертор 9, блок сравнения 10, пороговыйблок 11, регистр 12 сдвига и решающий блок 13. Входной сигнал, состоящий из смеси полезногое приныйоб ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР(21) 4333842/2 А(22) 26.11,87 (46) 30.01,89, Бюл. (71) Всесоюзный зао нический институт с (12) В.В. Шахгильдя (53) 621.394,6(088. (56) Авторское свид У 687620, кп, Н 04 ается в п и, г тся отсчеты сигнала, сжатого аз по времени по сравнению с ым сигналом, Полученные отсчеты обрабатываются в фильтре 5, двтектируются по амплитуде, а затем с помощью блока 7 выборки и хранения, усилителя 8, инвертора 9 и блока сравнения 10 производится вычисление модуля суммы уровней поступивших сигналов, Далее этот сигнал поступает напороговый блок 11, который при превышении или непревышении его порогаформирует уровень логической 1"или "0". Этот бинарный сигнал записывается в регистр 12, а также поступает в решающий блок 3, который мает решение о том, какои М-ичимвол передавался, либо решение сутствии полезного сигнала на приемника, 3 ил,5 4 формационный вход блока 7 и на второй вкод блока 1011 ри поступлении на управляющий вход блока 7 импульса с четвертого выхода блока 2 уровень входного сигнала блока 7 запоминается в этом блоке и хранится до момента поступления следующего импульса на управляющий вход, Так как на четвертом выходе блока 2 формируются импульсы (фиг.Зв) в моменты времени1 то есть задержанные на Т =1/Г =Т/Моотносительно начала периода анализа, то в блоке 1 запоминается уровень сигнала 11 на выходе амплитудного1детектора Ь в момент окончания первого цикла считывания,Решающий блок 8 представляет собойусилитель постоянного тока с коэффициентом усиления, изменяющимся линейно в соответствии с уровнем сигналана его управляющем входе, Выходнойсигнал решающего блока 8 (К, Б),где К , - коэффициент усиления над-м цикле считывания, инвертируетсяв инверторе 10, Коэффициент усиленияКц инвертора 10, представляющего собой инвертирующий усилитель, выбирается таким, чтобы скомпенсировать усиление с коэффициентом Ксигнала в решающем блоке 8 при нулейом напряжении на управляющем входе решающего блока 8, то есть К, К =1. Сигнал с выхода инвертора 9 поступает на первый вход блока 10, который производит вычисление модуля суммы уровней поступивших на его вход сигналов, Таким образом, в момент окончания цикла считывания на выходе блока,О формируется сигнал у".= Б - Кр. Б,.Необходимость регулировки уровня сигнала на выходе блока 7 объясняется следующим.Пусть на входе приемника действует мпульсная помеха неизвестной интенсивности, но имеющая известный вид неравномерности спектра в полосе частот приемника ДГ, причем ширина спектра помехи ЕДЕ, Тогда при отсутствии на входе приемника полезного сигнала получим, что уровни сигналоввызванных помехой, на различных циклах считывания отличны один от другого, причем степень отличия определяется видом неравномерности спектра помехи, Для компенсации действия неравномерности спектра помехи коэффициент усиления решающего блока 8 регулируется так, что на -м97746 5 10 15 20 25 30 35 40 45 50 55 цикле, считывания он равен К РЬ" /13, (регулировка производится пу 1тем подачи на управляющий выход решающего блока 8 специального аналогового сигнала с третьего выхода блока 2). Поэтому при отсутствии на входе приемника полезного сигнала и действии импульсной помехи уровень сигнала на выходе блока 10 при любом дбудет нулевым у 1 =(1, -Б К . ( =О,в, и 1; фПри совместном воздействии импульсной помехи и по.резного сигнала с поднесущей частотой Е(2 КйМ), то естьпри йередаче символа К, имеем утО.Если же К=1 то на выходе блока ОуъО при всех 2 ЫМ. Те же результаты получаем при наличии на входе приемника полезного сигнала без помехи,Выходной сигнал блока 10 сравнивается с фиксированным порогом в пороговом блоке 11, При превышении псрога на выходе порогового блока 11формируется уровень логической ",при непревышении - уровень логического 0. Пренебрегая малой неравномерностью АЧХ перестраинаемого фильтра 5 в полосе перестройки, порог нпороговом блоке 1 можно выбрать нулевым, то есть сигнал на его выходев тактовые моменты окончания цикловсчитывания равен( 1, у,0,Этот бинарный сигнал записывается врегистр 12 с тактовой частотойимпульсов, поступающих на тактовыйвход регистра 12 с пятого выхода блока 2 (фиг,3 б), Разрядность регистра 12 равна (М). В момент окончания 1-го периода анализа (моментвремени С на фиг,36) содер-.имое -йячейки регистра 12 равнс х"=гЗ,где 11 М, 2 ИМ, В этот хе момент времени на выходе пороговогоблока 11 имеем сигнал г". Сигналыс выходов всех ячеек регистра 12 подаются на соответствующие первые(М) входы решающего блока 13, асигнал с выхода порогового блока 11на (М)-й вход решающего блока 13,Решающий блок 13 стробируется поступающими на его тактовый вход импульсами с второго выхода блока 2 (фиг.3 а)в моменты окончания периодов анализа;В эти моменты времени в решающем блоке 13 принимается решение о том, какой М-ичный символ передавался, илирешение об отсутствии полезного сигнала на входе приемника, Решение об отсутствии полезного сигнала принимается в случае, если во всех разрядах регистра 12 записаны нули и на выходе порогового блока 11 г О,Алгоритм работы решающего блока 13 при приеме различных М-ичных символов показан в таблице для случая М=5 1 О (11 и - сигнал на выходе решающего блока 13, характеризующий принятое решение). Г Г 1Ф Ф"ъ гю "вью 15 1 1 1 1 1 1 2 1 0 0 0 2 3 0 1 0 0 3 4 00 1 0 4 5 0 0 05 Структурная схема возможной реализации блока 2 приведена на фиг.2,Частота поступающих на вход блока 2 25импулвсов задающего генератора 1 последовательно делится на КА, М в двлителе 14; на КА.фХ )2(- +2)(так как 12(2 К+Р)М 1 1=1/То=НМ) 30в делителе 15, на КАМ, в делителе 16Кроме того, кодовый выход делителя 16 подключен к адресному входупостоянного запоминающего устройства(ПЗУ) 7 и к второму входу дешифратора 19, Постоянное запоминающее устройство 17 и цифроаналоговый преобразователь 18 (ЦАП) предназначены дляформирования на третьем выходе 2 аналогового сигнала, управляющего регулировкой решающего блока 8. Содержимою ПЗУ 17 определяется видом неравномерности спектра воздействующей наприемник импульсной помехи. Каждыйтакт частоты Е в течение периода 45анализа кода на адресном входе ПЗУ 17увеличивается на единицу и из ПЗУ 17извлекается код, соответствующийтребуемому на данном цикле считывания коэффициенту усиления решающегоблока 8, ЦАП 18 преобразует этот кодв аналоговый сигнал, Так как характеристика управления решающего блока 8 предполагается линейной, то коэффициент усиления этого блока будетпропорционален уровню выходного сигнала ЦАП 18,Дешифратор 19, элемент НЕ 20, элемент НЕ 21, сумматор 22 и элемент И 23 предназначены для формирования на четвертом выходе блока 2 коротких импульсов, запаздывающих на Т относительно начала периода анализа (фиг,3 в). На выходе дешифратора 19 формируется сигнал логической "1" при поступлении на его вход любой ненулевой кодовой комбинации (такой дешифратор может быть реализован в виде многовходовой схемы ИЛИ). Блоки 20-23 служат для сокращения длительности сформированных на выходе дешифратора 19 положительАых импульсов до длительности, равной задержке сигнала в последовательно соединенных первом элементе НЕ 20 и втором элементе НЕ 21,формула изобретенияПриемник М-ичных дискретных сигналов, содержащий амплитудный детектор, решающий блок и последовательно соединенные инвертор, блок сравнения и пороговый блок, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости, введены задающий генератор, блок управления, первый и второй блоки памяти, перестраиваемый фильтр, блок выборки и хранения, регулируемый усилитель и регистр сдвига, причем выход задающего генератора подключен к тактовому входу второго блока памяти ик входу блока управления, первый выход которого подключен к тактовому входу первого блока памяти, информационный вход которого является входом приемника, второй выход блокауправления подключен к тактовому входу решающего блока и к управляющему входу первого блока памяти, выход которого подключен к информационному входу второго блока памяти, третий выход блока управления соединен с,управляющим входом регулируемого усилителя, четвертый выход блока управления подключен к управляющему входу блока выборки и хранения, пятый выход блока управления подключен к тактовому входу регистра сдвига и к управляющим входам перестраиваемого фильтра и второго блока памяти, выход которого через перестраиваемый фильтр подключен к входу амплитудного детектора, выход которого подключен к второму входу блока сравнения и к информационному входу блока выборки и хра10 1497746 ционному входу регистра сдвига, выходы которого подключены к соответствующим информационным входам решающего блока.5 Составитель Н. Лазарактор А. Маковская Техред Л,Олийнык Коэориэ Корре Заказ 4458/56 Тира 3 к 626 ВНИИПИ Государственного комитета по иэоб 113035, Москва, Ж, Раениям и кая наб оизводственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,10 кения, выход которого через регули руемый усилитель подключен к входу инвертора,выход порогового блока подключен к одному из информационных входов решающего блока и к информаписное крытиям при ГКНТ СС д. 4/5

СмотретьЗаявка

4333842, 26.11.1987

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

ШАХГИЛЬДЯН ВАГАН ВАГАНОВИЧ, АБРАМОВ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H04B 1/10

Метки: дискретных, м-ичных, приемник, сигналов

Опубликовано: 30.07.1989

Код ссылки

<a href="https://patents.su/5-1497746-priemnik-m-ichnykh-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Приемник м-ичных дискретных сигналов</a>

Предыдущий патент: Декодирующее устройство

Следующий патент: Адаптивный взаимно базисный корректор

Случайный патент: Навесная лестница