Последовательно-параллельный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

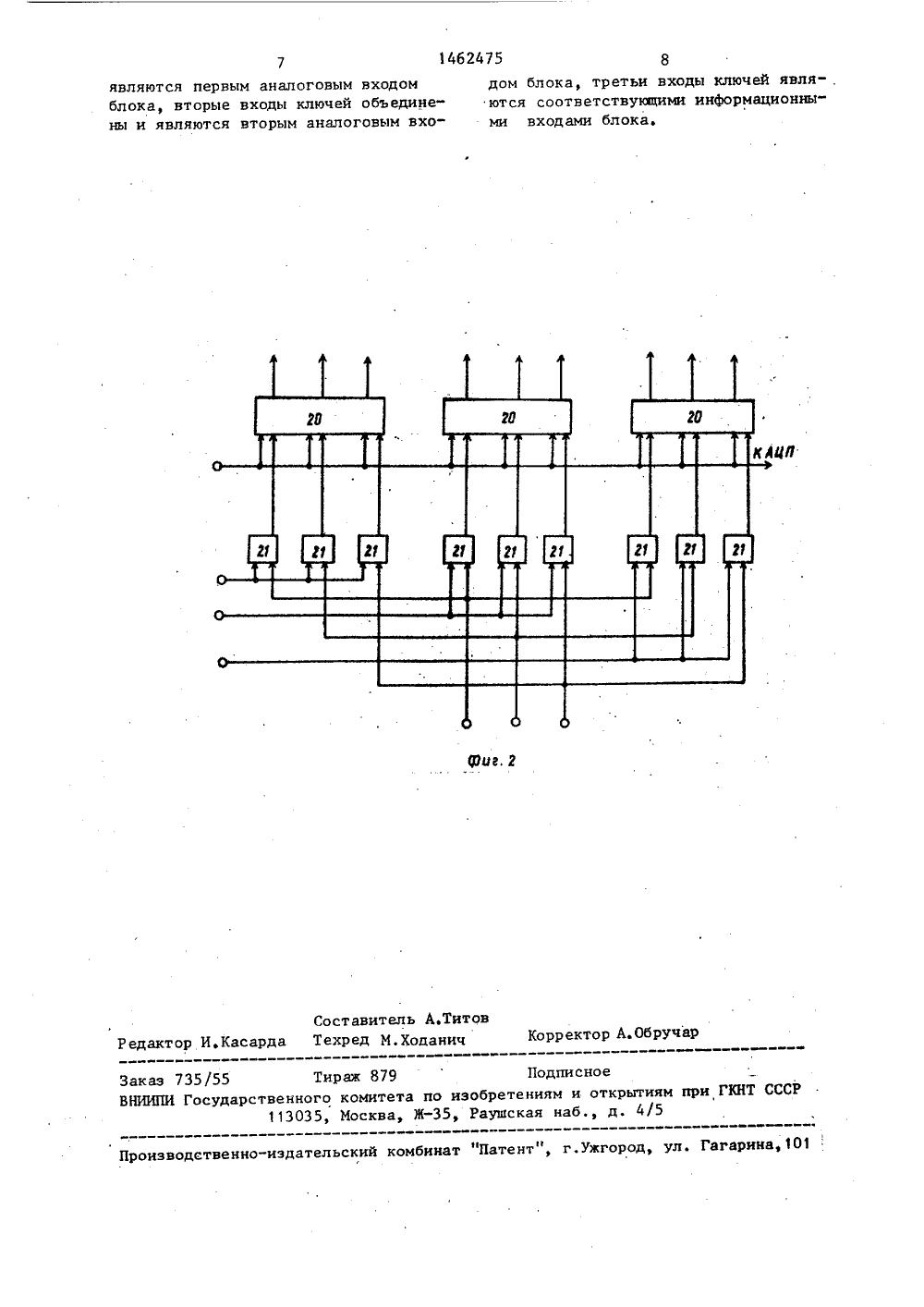

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) (Ш 2475 А ОЗМ 11 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР ПИСАНИЕ ИЗОБРЕТЕНИЯ СКОМУ А(21) 4183710/24-24 (22) 19. 01. 87 (46) 28.02.89. Бюл. У 8 (71) Таганрогский радиотехнический институт им. В;Д.Калмыкова (72) Б.М.Строцкий и Т.И.Федорова (53) 681.325 (088.8) (56) Шило В.П. Линейные интегральные схемы в радиоэлектронной аппаратуре. М.ф Советское радио, 1979, с. 348,Бахтияров Г.Д. Аналого-цифровые преобразователи. М.: Советское радио 1980, с, 204, рис. 7.28 прототип), (54) ПО СЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЪНЫИ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к измерительной технике, может быть использовано в информационно-измерительных системах, гибридных вычислительныхц комплексах, системах автоматики, регулирования и контроля.и позволяетповысить точность преобразования.Это достигается тем, что в преобразователь, содержащий ш-разрядныйаналого-цифровой преобразователь 2,операционный усилитель 1, блок 3управления, цифроаналоговый преобразователь 7, введены источник 4 опорного напряжения, блок 5 двухпозиционных переключателей, равноппечийделитель 6 напряжения, счетчик 11,дешифратор 12, элемент 10 задержки,инвертор 9, умножающий цифроаналоговый преобразователь 8, а цифроаналоговый преобразователь 7 выполнен ввиде секционированного умножающегоцифроаналогового преобразователя.3 зп. ф-лы, 2 ил.Изобретение относится к иэмери, елькой технике и может быть использовано в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматики,регулирования и контроля.Цель изобретения - повышение точности преобразования,На Фиг.1 приведена Функциональнаясхема преобразователя; на фиг.2 -функциональная схема блока управления.Преобразователь содержит операци:онньй усилитель 1, ш-разрядный аналого-цифровой преобразователь 2,, блок 3 управления, источник 4 опорного напряжения блок 5 двухпозиционных переключателей, равноплечий делитель б напряжения, секционированный умножающий. цифроаналоговый пре образователь 7, умножающий цифроаналоговый преобразователь 8, инвер,тор 9, элемент 10 задержки, счетчик11, дешифратор 12. 25Секционированный умножающий цифроаналоговый преобразователь содержит ключи 13, резисторы 14. Умножающий цифроаналоговый преобразовательсодержит ключи 15, резисторы 16. 30Равноплечий делитель 6 содержит ре, зисторы 17 и 18. Блок 5 содержит; ключи 19, Блок управления содержитрезисторы 20 и элементы И 21,Для систем с отрицательной обратной связью при достаточно большом коэффициенте усиления в контуре стабильность сигнала на выходе полностью определяется стабильностьюцепи обратной связи, 40В последовательно-параллельныханалого-цифровых преобразователяхсигнал рассогласования приводитсяк выходу ш-разрядного аналого-цифрового преобразователя Следователь-. но, контур обратной связи Формируетсяиз цифроаналогового преобразователя обратной связи и вычитающего;устройства. Поскольку эта цепь совместно с источником опорного напряжения Фактически Формирует разностьмежду эталонной мерой и измеряемойвеличиной, то путем различных корректирующих процедур, даже при точности ш-разрядного аналого-цифровогопреобразователя значительно болеенизкой, чем точность последовательнопараллельного аналого-цифрового преобразователя, погрешность преобраэования на последнем такте может быть определена каксумма относительной погрешности определения последней разности на входе ш-раэрядного аналого-циФрового преобразователя и относительной погрешности самого ш-разрядного аналого-циФрового преобраэо= ватепя. Но точность формирования раэностного сигнала на входе ш-раз-рядного аналого-цифрового преобразователя полностью определяется точность цифроаналогового преобразователя обратной связи и вычитающего узла, Следовательно, повышение точностных характеристик этой цепочки прямо влияет на повышение точности последовательно-параллельного аналого-цифрового преобразователя.Схема замещения цифроаналогового преобразователя может быть представлена в виде последовательно включен-. ных источника опорного напряжения 0 и кодоуправляемой проводимости Ум. Тогда в соответствии с фиг.1 можно записать 1 х ч + 1 нДля напряжений, получаютУ м-3 -5где Л и Л - токи на выходах пренобраэователей 8 и 7;П и Ц - напряжения входногосигнала и источника 4;У,У,Ун - проводимости делителя6, преобразователей8 и 7,Преобразователь работает следующим образом.В исходном состоянии на выходной информационной шине блок 3 устанавливает нулевой код. Это приводит к сос" тоянию суммарной проводимости умножающего цифроаналогового преобразователя 8 и секционированного умножающего цифроаналогового преобразователя 7, что выражается в следующем видеУо Уо 7 (2 1) о ф (3)где и число двоичных разрядов умножающего цифроаналогового преобразователя 8 и секционированного умножающего цифроанапогового преобразователя 7У- младший квант цифроуправляемой проводимости.15 091 Пх 2 -Бо. Ю,(6) где цб 0,1 В начальном состоянии счетчик 11 обнулен и все выходы блока 5 подключены к соответствующим ,аналоговым входам преобразователя 7.Проводимость плеч равноплечного делителя б напряжения выбирается рав ной у . Тогда для напряжения на входе ш-разрядного аналого-цифрового преобразователя 2 справедливо равен О ство и(2 л 1)У .у х " ) т,е. Кх,= -1 е Кио= О. Далее блок 3 вырабатывает первый импульс запуска н-разрядного аналогоцифрового преобразователя 2 и через элемент 10 этот же импульс заносится в счетчик 11. В результате пт-раз 20 рядный аналого-цифровой преобразователь 2 выдает. результаты кодирования в блок 3, где они обрабатываются по установленному алгоритму и поступают на выходную шину. К этому моментупервый ключ 19 блока 5 под воздействием сигнала с выхода дешифратора 12 подключает аналоговый вход первой секции секционированного умножающего цифроаналогового преобразователя 7 к выходу источника 4 опорного напряжения. Причем число разрядов секции равно т. Старшие т разрядов блока 3 осуществляют управление 3соответствующими ключами 15 умножаю." щего цифроаналогового преобразовател-яя 8 и старшей секции секционирован" ного умножакщего цифроаналогового преобразователя 7.40В результате в схеме устанавливаются следующие соотношениял+,+ц 2 - результат первогокодирования ш-разрядного цифрового преобр аз ов ателя, 2..Следует отметить, что те разряды первой секции, для которых 8; равно. нулю, не выключаются их схемы, а замещают аналогичные разряды в умножающем цифроаналоговом преобразователее 8,Проводимость, которая в зависимости от значения М, исключается из У, включается параллельно У. В то же время, поскольку на информационный вход умножающего цифроаналогового преобразователя 8 поступает инверсия кода И, то соответствующие проводимости будут исключены из У, так как оба их вывода получаются подключенными к одной и той же точке - инвертирукщему входу операцион. ного усилителя 1.Для сигнала на входе ш-разрядного аналого-цифрового преобразователя 2 после первого такта преобразования получают Второй и все последукицке такты преобразования протекают аналогичным образом. В результате коэффициент передачи операционного .усилителя 1 возрастает эа счет уменьшения проводимости цепи обратной связи. В то же время преобразователь 7 обратной свя" зи формируется из освободившихся про водимостей посекционно, Причем неиспользуемые в зависимости от формиру". емого кода проводимости замещают аналогичные проводимости из состава умножающего цифроаналогового преобра-. зователя 8. В результате погрешности, вносимые на предыдущем такте проводимости из состава у, вычитаются в последующем такте, так как проводимости будут входить уже в состав У или ух .Для-го такта преобразования можно записать следующие основные соотношенйя к= - 2 (7)(ив-е 1К =-Ы =-(а 2 +Вк(ее-Ф (е-йх 2 +я 2) (8) На последнем такте преобразования сформированный код в цепь .обратной связи не вводится, а только поступает на последние разряды выходной шины,Формула изобретения 1. Последовательно-параллельныйаналого-цифровой преобразователь, 1462475содержащий блок управления, ш-разрядный. анапого-цифровой преобразователь и операционный усилитель, выход которого соединен с инормационным входом ш-р аз рядно го анап ого-цифрового преобразователя, информационные выходы которого соединены соответственно с информационными входами блока упранления, информационные выходы которого соединены с соответствующими информационными входами ,цифроаналогового преобразователя и яв.ляются выходной шиной, о т л и ч а ю - щ и й с я тем,что, с целью повышения точности,в него введены умножающий цифроаналоговый преобразователь, блокдвухпозиционных переключателей, элемент задержки, счетчик, дешифратор, инвертор, ранноплечий делитель напряжения, источник опорного напряжения,,а цифроаналоговый преобразователь выполнен в виде секционированного умножающего цифроаналогового преобразователя, причем выход источника опорного напряжения соединен с эталонным входом ш-разрядного аналого-цирового преобразователя и первыми информационными входами блока двухпозиционных переключателей, вторые информационные входы которого соединены с выходом операционного усилителя и с выходом равноплечего делителя напряжения, а выходы соединены с соответствующими аналоговыми входами секциониронанного умножающего цифроаналогового преобразователя, выход которого объединен с выходом и соединен с первым аналоговым входом умножающего цифроаналогового преобразователя, с первым входом ран" ноплечего делителя напряжения и с иннертирующим входом операционного усилителя, неинвертирунщий вход которого является шиной нулевого потенциала, второй аналоговый вход умножающего цифроаналогового преобразователя объединен с вторым входом равноплечего делителя напряжения, с информационным входом секционированного умножающего цифроаналогового преобразователя и янляется входной шиной, информационные выходы блока упранления через инвертор соединены с соответствующими информаци=. онными входами умножаюшего цифроаналогового преобразователя,управляющий выход блока управления соединен с управляющим входом ш-разрядного10 15 что блок управления выполнен на ре 20 25 30 35 40 50 55 аналого-цифрового преобразователя ичерез элемент задержки соединен сосчетным входом счетчика, выходы которого соединены с соответствующимивходами дешифратора, выходы которогосоединены с соответствующими управляющими входами блока двухпозиционных переключателей, и-управляющихвходов блока управления являютсяшиной Запуск. 2. Ло следов ател ьно-пар алл ел ьный анапого-цифровой преобразователь по п.1, о т л и ч а ю щ и й с я тем,гистрах и группах элементов И, первые входы элементов И каждой группы .объединены и являются соответствую-,щим информационным входом блока, выходы элементов И 1-й группы соединены с соответствующими первыми входами -го регистра, выходы регистровявляются соответствующими информационными выходами блока, вторые входы регистров объединены и являютсяпервым управляющим входом и управляющим ныходом блока, вторые входы одноименных элементов И всех группобъединены и являются соответствующими иуправляющими входами блока. 3. Последовательно-параллельныйаналого-цифровой преобразовательпо п.1, о т л и ч а ю щ и й с ятем, что секционированный умножающийцифроаналоговый преобразователь выполнен на группах ключей и резисторах, первые входы всех ключей объединены и являются информационнымвходом блока, вторые входы ключейкаждой 1.-й группы объединены и являются соответствующим 1.-м аналоговымвходом блока, третий вход каждогоключа является соответствующим информационным входом блока, выходкаждого ключа соединен с первым вы"водом соответствующего резистора,вторые выводы резисторов объединеныи являются выходом блока,4. Последовательно-параллельныйаналого-цифровой преобразователь поп.1, отличающийся темчто умножающий цифроаналоговый преобразователь выполнен на ключах ирезисторах, первые выводы которыхобъединены и являются выходом блока,второй вывод -го резистора соединенс выходом -го ключа, первые нхЬдыключей соответственно объединены и1462475 Составитель А.Титоврда Техред М.Ходанич орректор А.Обруч едакт аз 735/55 Тираж 879 ПодпиНИИПИ Государственного комитета по изобретениям 113035, Москва, Ж, Раушская н н Т СССР открытиям при Г д. 4/5 В Производетвенно-издательский комбинат Патент , г.ужгород, ул. Гагари а,1 3 Г ина 1 являются первым аналоговым входомблока, вторые входы ключей объединены и являются вторым аналоговым вхо 8дом блока, третьи входы ключей являются соответствунзцими информационными входами блока.

СмотретьЗаявка

4183710, 19.01.1987

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

СТРОЦКИЙ БОРИС МИХАЙЛОВИЧ, ФЕДОРОВА ТАТЬЯНА ИВАНОВНА

МПК / Метки

МПК: H03M 1/14

Метки: аналого-цифровой, последовательно-параллельный

Опубликовано: 28.02.1989

Код ссылки

<a href="https://patents.su/5-1462475-posledovatelno-parallelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Последовательно-параллельный аналого-цифровой преобразователь</a>

Предыдущий патент: Двоично-десятичный счетчик в коде 8-4-2-1

Следующий патент: Преобразователь импульсов датчика перемещения

Случайный патент: Устройство для вывода графической информации