Генератор базисных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

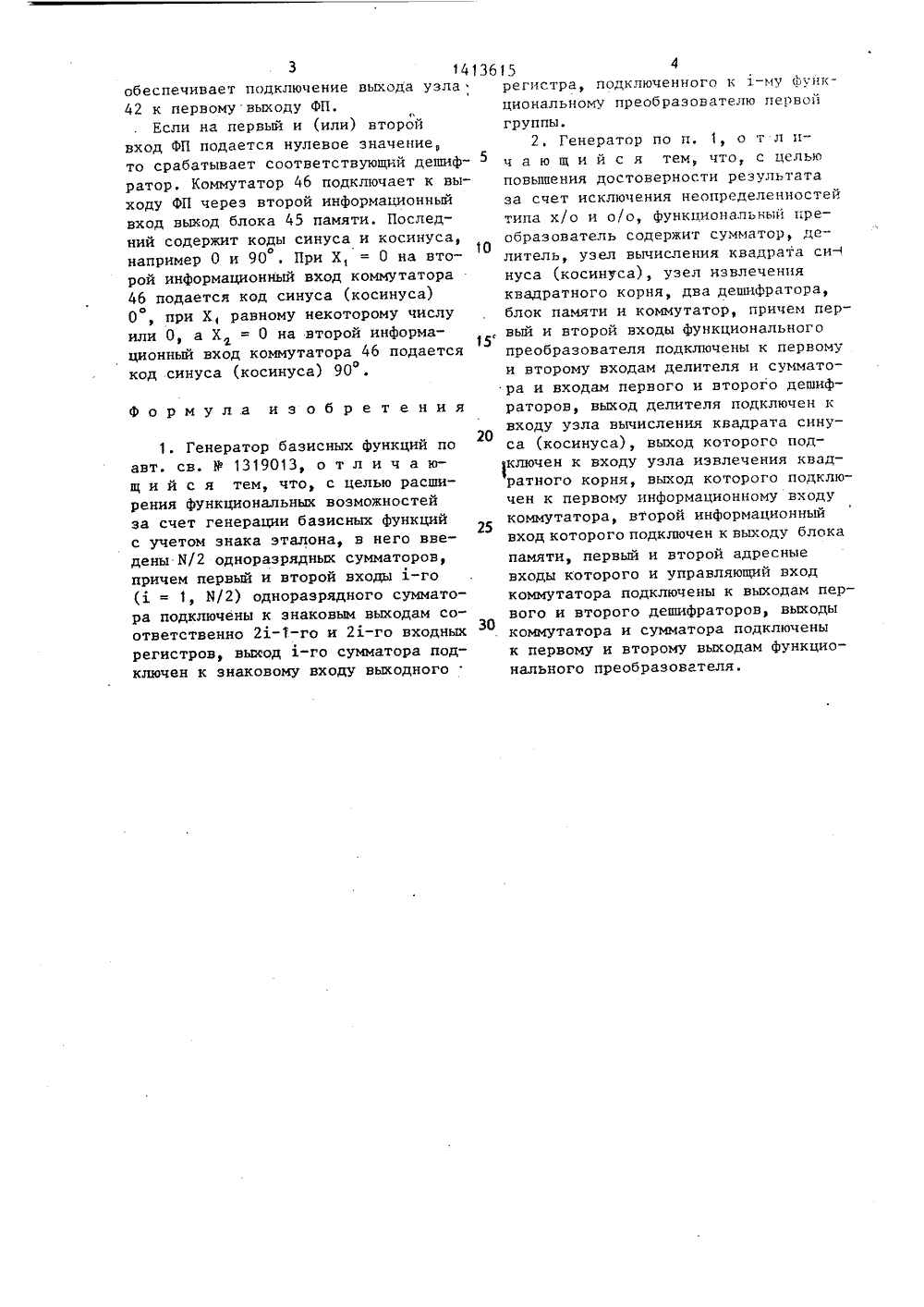

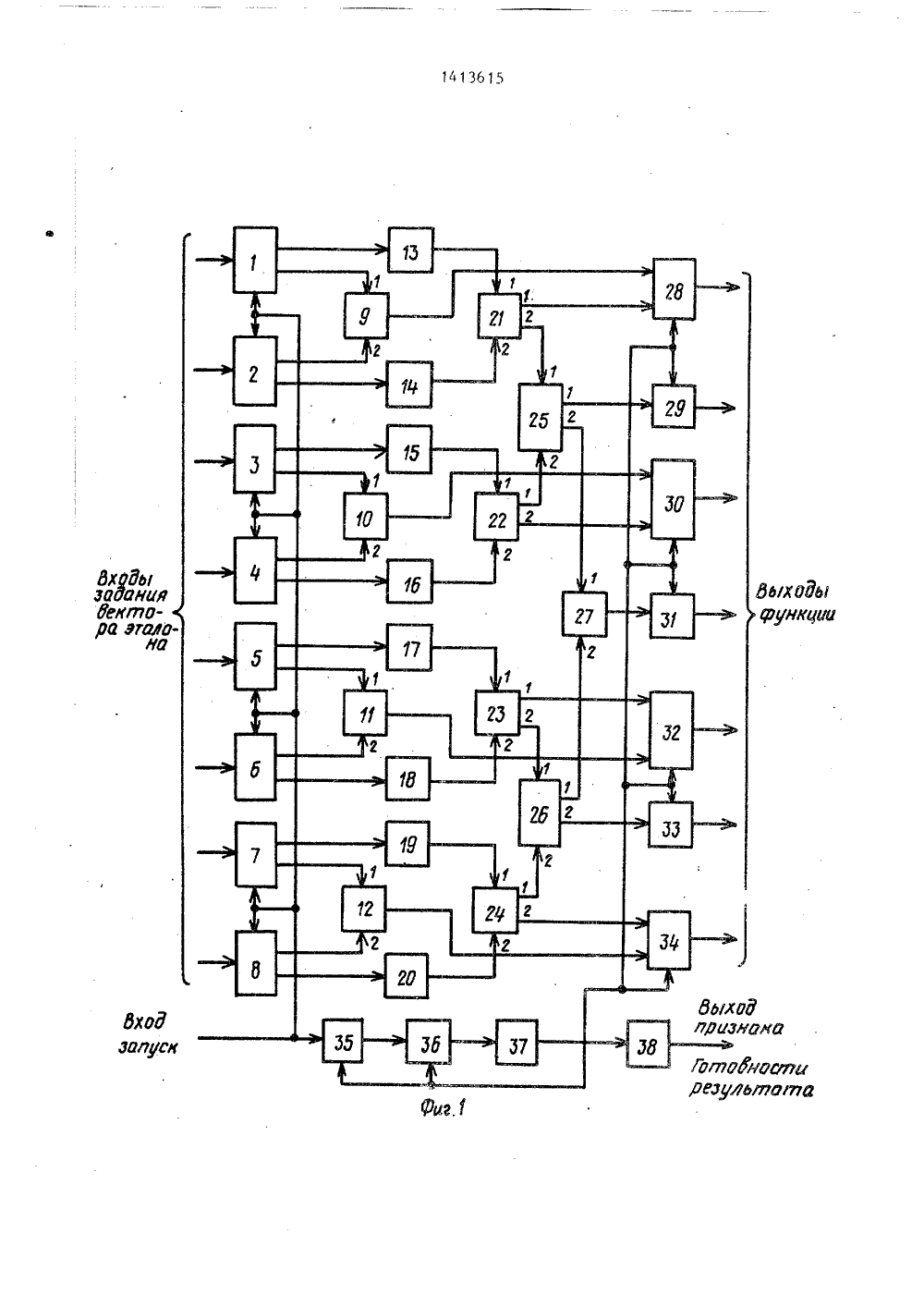

ОЮЗ СОВЕТСКИХОЦИАЛИСТИЧЕСНИХ 19) (1 1 1 СПУБЛИН 51) 4 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ВСЕСюйз.И ОПИСАН АЮТОРС БРЕТЕНИЯ И ТЕ:.,.4Я 1 ЯОТЯЛ У ТЕЛ оль 4-24 ном аЦельционалнерацизнакадости Бюл. В 28ьев, П.Ф.ДУР 8.8)свидетельство СССР С 061/Огю 1986однор нальн но вв(54) ГЕНЕРАТОР БАЗИСНЫХ ФУНКЦИЙ(61) 1319013 (21) 4183063 (22) 16,01,87 (46) 30,07,88 (72) В,А.Григ и В,А.Шабалов (53) 681,325( (56) Авторско Яф 1319013, кл овано для генерирования базиснкций, например, при спектраль нализе случайных процессов.изобретения - расширение функьных возможностей за счет ген базисных функций с учетом эталона. Поставленная цель ается за счет введения Х/г эрядных сумматоров, В функциоый преобразователь дополкительдены первый и второй дещифраблок памяти, коммутатор. 1 з.пИзобретение относится к вычислительной технике и может быть использовано для генерирования базисных функций, например, при спектральном анализе случайных процессов.Цель изобретения - расширение функциональных возможностей за счет генерации базисных функций с учетом знака эталона и повышение достоверности результата эа счет исключения неопределенностей типа х/о и о/о,На фиг. 1 приведена структурная схема генератора, на фиг. 2 - схема функционального преобразователя. 5Генератор базисных функций (ГБФ) содержит (фиг.1) входные регистры 1 - 8, одноразрядные сумматоры 9 - 12 квадраторы 13 - 20, функциональные преобразователи (ФП) 21 - 27, выходные регистры 28 - 34, генератор 35 импульсов (ГИ), счетчик 36, дешифратор 37 и триггер 38. ФП (фиг. 2) содержит сумматор 39, делитель 40, узел 41 вычисления квадрата синуса (косинуса), узел 42 извлечения квад - ратного корня, дешифраторы 43 и 44, блок 45 памяти и коммутатор 46.Генератор работает следующим образом. 30ГБФ работает аналогично устройству-прототипу, Перед началом работы устройства ГИ 35 выключен, счетчик 36 и триггер 38 установлены в исходное, например, нулевое состояние. При поступлении на вход запуска устройства импульса запуска включается ГИ 35 и с входов задания векторов эталона в регистры 1 - 8 записывается эталон сигнала. Частота импуль 40 сов на выходе ГИ 35 и емкость счетчика 36 подбираются так, чтобы время формирования на входе дешифратора ,37 определенной кодовой комбинациибыло равно времени преобразования эталона в коэффициенты базисной сис 45 темы функций.Отсчеты эталона с выходов регистров 1 - 8 подаются через квадраторы 13 - 20 на входы ФП 21 - 27, На входы ФП 22 подаются отсчеты с выходов квадраторов 15 и 16, на входы ФП 21 - с выходов квадраторов 13 и 14, на входы ФП 23 - с выходов квадраторов 17 и 18, на входы ФП 24 - с выходов квадраторов 19 и 20. 55На первых выходах ФП 21 - 27 формируются коды синусов и косинусов искомой базисной системы функций, На вторых выходах ФП 21 - 24 формируются соответственно суммы квадратов отсчетов Х 2 + Х 2 Х 2+ Х Х" + Х 2 Х+Х,2 Э 3абе 7 В Эти суммы подаются соответственно на первый и второй входы ФП 25, на первый и второй входы ФП 26.На вторых выходах ФП 25 и 26 формируются соответственно суммы квадратов отсчетов Х + Х + Х + Х и Х + Х +2 З а 5 6 +Х + Х . Эти суммы подаются на первый и второй входы ФП 27. В момнт окончания работы ФП 27 на вход записи выходных регистров 28 - 34 подается импульс с дешифратора 37,и полученные значения синусов и .косинусов базиса записываются в выходные регистры 28 - 34, Одновременно триггер 38 устанавливается в состояние, информирующее о завершении формирования базисной системы функций.Формирование базисных функций с учетом знака эталона обеспечивается одноразрядными сумматорами 9 - 12, на входы которых подаются потенциалы знаковых разрядов с знаковых выходов входных регистров 1 - 8. На первый и второй входы сумматора 9 подаются потенциалы знаковых разрядов соответственно с знаковых выходов входных регистров 1 и 2, на первый и второй входы сумматора 10 - с знаковых вы - ходов входных регистров 3 и 4, на первый и второй входы сумматора 11 с знаковых выходов входных регистров 5 и 6; на первый и второй входы сумматора 12 - с знаковых выходов входных регистров 7 и 8. Результат сложения по модулю 2 (1+1=0, 1+0=1;0+1=1, 0+0=0) подается с выходов сумматоров 9 - 12 на входы знака синуса соответственно выходных регистров 28, 30, 32 и 34, в которые зап. аа - ются коды синусов (косинусог ,:"ьей матрицы Гуда, От знака отсчетов эта,лона зависит ядро третьей матрицы Гуда.Принцип работы ФП 21 - 27 состоит в следующем. Входные данные, например Х, и Х поступают на первый и второй входы сумматора 39 и делителя 40. Сумма Х + Х с выхода сумГ 2матора подается на второй выход ФП. На выходе делителя 40 формируется отношение вида Х,/Х по которому в узле 41 вычисляются значения з 1 п 26, и сояВ,. Последние через узел 42 подаются на первый вход коммутатора 46, который в исходном состоянии3 14136 обеспечивает подключение выхода узла 42 к первомувыходу ФП.Если на первый и (или) второй вход ФП подается нулевое значение, то срабатывает соответствующий дешиф ратор. Коммутатор 46 подключает к выходу ФП через второй информационный вход выход блока 45 памяти, Последний содержит коды синуса и косинуса, например 0 и 90 . При Х, = 0 на втоо 10 рой информационный вход коммутатора 46 подается код синуса (косинуса) 0 , при Х, равному некоторому числу или О, а Х = 0 на второй информационный вход коммутатора 46 подается код синуса (косинуса) 90Формула изобретения1. Генератор базисных функций по авт. св. У 1319013, о т л и ч а ющ и й с я тем, что, с целью расширения функциональных возможностей за счет генерации базисных функций с учетом знака эталона, в него введены И/2 одноразрядных сумматоров, причем первый и второй входы 1-го (д = 1, Н/2) одноразрядного сумматора подключены к знаковым выходам соответственно 21-1-го и 2-го входных регистров, выход -го сумматора подключен к знаковому входу выходного . 5 4регистра, подключенного к -му функциональному преобразователю первой группы.2. Генератор по п. 1, о т л ич а ю щ и й с я тем, что, с целью повышения достоверности результата за счет исключения неопределенностей типа х/о и о/о, функциональный преобразователь содержит сумматор, делитель, узел вычисления квадрата си нуса (косинуса), узел извлечения квадратного корня, два дешифратора, блок памяти и коммутатор, причем первый и второй входы функционального преобразователя подключены к первому и второму входам делителя и сумматора и входам первого и второго дешифраторов, выход делителя подключен к входу узла вычисления квадрата синуса (косинуса), выход которого подключен к входу узла извлечения квадратного корня, выход которого подключен к первому информационному входу коммутатора, второй информационный вход которого подключен к выходу блока памяти, первый и второй адресные входы которого и управляюпдй вход коммутатора подключены к выходам первого и второго дешифраторов, выходы коммутатора и сумматора подключены к первому и второму выходам функционального преобразователя.едактор И.Каса Лончакова оррек одпнсно СССРПроизводственно-полиграфическое предприятие, г, Ужгород, ул. Проектна каз 3786/51 Тираж 704 ВНИИПИ Государстве по делам изобрет 113035, Москва, Ж, ого комитетаий и открытийаушская наб., д, 4/5

СмотретьЗаявка

4183063, 16.01.1987

ВОЕННАЯ КРАСНОЗНАМЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО

ГРИГОРЬЕВ ВЯЧЕСЛАВ АЛЕКСАНДРОВИЧ, ДУРБАЛЬ ПАВЕЛ ФЕОДОСЬЕВИЧ, ШАБАЛОВ ВИКТОР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: базисных, генератор, функций

Опубликовано: 30.07.1988

Код ссылки

<a href="https://patents.su/5-1413615-generator-bazisnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор базисных функций</a>

Предыдущий патент: Генератор биортогональных кодов

Следующий патент: Генератор нелинейных последовательностей

Случайный патент: Устройство для удаления околоплодника семян свеклы