Система передачи данных с множественным доступом

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

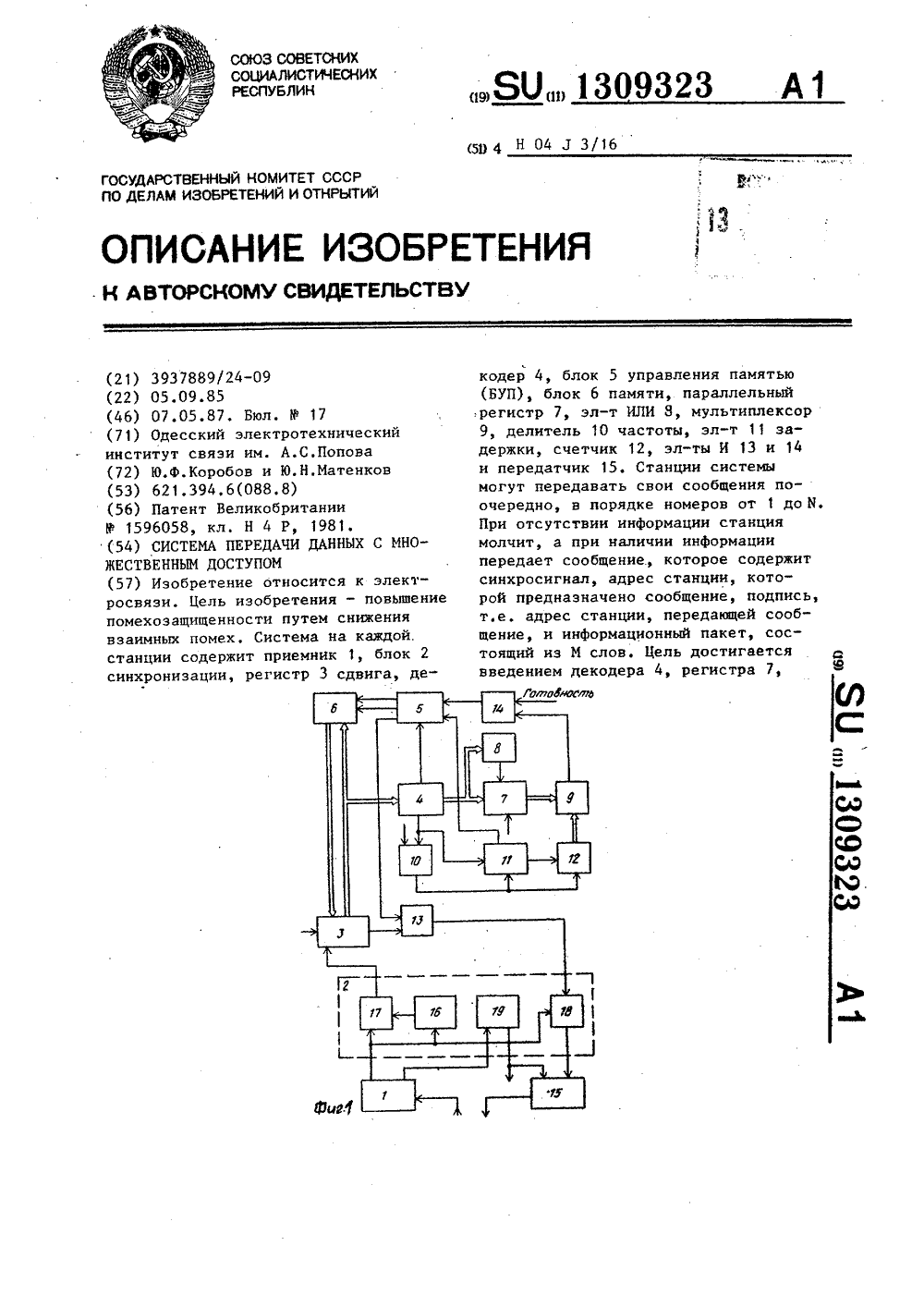

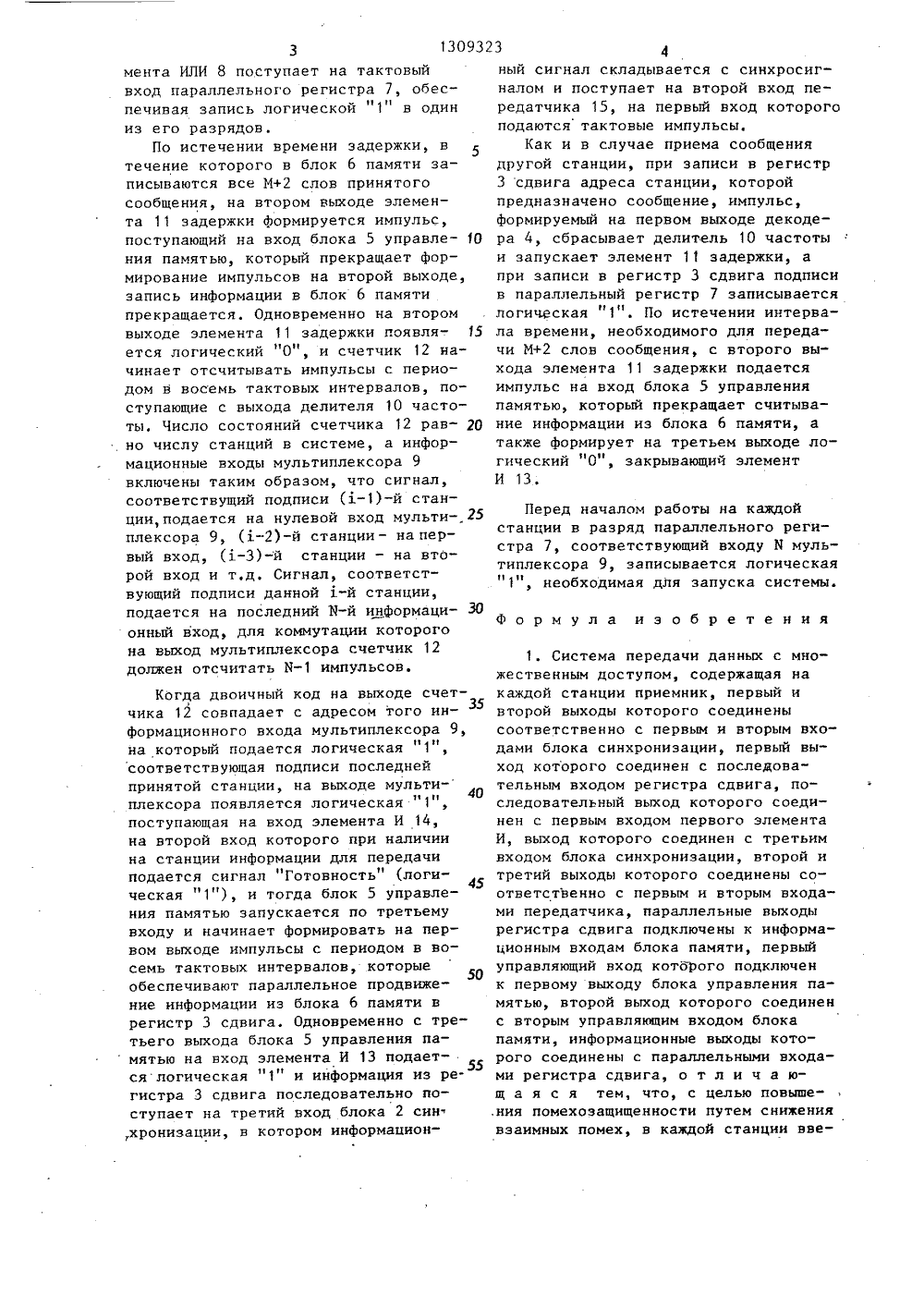

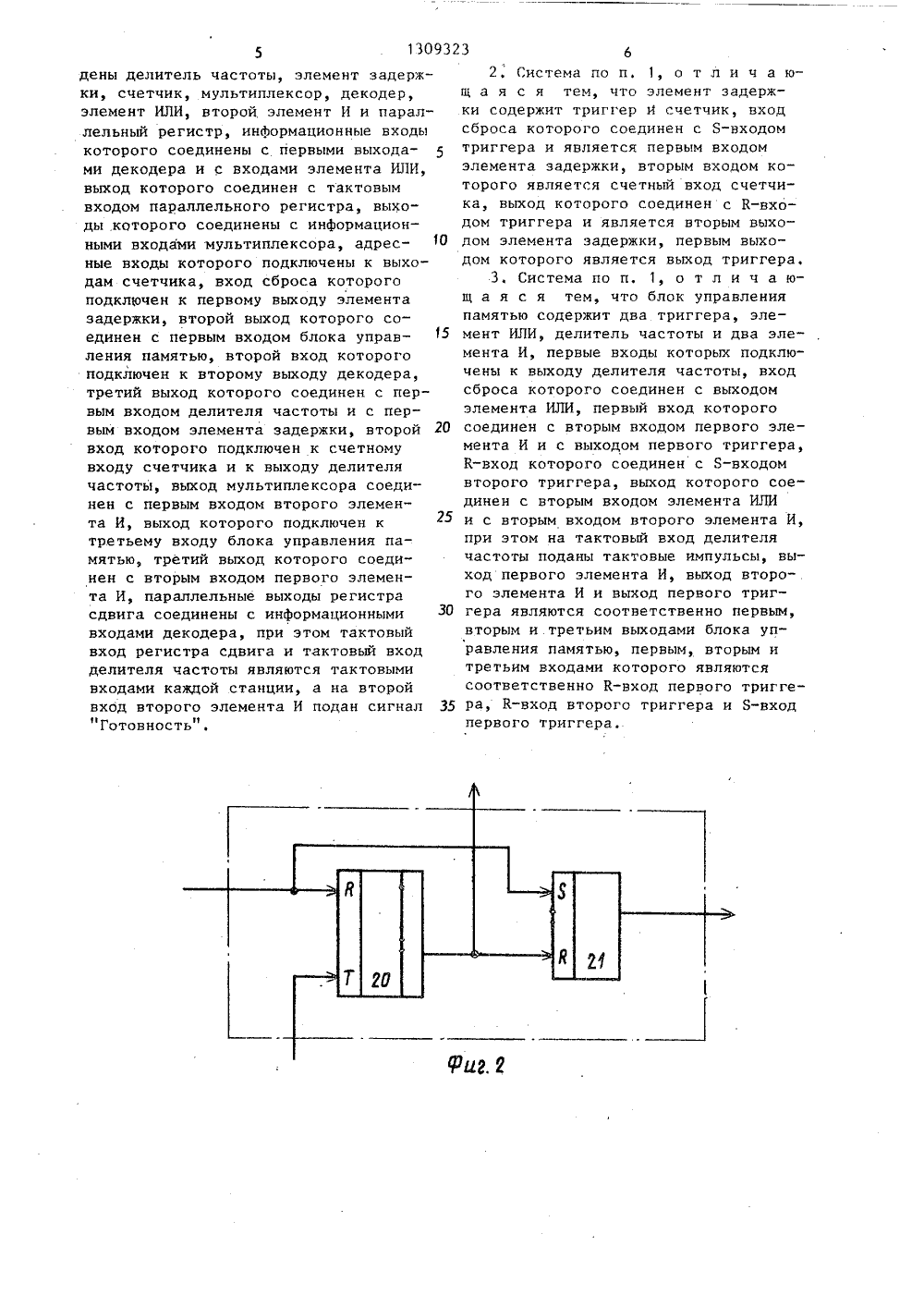

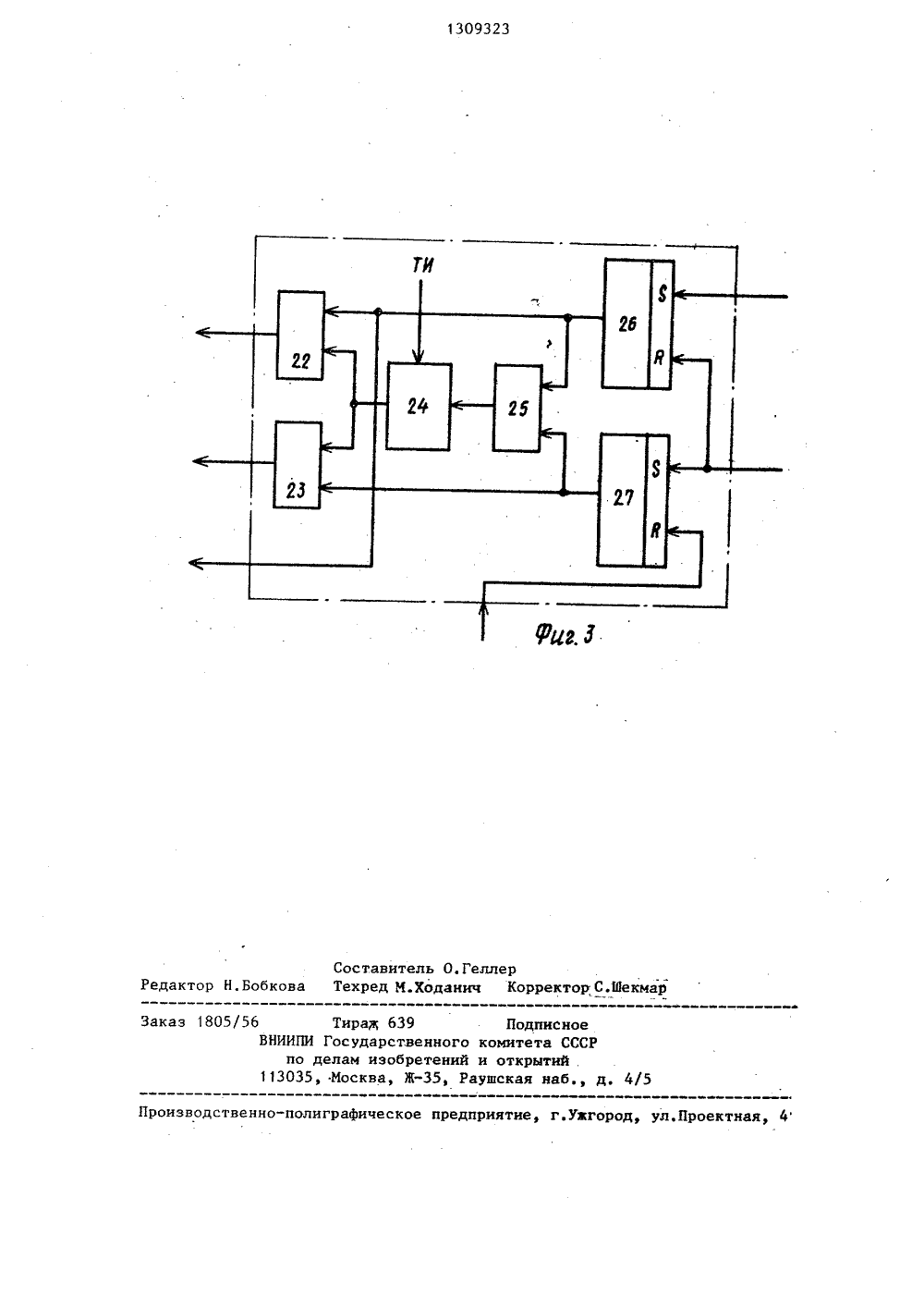

-09 лект"вьипениния аждои.лок 2де 1 ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Одесский электротехническийинститут связи им. А.С,Попова(54) СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНЖЕСТВЕННЫМ ДОСТУПОМ(57) Изобретение относится к эросвязи. Цель изобретения - попомехозащищенности путем снижевзаимных помех, Система на кстанции содержит приемник 1, бсинхронизации, регистр 3 сдвига кодер 4, блок 5 управления памятью:регистр 7, эл-т ИЛИ 8, мультиплексор9, делитель 10 частоты, эл-т 11 задержки, счетчик 12, эл-ты И 13 и 14и передатчик 15. Станции системымогут передавать свои сообщения поочередно, в порядке номеров от 1 до М.При отсутствии информации станциямолчит, а при наличии информациипередает сообщение., которое содержитсинхросигнал, адрес станции, которой предназначено сообщение, подпись,т.е. адрес станции, передающей сообщение, и информационный пакет, состоящий из М слов. Цель достигаетсявведением декодера 4, регистра 7, ф1309323 эл-та ИЛИ 8, мультиплексора 9, делителя 10, эл-та 11 задержки, счетчика 12 и эл - та ИЛИ 14. Система по Изобретение относится к электросвязи и может быть использовано для передачи дискретных сообщений.Цель изобретения - повышение помехозащищенности путем снижения взаимных помех.На фиг. 1 изображена структурная электрическая схема станции системы передачи данных; на фиг. 2 - структурная электрическая схема элемента задержки; на фиг. 3 - структурная электрическая схема блока управления памятью.Каждая станция системы передачи данных с множественным доступом содержит приемник 1, блок 2 синхронизации, регистр 3 сдвига, декодер 4, блок 5 управления памятью, блок 6 памяти, параллельный регистр 7, элемент ИЛИ 8, мультиплексор 9, делитель 10 частоты, элемент 11 задержки, счетчик 12, первый 13 и второй 14 элементы И, передатчик 15.Блок 2 синхронизации содержит декодер 16, элемент 17 вычитания, элемент 18 сложения и узел 19 фазовой автоподстройки частоты. Элемент задержки содержит счетчик 20 и триггер 21.Блок управления памятью содержит первый 22 и второй 23 элементы И, делитель 24 частоты, элемент ИЛИ 25, первый 26 и второй 27 триггеры. иСистема работает следующим образом,Станции системы пронумерованы от 1до И и могут передавать свои сообщения поочередно, в порядке номеров.При отсутствии информации станциямолчит, а при наличии информации передает сообщение, которое содержитсинхросигнал и адрес станции, которойпредназначено сообщение, подпись,т.е. адрес станции, передающей сообщение и информационный пакет, состоящий из М слов. пп.2 и 3 ф-лы отличается выполнениемэл-та 11 задержки и БУП 5, 2 з.п.ф-лы, 3 ил,Рассмотрим работу одной из станций системы с номеромСигнал, принятый из канала приемником 1, поступает на входы блока 2синхронизации, который обеспечиваетпобитовую синхронизацию принимаемогосообщения, а также формирует тактовыеимпульсы, необходимые для работыстанции.10 Информационный сигнал с первоговыхода блока 2 синхронизации последовательно записывается в восьмираз. -рядный регистр 3 сдвига. За каждыевосемь тактовых интервалов в ре гистр 3 сдвига записывается очередное слово сообщения. При записи в регистр 3 сдвига адреса какой-либо станции на первом выходе декодера 4 появляется импульс, который обеспечивает 20 кратковременный сброс делителя 10частоты на восемь и запускает элемент 11 задержки. После этого на первом выходе последнего в течение времени, равного длительности М+2 восьмибитовых слов сообщения, формируется логическая "1", которая устанавливает в "0" счетчик 12 и удерживаетего в этом состоянии. Если адрес, записанный в регистре 3 сдвига, являет ся адресом данной -й станции, навтором выходе декодера 4 также появляется импульс, запускающий блок 5управления памятью. Последний приэтом формирует на втором выходе им пульсы с периодом в восемь тактовинтервалов, обеспечивающие параллельную запись информации из регистра 3сдвига в блок 6 памяти.В тот момент, когда в регистр 3сдвига записывается подпись какойлибо станции, на одном из первых выходов (подписи) декодера 4 появляется логическая "1", которая поступает 45на один из входов параллельного регистра 7, число разрядов которогоравно числу станций в системе. Одновременно логическая "1" с выхода эле 3 13093мента ИЛИ 8 поступает на тактовый вход параллельного регистра 7, обеспечивая запись логической "1" в одиниз его разрядов.По истечении времени задержки, в течение которого в блок 6 памяти записываются все М+2 слов принятого сообщения, на втором выходе элемента 11 задержки формируется импульс, поступающий на вход блока 5 управле ния памятью, который прекращает формирование импульсов на второй выходе, запись информации в блок 6 памяти прекращается. Одновременно на втором выходе элемента 11 задержки гоявля ется логический "0", и счетчик 12 начинает отсчитывать импульсы с периодом в восемь тактовых интервалов, поступающие с выхода делителя 10 частоты. Число состояний счетчика 12 рав . но числу станций в системе, а информационные входы мультиплексора 9 включены таким образом, что сигнал, соответствущий подписи (-1)-й станции,подается на нулевой вход мульти плексора 9, (1-2)-й станции - на первый вход, (1-3)-й станции - на второй вход и т.д. Сигнал, соответствующий подписи данной 1-й станции, подается на последний Н-й информаци онный вход, для коммутации которого на выход мультиплексора счетчик 12 должен отсчитать Мимпульсов.Когда двоичный код на выходе счетчика 12 совпадает с адресом того ин 35 формационного входа мультиплексора 9, на который подается логическая "1", соответствующая подписи последней принятой станции, на выходе мульти- плексора появляется логическая " 1", поступающая на вход элемента И 14, на второй вход которого при наличии на станции информации для передачи подается сигнал "Готовность(логическая "1"), и тогда блок 5 управления памятью запускается по третьему входу и начинает формировать на первом выходе импульсы с периодом в восемь тактовых интервалов, которые обеспечивают параллельное продвижение информации из блока б памяти в регистр 3 сдвига. Одновременно с третьего выхода блока 5 управления па мятью на вход элемента И 13 подается логическая "1" и информация из ре. гистра 3 сдвига последовательно поступает на третий вход блока 2 сии ,хронизации, в котором информацион 23 4ный сигнал складывается с синхросигналом и поступает на второй вход передатчика 15, на первый вход которого подаются тактовые импульсы.Как и в случае приема сообщения другой станции, при записи в регистр 3 сдвига адреса станции, которой предназначено сообщение, импульс, формируемый на первом выходе декодера 4, сбрасывает делитель 10 частоты и запускает элемент 11 задержки, а при записи в регистр 3 сдвига подписи в параллельный регистр 7 записывается логическая 1. По истечении интервала времени, необходимого для передачи М+2 слов сообщения, с второго выхода элемента 11 задержки подается импульс на вход блока 5 управления памятью, который прекращает считывание информации из блока 6 памяти, а также формирует на третьем выходе логический "О", закрывающич элемент И 13.Перед началом работы на каждой станции в разряд параллельного регистра 7, соответствующий входу И мультиплексора 9, записывается логическаянеобходимая для запуска системы.Формула и з обретения1. Система передачи данных с множественным доступом, содержащая на каждой станции приемник, первый и второй выходы которого соединены соответственно с первым и вторым входами блока синхронизации, первый выход которого соединен с последовательным входом регистра сдвига, последовательный выход которого соединен с первым входом первого элемента И, выход которого соединен с третьим входом блока синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым входами передатчика, параллельные выходы регистра сдвига подключены к информационным входам блока памяти, первый управляющий вход которого подключен к первому выходу блока управления памятью, второй выход которого соединен с вторым управляющим входом блока памяти, информационные выходы которого соединены с параллельными входами регистра сдвига, о т л и ч а ющ а я с я тем, что, с целью повышения помехозащищенности путем снижения взаимных помех, в каждой станции вве 1309323дены делитель частоты, элемент задержки, счетчик, мультиплексор, декодер, элемент ИЛИ, второй элемент И и параллельный регистр, информационные входы которого соединены с первыми выходами декодера и с входами элемента ИЛИ, выход которого соединен с тактовым входом параллельного регистра, выходы которого соединены с информационными входами мультиплексора, адрес ные входы которого подключены к выходам счетчика, вход сброса которого подключен к первому выходу элемента задержки, второй выход которого соединен с первым входом блока управления памятью, второй вход которого подключен к второму выходу декодера, третий выход которого соединен с первым входом делителя частоты и с первым входом элемента задержки, второй 20 вход которого подключен к счетному входу счетчика и к выходу делителя частоты, выход мультиплексора соединен с первым входом второго элемента И, выход которого подключен к третьему входу блока управления памятью, третий выход которого соединен с вторым входом первого элемента И, параллельные выходы регистра сдвига соединены с информационными входами декодера, при этом тактовый вход регистра сдвига и тактовый вход делителя частоты являются тактовыми входами каждой станции, а на второй вход второго элемента И подан сигнал 35Готовность". 2, Система по п. 1, о т л и ч а ющ а я с я тем, что элемент задержки содержит триггер И счетчик, вход сброса которого соединен с Б-входом триггера и является первым входом элемента задержки, вторым входом которого является счетный вход счетчика, выход которого соединен с К-входом триггера и является вторым выходом элемента задержки, первым выходом которого является выход триггера,3, Система по п. 1, о т л и ч а ющ а я с я тем, что блок управления памятью содержит два триггера, элемент ИЛИ, делитель частоты и два элемента И, первые входы которых подключены к выходу делителя частоты, вход сброса которого соединен с выходом элемента ИЛИ, первый вход которого соединен с вторым входом первого элемента И и с выходом первого триггера, К-вход которого соединен с Б-входом второго триггера, выход которого соединен с вторым входом элемента ИЛИ и с вторым входом второго элемента И, при этом на тактовый вход делителя частоты поданы тактовые импульсы, выход первого элемента И, выход второ-. го элемента И и выход первого триггера являются соответственно первым, вторым и третьим выходами блока управления памятью, первым, вторым и третьим входами которого являются соответственно К-вход первого триггера, К-вход второго триггера и Б-вход первого триггера.1309323 Составитель О,Геллерва Техред М.Ходанич КорректорС.Шекмар Н,Боб Редак Заказ 18 4/5 ктная, 4 роизводственно-полиграфическое предприятие, г.Уагород, ул 6 Тирад 639 ВНИИПИ Государствпо делам изобр 113035, Москва, Ж нного тений 35, Р Подписное омитета ССС открытий . шская наб.,

СмотретьЗаявка

3937889, 05.09.1985

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

КОРОБОВ ЮРИЙ ФЕДОРОВИЧ, МАТЕНКОВ ЮРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H04J 3/16

Метки: данных, доступом, множественным, передачи

Опубликовано: 07.05.1987

Код ссылки

<a href="https://patents.su/5-1309323-sistema-peredachi-dannykh-s-mnozhestvennym-dostupom.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи данных с множественным доступом</a>

Предыдущий патент: Система передачи стереофонических сигналов

Следующий патент: Автоматический генератор кода морзе

Случайный патент: Способ приготовления стержневых и формовочных смесей для литейного производства