Устройство фазирования числовых последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

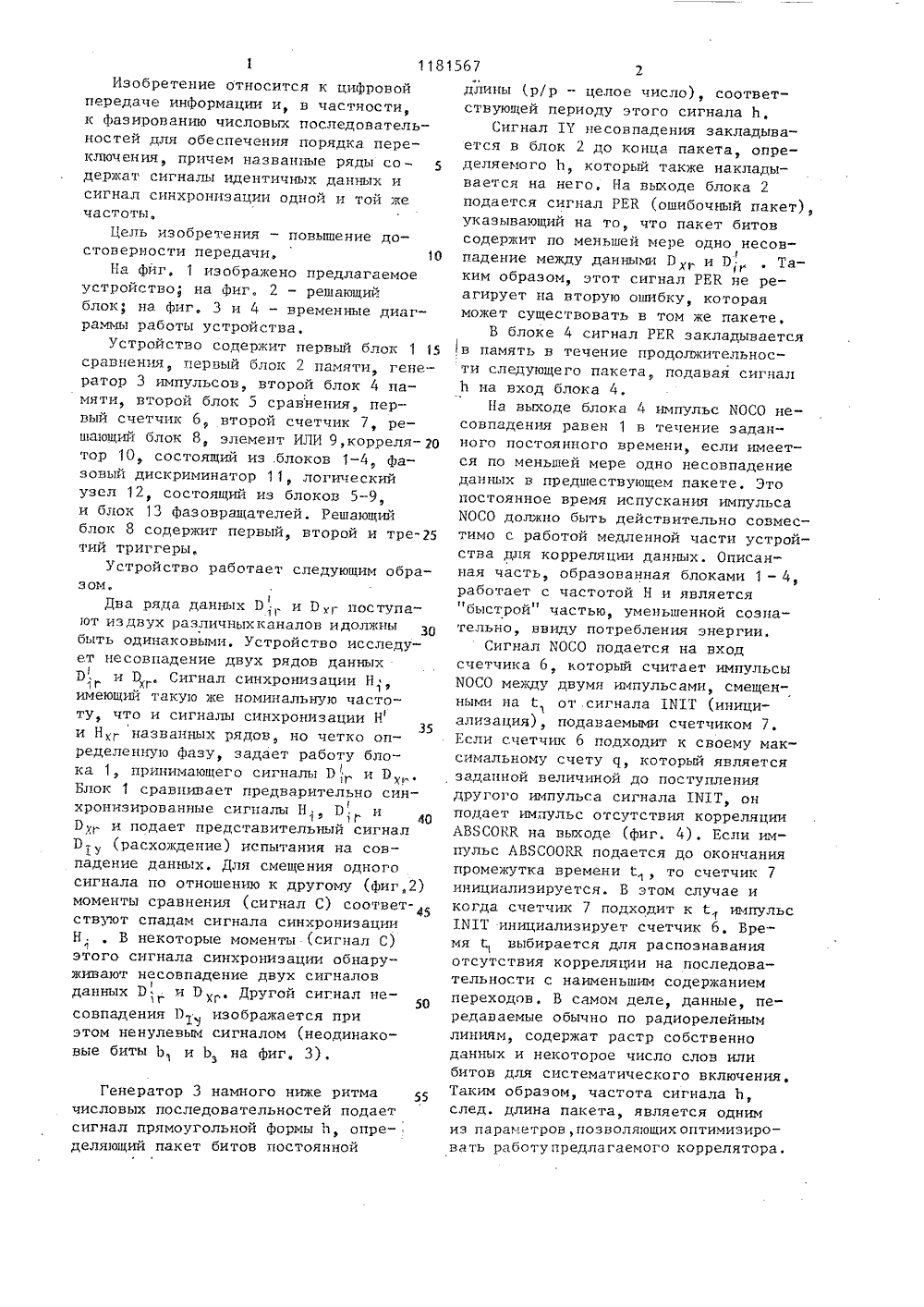

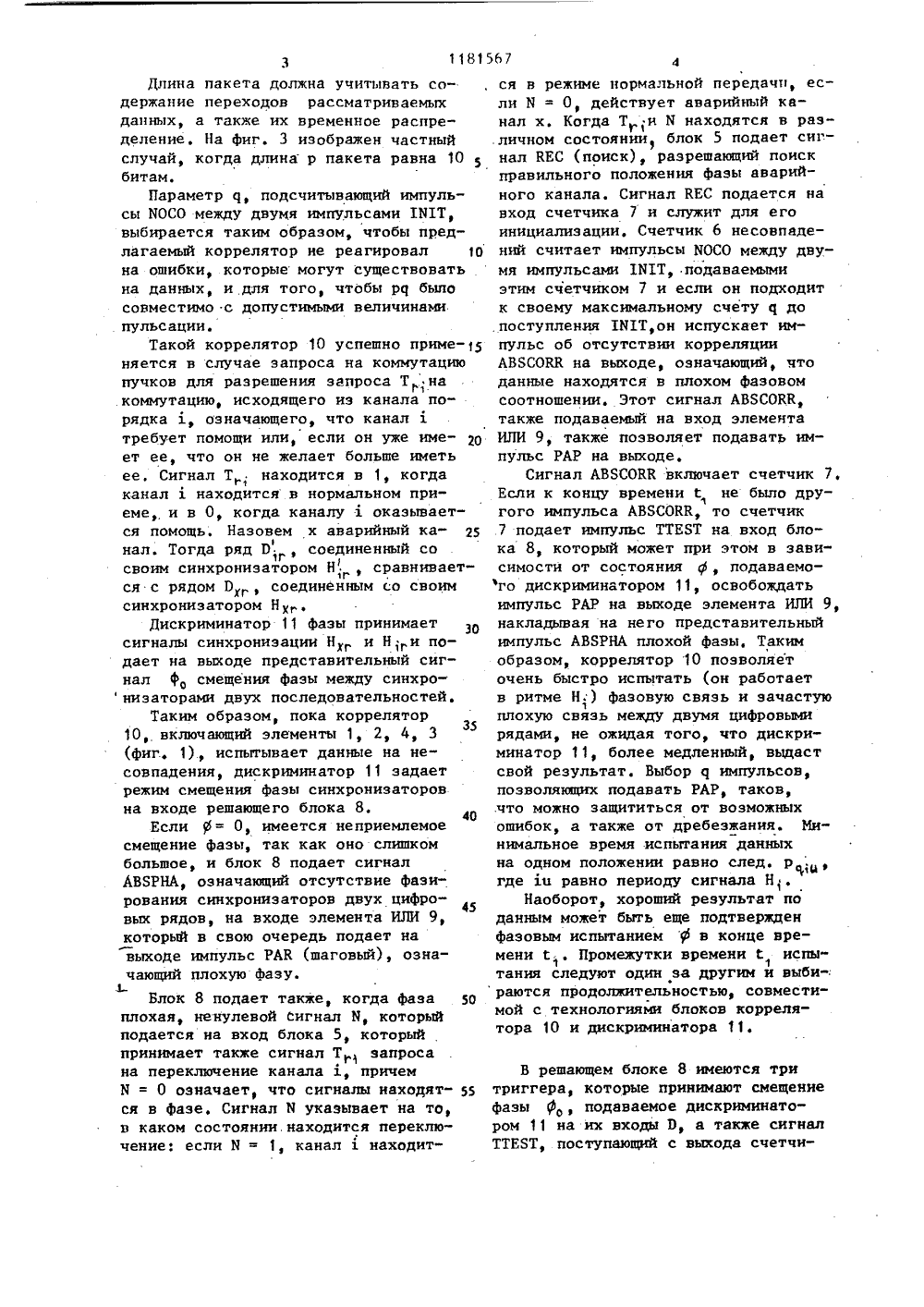

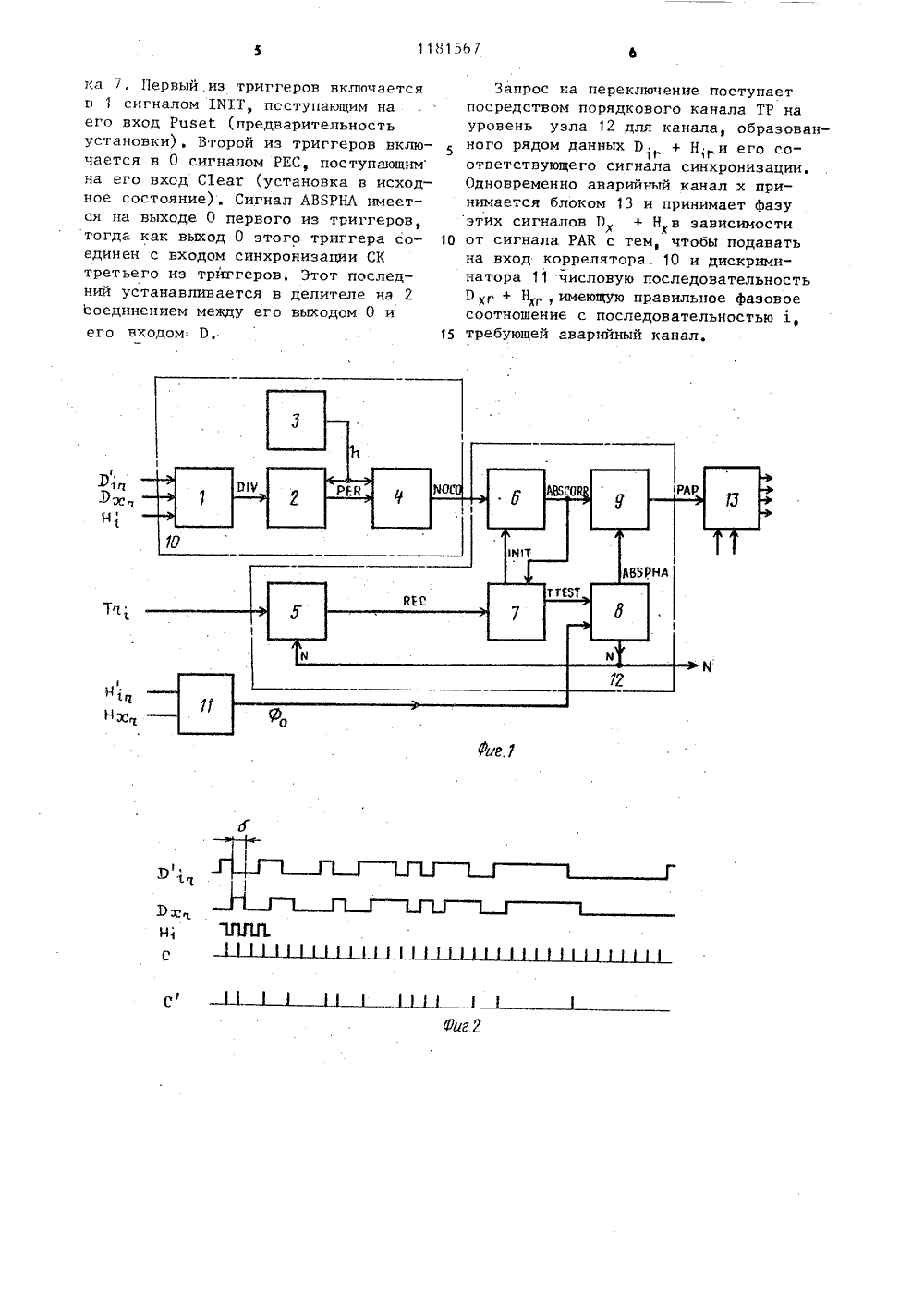

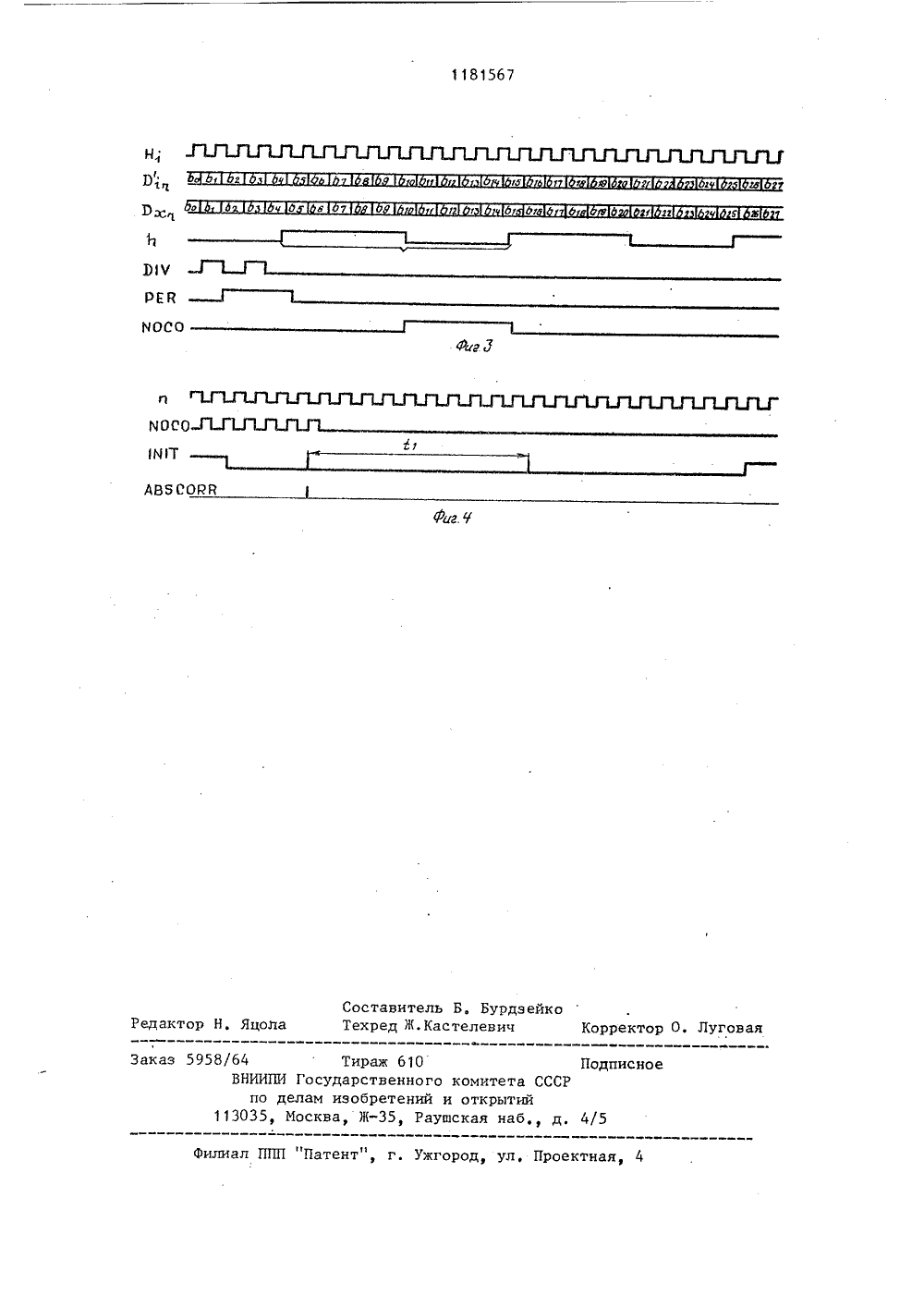

е коммю 79,у 79181Основсообще431, ртехники ний. М,; ис, 8.1,тся п авляю ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ( арль Анри Аби Анри Беренги( осьете Анонимн он (РК)(5 ) 1. УСТРОЙСТВО ФАЗИРОВАНИЯЧИС Х ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащ ервый блок сравнения, генератор импульсов, первый блок памяти,счетчик, блок фазовращателей, о тл и ч а ю щ е е с я тем, что, сцелью повышения достоверности передачи, в него введены второй блок памяти, элемент ИЛИ, второй счетчик,второй блок сравнения, решающийблок, фазовый дискриминатор, выходпервого блока сравнения подключенк первому входу первого блока памяти, выход которого подключен к первому входу второго блока памяти,выход генератора импульсов соединенс вторыми входами первого и второгоблоков памяти, выход второго блокапамяти соединен с первым входомпервого счетчика, выход которого подключен к первым входам элемента ИЛИи второго счетчика, выход элемента ИЛИ подключен к управляющему входублока фазовращателей, первый ивторой выходы второго счетчика подключены соответственно к второмувходу первого счетчика и к перв мувходу решающего блока, первый выходкоторого соединен с первым входомвторого блока сравнения, выход которого соединен с вторым входом второго счетчика, второй выход решающегоблока подключен к второму входу элемента ИЛИ, выход фазового дискриминатора подключен к второму входу решающего блока, входы первого блокасравнения, фазового дискриминатораи информационные входы блоков фазовращателей являются информационнымивходами устройства, вход второгоблока сравнения является управляющимвходом устройства, выходы блока фазовращателей являются информационнымивыходами устройства, первый выход решающего блока являе у р щимвыходом устройства.2 Устройство по п, 1, о т л ич а ю щ е е с я тем, что решающийблок содержит триггеры, выход первоготриггера подключен к первому входувторого триггера, второй вход которога подключен к его первому выходу,первые входы первого и третьего триггеров объединены и являются первымвходом решающего блока, вторые входыпервого и третьего триггеров объединены и являются вторым входам решающего блока, второй выход второготриггера является первым выходомрешающего блока, выход третьего триггера является вторым выходом решающего блока, 1181567 2Изобретение относится к цифровойпередаче информации и, в частности,к фазированию числовых последователь -ностей для обеспечения порядка. переключения, причем названные ряды со -держат сигналы идентичных данных исигнал синхронизации одной и той жечастоты,Цель изобретения - повышение достоверности передачи, 1 ОНа фйг, 1 изображено предлагаемоеустройство; на фиг. 2 - решающийблок, на. фиг, 3 и 4 - временные диаграммы работы устройства.Устройство содержит первый блок 1 15сравнения, первый блок 2 памяти, генератор 3 импульсов, второй блок 4 памяти, второй блок 5 сравнения, пер-.вый счетчик 6, второй счетчик 7, решающий блок 8, элемент ИЛИ 9,коррелятор 10, состоящий из блоков 1-4, фазовый дискриминатор 11, логическийузел 12, состоящий из блоков 5-9,и блок 13 фазовращателей. Решающийблок 8 содержит первый, второй и тре тий триггеры,Устройство работает следующим образом.Два ряда данных Р;. и Р г поступают издвух различныхканалов идолжныбыть одинаковыми, Устройство исследует несовпадение двух рядов данныхР. и Р , Сигнал синхронизации Н;,имеющий такую же номинальную частоту, что и сигналы синхронизации Н35и Н- названных рядов, но четко определенную фазу, задает работу блока 1, принимающего сигналы Р;г и Р.Блок 1 сравнпает предварительно синхронизированные сигналы Н РиР и подает представительный сигналР 1 (расхождение) испытания на совпадение данных, Для смещения одногосигнала по отношению к другому (фиг 2)моменты сравнения (сигнал С) соответ-,ствуют спадам сигнала синхронизацииН. . В некоторые моменты (сигнал С)этого сигнала синхронизации обнаруживают несовпадение двух сигналовданных Р и Р г, Другой сигнал негсовпадения Р 2 изображается приэтом ненулевым сигналом (неодинаковые биты Ь и Ь, на фиг. 3),Генератор 3 намного ниже ритма числовых последовательностей подает сигнал прямоугольной формы Ь, определяющий пакет битов постоянной длины (р/р - целое число), соответствующей периоду этого сигнала ЬСигнал 1 У несовпадения закладывается в блок 2 до конца пакета, определяемого Ь, который также накладывается на него, На выходе блока 2 подается сигнал РЕК (ошибочный пакет), указывающий на то, что пакет битов содержит по меньшей мере одно несовl падение между данными Рг и Р, Таким образом, этот сигнал РЕК не реагирует на вторую ошибку, которая может существовать в том же пакете,В блоке 4 сигнал РЕК закладываетсяв память в течение продолжительности следующего пакета, подавая сигналЬ на вход блока 4.На выходе блока 4 импульс БОСО несовпадения равен 1 в течение заданного постоянного времени, если имеется по меньшей мере одно несовпадение данных в предшествующем пакете. Этопостоянное время испускания импульса БОСО должно быть действительно совместимо с работой медленной части устройства для корреляции данных. Описанная часть, образованная блоками 1 - 4, работает с частотой Н и является "быстрой" частью, уменьшенной сознательно, ввиду потребления энергии.Сигнал БОСО подается на вход счетчика 6, который считает импульсыБОСО между двумя импульсами, смещенными на 1 от сигнала 1 И 1 Т (инициализация), подаваемыми счетчиком 7.Если счетчик 6 подходит к своему максимальному счету о, который являетсязаданной величиной до поступлениядругого импульса сигнала 1 И 1 Т, онподает импульс отсутствия корреляцииАВВСО 1% на выходе (фиг. 4), Если импульс АВБСООВК подается до окончания промежутка времени, то счетчик 7 инициализируется. В этом случае и когда счетчик 7 подходит к С импульс 1 И 1 Т инициализирует счетчик 6, Время С, выбирается для распознавания отсутствия корреляции на последовательности с наименьшим содержанием переходов. В самом деле, данные, передаваемые обычно по радиорелейным линиям, содержат растр собственно данных и некоторое число слов или битов для систематического включения, Таким образом, частота сигнала Ь, след. длина пакета, является одним из параметров, позволяющихоптимизиро - вать работупредлагаемого коррелятора.1181567 Длина пакета должна учитывать содержание переходов рассматриваемых данных, а также их временное распределение, На фиг, 3 изображен частный случай, когда длина р пакета равна 10 битам.Параметр о, подсчитывающий импульсы БОСО между двумя импульсами 101 Т, выбирается таким образом, чтобы предлагаемый коррелятор не реагировал 10 на ошибки, которые могут существоватьна данных, и для того, чтобы рп былосовместимо с допустимыми величинамипульсации,Такой коррелятор 10 успешно приме няется в случае запроса на коммутациюпучков для разрешения запроса Т, накоммутацию, исходящего иэ канала порядка 1, означающего, что каналтребует помощи или, если он уже имеет ее, что он не желает больше иметьее. Сигнал Т находится в 1, когдаканал д находится в нормальном приеме, и в О, когда каналу д оказывается помощь. Назовем х аварийный канал. Тогда ряд Р , соединенный сог 9своим синхронизатором Н, сравнивается с рядом 0, соединенным со своимсинхронизатором Н,Дискриминатор 11 фазы принимаетсигналы синхронизации Н и Н;и подает на выходе представительный сигнал фо смещения фазы между синхро низаторами двух последовательностей.Таким образом, пока коррелятор10, включающий элементы 1, 2, 4, 335(фиг. 1)., испытывает данные на несовпадения, дискриминатор 11 задаетрежим смещения фазы синхронизаторовна входе решающего блока 8.Если ф = О, имеется неприемлемоесмещение фазы, так как оно слишкомбольшое, и блок 8 подает сигналАВБРНА, означающий отсутствие фазирования синхронизаторов двух цифравых рядов, на входе элемента ИЛИ 9,который в свою очередь подает навыходе импульс РАК (шаговый), означающий плохую фазу.,3Блок 8 подает также, когда фаза 50плохая, ненулевой Сигнал К, которыйподается на вход блока 5, которыйпринимает также сигнал Тзапросана переключение канала х, причемЯ = 0 означает, что сигналы находятся в фазе. Сигнал Ю указывает на то,в каком состоянии. находится переключение; если Я = 1, канал д находит 4ся в режиме нормальной передачи, если И = О, действует аварийный канал х. Когда Тг,и Я находятся в раз.личном состоянйй блок 5 подает сигнал КЕС (поиск), разрешающий поиск правильного положения фазы аварийного канала. Сигнал КЕС подается на вход счетчика 7 и служит для его инициализации, Счетчик 6 несовпадений считает импульсы КОСО между двумя импульсами 101 Т, подаваемыми этим счетчиком 7 и если он подходит к своему максимальному счету и до поступления 1 И 1 Т,он испускает импульс об отсутствии корреляции АВБСОКК на выходе, означающий, что данные находятся в плохом фазовом соотношении. Этот сигнал АВБСОКК, также подаваемый на вход элемента ИЛИ 9, также позволяет подавать импульс РАР на выходе.Сигнал АВБСОКК включает счетчик 7. Если к концу времени й не было дру 1гого импульса АВБСОКК, то счетчик 7 подает импульс ТТЕБТ на вход блока 8, который может при этом в зави" симости от состояния ф, подаваемого дискриминатором 11, освобождать импульс РАР на выходе элемента ИЛИ 9, накладывая на него представительный импульс АВБРНА плохой фазы, Таким образом, коррелятор 10 позволяет очень быстро испытать (он работает в ритме Н;) фазовую связь и зачастую плохую связь между двумя цифровыми рядами, не ожидая того, что дискриминатор 11, более медленный, выдаст свой результат. Выбор о импульсов, позволяющих подавать РАР, таков, что можно защититься от возможных ошибок, а также от дребезжания. Минимальное время испытания данных на одном положении равно след. рИ ф где ц равно периоду сигнала Н,.Наоборот, хороший результат по данным может быть еще подтвержден фазовым испытанием ф в конце времени й Промежутки времени С испытания следуют один за другим и выби" раются продолжительностью, совместимой с технологиями блоков коррелятора 10 и дискриминатора 11. В решающем блоке 8 имеются три триггера, которые принимают смещение фазы ф , подаваемое дискриминатором 11 на их входы Р, а также сигнал ТТЕБТ, поступающий с выхода счетчи 118156 1Ка 7, 11 ервый,из триггеров включаетсяв 1 сигналом 1 МХТ, псступающим наего вход РцзеС (предварительностьустановки). Второй иэ триггеров включается в О сигналом РЕС, поступающимна его вход С 1 еаг (установка в исходное состояние), Сигнал АВБРНА имеется па выходе О первого иэ триггеров,тогда как выход О этого триггера соединен с входом синхронизации СКтретьего из триггеров, Этот последний устанавливается в делителе на 2соединением между его выходом О иего входом, Э,Запрос на переключение поступаетпосредством порядкового канала ТР науровень узла 12 для канала, образованного рядом данных О, + Н и его соответствующего сигнала синхронизации.Одновременно аварийный канал х принимается блоком 13 и принимает фазуэтих сигналов Р + Н в зависимости 10 от сигнала РАК с тем, чтобы подаватьна вход коррелятора 10 и дискриминатора 11 числовую последовательностьЭ г + Н,имеющую правильное фазовоесоотношение с последовательностью 15 требующей аварийный канал.1181567 ю б ду НОСО мого ДВБСОВ Фиг. 9 Составитель Б, БурдзейкоТехред Ж.Кастелевич Корректор О. Луговая Редактор Н, Яцола Подписное Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4 Заказ 5958/64 Тираж 610ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д, 4/5

СмотретьЗаявка

3437215, 05.05.1982

Сосьете Аноним де Телекоммюникасьон

ШАРЛЬ АНРИ АБ ДЕР АЛЬДЕН, ПЬЕР АНРИ БЕРЕНГИЕР

МПК / Метки

МПК: G08C 19/16

Метки: последовательностей, фазирования, числовых

Опубликовано: 23.09.1985

Код ссылки

<a href="https://patents.su/5-1181567-ustrojjstvo-fazirovaniya-chislovykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство фазирования числовых последовательностей</a>

Предыдущий патент: Устройство для автоматического поддержания уровня воды в резервуарах (его вариант)

Следующий патент: Устройство для отображения телетекста на экране телевизионного приемника

Случайный патент: Гусеничный движитель транспортного средства