Дешифратор интервально-временных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1120485

Автор: Тырков

Текст

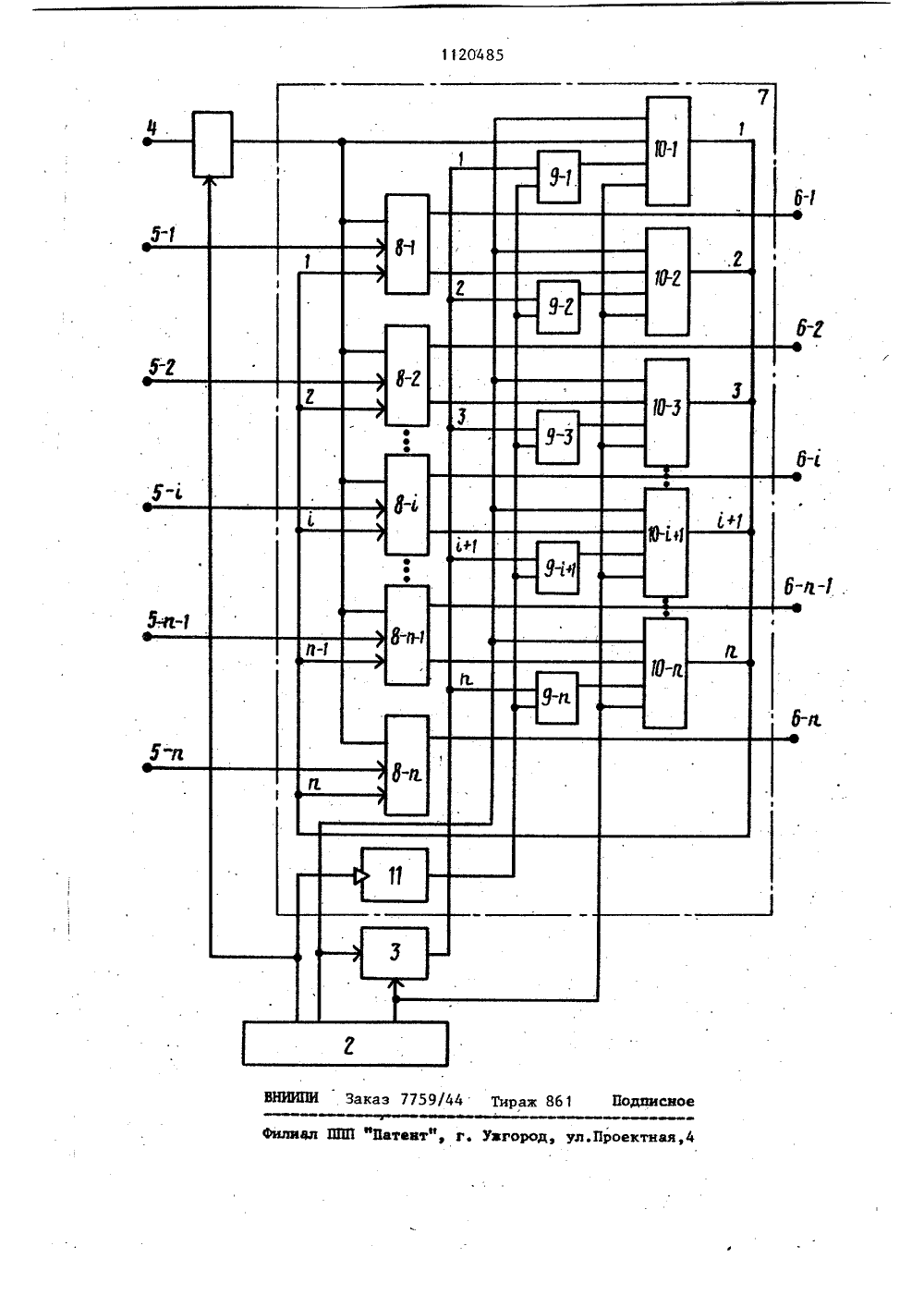

СОЮЗ СОВЕТСКИХсаицъютаисниРЕСПУБЛИК З 1 Я) Н 03 К 13/258 ОПИСАНИЕ ИЗОБРЕТЕНИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПЬ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54)(57) 1. ДЕ 1 ПИФРАТОР ИНТЕРВАЛЬНОВРЕИЕННЫХ СИГНАЛОВ, содержащий ли нию задержки, вход которой соеди- нен с входом дешифратора, и блок обработки, вход которого соединен с выходом линии задержки, а выходы подключены к выходам дешифратора, о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных воэможностей, в него введены блок синхронизации, постоянное запоминающее устройство и шины настройки, причем тактовый выход блока синхронизации соединен с тактовыми входами блока обработки и линии задержки, выход управления блока синхронизации соединен с входами управлении постоянного запоминающего устройства и блока обработки, выход адресов блока синхронизации подключен к адресному входу постоянного запоминающего устройства и адресному входу блока обработки, шины настройки соединены с входами установки порога блока,.ЯО 1120485 А обработки, а выходы постоянного запоминающего устройства - с входами кодов интервалов блока обработ- ки.2. Дешифратор по п,1, о т л ич а ю щ и й с я тем, что блок обработки содержит п -групп, каждая из которых состоит из соединечных последовательно сумматора модификации адреса, оперативного запоминающего устройства и сумматора, а также счетчик адресов, выход которого соединен с первыми входами всех сумматоров модификации адреса вторые входы которых.подклюО чены к соответствующим входам кодов 19 интервалов блока обработки, входы установки порога которого соединены с вторыми входами соответствующих сумматоров, третьи входы которых подключены к входу блока абра-фС ботки, а .первые выходы - к соответствующим выходам блока обработки,при этом второй выход сумматора -й группы, кроме последней, соединен с вторым входом оперативного запоминающего устройства (+1)-й группы, кроме первой, второй вход оперативного запоминающего устройства которой соединен с входом блока обработки, кроме того, третьи входы всех оперативных запоминающих , устройств соединены с вхбдом управления блока обработки, а четвер- фр тые входы - с адресным входом блока обработки, тактовый вход которого подключен к входу счетчика .адресов.1120485 1Изобретение относится к импульсной, технике и может бьггь использовано при декодировании интервальновременных кодов в системах передачиданных.Известен дешифратор интервальновременных сигналов, состоящий иэ линии задержки, тактового генератораи блока обработки, входы которогоподключены к выходам линии задержки, а выход соединен с выходом устройства 1 1.Недостатком дешифратора являются ограниченйые функциональные воэможности.Наиболее близким к изобретениюпо технической сущности являетсядешифратор интервально-временныхсигналов, содержащий линию задержкии блоки обработки, входы которыхсоединены с соответствующими выходами линии задержки, а выходы подключены к выходам дешифратора, входлинии задержки подключен к входудешифратора 2 3.Недостатком известного дешифратора являются ограниченные Функциональные воэможности, обусловленныеотсутствием возможности перенастройки устройства на другой ансамбльсигналов,11 ель изобретения - расширениефункциональных возможностей.1 ель достигается тем, что в дешифратор интервально-временных сигналов, содержащий линию задержки,вход которой соединен с входом дешифратора и блок обработки, вход которого соединен с выходом линии задержки, а вьиоды подключены к выходам дешифратора, введены блок синхронизации, постоянное запоминающее устройство и шины настройки,причем тактовый выход блока синхронизации соединен с тактовыми входа"ми блока обработки и линии задержки,выход управления блока синхронизациисоединен с входами управления постоянного запоминающего устройства иблока обработки, выход адресовблока синхронизации подключен кадресному входу постоянного запоминающего устройства и адресному входу блока обработки, шинынастройки соединены с входами установки порога блока обработки,а выходы постоянного запоминающегоустройства - с входами кодов интервалов блока обработкИ. 5 10 15 20 25 30 35 40 45 50 55 2Кр оме того, блок о бработ ки содержит и групп, каждая из которыхсостоит иэ последовательно соединенных сумматора модификации адреса,оперативного запоминающего устройства и сумматора, а также счетчикадресов, вьиод которого соединенс первыми входами всех сумматоровмодификации адреса, вторые входыкоторых подключены к соответствующим входам кодов интервалов блокаобработки, входы установки порогакоторого соединены с вторыми входами соответствующих сумматоров,третьи входы которых подключены квходу блока обработки, а первыевыходы - к соответствующим выходам блока обработки, при этомвторой выход сумматора -ой группы, кроме последней, соединен свторым входом оперативного запоминающего устройства (1+ 1)-й группы, кроме первой, второй входоперативного запоминающего устройства которой соединен с входомблока обработки, кроме того, третьивходы всех оперативных запоминающих устройств соединены с входом управления блока обработки, а четвертые входы - с адресным входомблока обработки, тактовый вход которого подключен к входу счетчикаадресов,На чертеже приведена функциональ.ная схема предлагаемого дешифратора,Дешифратор интервально-временного сигнала состоит из цифровой линии 1 задержки, блока 2 синхронизации, постоянного запоминающегоустройства (ПЗУ) З,входа 4 видеоимпульсов, шин 5.1-5,ь настройки,п выходов 6.1-б,п блока 7 обработки, причем блок 7 обработки состоит иэ п групп, каждая из которыхсодержит сумматор 8.1-8. сумматор9,1-9,п модификации адреса, оперативноезапоминающее устройствоОЗУ) 10.1-10.п, а также счетчик 11адресов.Вход линии 1 задержки соединен свходом дешифратора, а вьиод - с вхбдом блока 7 обработки, выходы которого подключены к выходам дешифратора, тактовый вход блока 2 синхронизации сбединен с тактовыми входаии блока 7 и линии 1 задержки,выход управления блока 2 соединенс входами управления ПЗУ 3 и блока 71120485 3обработки, выход адресов блока 2 под 1 слючен к адресному входу ПЗУ 3 и адресному входу блока 7, шины 5,1-5,п настройки соединены с входами установки порога блока 7,а 5 выходы ПЗУ 3, - с входами кодов интервалов блока 7, 1-й сумматор 9 модификации адреса последовательно соединен с 1-ым ОЗУ 10 и -ым сумматором 8, выход счетчика 11 адресов соединен с первыми входами сумматоров 9 модификации адреса, вторые входы которых подключены соответственно к входам кодов интервалов блока 7, входы установки порога которого соединены с вторыми входами соответствующих .сумматоров 8, третьи входы которых подключены к входу блока 7, а первые выходы - к соответствующим выходам блока 7, второй выход 1-го сумматора 8, кроме последнего, соединен с вФорым входом ОЗУ 10.1-10. п,кроме первого, второй выход которого соединен с входом блока 7, третьи входы всех ОЗУ 10 соединены соответственно с входами управления блока 7, тактовый вход которого подключен к входу счетчика 11 адресов.- ожидаемая вероятностьпоявления импульса номер 1+ 1 в момент вре мени й + с.;- кодовый интервал междуи 1+1 импульсамисигнала;- число импульсов в сиг нале.Если Р+О%/1,где К - порогдешифратора, то Считается, что в момент времени 1 отдекодировался интервально-временной сигнал.20Производится отсчет времени.Дешифратор оперирует не дробнымзначениями вероятностей Р, а с целыми числами математических ожи- даний(2)В зависимости от числа импульсов в сигнале 6 на шины 5 настройки номер иустанавливается порог дешиФрации в дополнительном коде К = 2 - К, где г - разрядность сумматоров 8, на все предыдущие шины 5 устанавливаются нули, признак дешифрации сигнала 35снимается с соответствующего выхода 6.Дешифратор работает следующимобразом.В начальный момент все ОЗУ 10 40обнулены, а счетчик 11 адресов находится в произвольном состоянии. Блок2 синхронизации вьпает с выхода управления нулем сигнал считывания,который поступает на управляющий 45 вход ПЗУ 3 кодов интервалов, выходыПЗУ 3 закрываются и на первые входывсех сумматоров 9 модификации адреса поступают нули. Таким образом,в младшие разряды первых (адресных)входов ОЗУ 10 транслируется текущийадрес й с выходов счетчика 11. Садресных выходов блок 2 синхронизации выдает номер сигнала в ансамбле,который поступает на четвертые входы 55 Тстаршие разряды адресов) ОЗУ 1 О,тем самым обеспечивается запись ин Формации о видеоимпульсах сигналов в)непересекающиеся области ОЗУ 10 .На . Расширение функциональных возможностей .дешифратора заключается в том, что настройка дешифратора на новый ансамбль интервально-временных сигналов достигается установкой нового порога дешифратора по шинам настройки, смене постоянного запоминающего устройства, и не меняет структуру блока обработки и его связи. Сокращение числа отводов от линии задержки достигается тем, что данная структура дешифратора ориентирована на то, что дешифрациясигнала в блоке обработки производится последующиму алгоритмуЪ В каждый момент времени й вычисляется ожидаемая вероятность появления видеоимпульса номер +1 в момент времени+ Ф по рекурентнойформулефф;с( ф, . Р= Р, + О, (1: 1,2. 6-1), Р : ОИ+где Р,. - ожидаемая вероятностьпоявления видеоимпульсаномер 1 в момент времени й; О, если вндеоимпульса в момент временинет;1/Г если видеоимпульс в момент времени й присутствует;третий вход (управление считыванием(записью).ОЗУ 10 также поступает нулем сигнал считывания с блока 2 синхронизации, таким образом с выходов ОЗУ 10 по текущему адресу5 считывается значение матиматического ожидания ш,которое устанавливуется на первых входах сумматоров 8.1-8. н. На третьи входы (переносов) сумматоров 8 пОдается с выхода линии задержки признак наличия видеоимпульса и.Фс 1 О, если нет видеоимпульса;1, если есть видеоиьаульс,Вторые входы сумматоров 8.1-8.15 соедийены с шинами 5 установки порога дешифрации. Так как на все шины 5 с номерами 1 Ф-1 подается "0",то на первых выходах сумматоров 8 с номерами 1 Ф Г -1 устанавливается 20 значение математического ожидания1 фтп 1: щ + 0 а на сумматоре 8 с номерами 1 = 1 - 1,суммаЗ =1 п О +2 -1 сгТаким образом, если в- м + О больше порога Е, то на первом выходе (переноса) сумматора 8 с номером 1 -1 появится перенос и на шине 5 номер -1 установится признак дешифрации 30 кодирующей последовательности.Следующим тактом блок 2 синхроьизации выдает на управляющий выход сиг. нал записи уровнем единицы, Сигнал записи поступает на управляющий вход ПЗУ 3 и открывает выходы, коды интервалов 7;, характеризующие сигнал, параллельно поступают на вторые входы сумматоров 9 модификации адреса и на их выходах. образуется совокупность новых адресов Т =.С + ;. По этим адресам сигналом записи происходит запись математического ожидания в ОЗУ 10 номер 1+1 с первых выходов сумматора 8 номерВторой вход (данных).первого ОЗУ .10 соединен непосредственно с выходом линии 1 задержки, так как согласно выражениям (1) и (2)1+а:о2 1 1После записи информации в ОЗУ цикл дешифрации одного сигнала заканчивается. Следующим тактом блок 2 синхрони- зации на выходах адресов устанавливает номер следующего сигнала. Номер сигнала поступает на адресный вход ПЗУ 3, тем самым выбирается набор кодов интервалов, характеризующий этот сигнал. Номер сигнала также поступает на старшие разряды адресных входов ОЗУ 10 тем самым переключая рабочую область ОЗУ. Затем циклы считывания и записи повторяют. ся до тех пор, пока не исчерпывается весь ансамбль. После этого блок 2 синхронизации выдает на тактовый выход синхроимпульс и производится отсчет времени счетчиком 11 адресов.Введение ПЗУ, блока обработки указанной структуры, позволяющей производить перенастройку дешифратора на другой ансамбль сигналов простой сменой ПЗУ, дает возможность путем последовательной обработки декодировать ансамбль интервально-временных сигналов с помощью одного блока обработки.1120485 ВНЮПЗИ Заказ УУ 59/44Тираж 86 ад ППП евтф жгоро о Проектная,4

СмотретьЗаявка

3566822, 17.03.1983

ПРЕДПРИЯТИЕ ПЯ А-1431

ТЫРКОВ СЕРГЕЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 13/258

Метки: дешифратор, интервально-временных, сигналов

Опубликовано: 23.10.1984

Код ссылки

<a href="https://patents.su/5-1120485-deshifrator-intervalno-vremennykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Дешифратор интервально-временных сигналов</a>

Предыдущий патент: Генератор переменной частоты

Следующий патент: Усилитель фототока

Случайный патент: Устройство для испытания воздухоочистителей