Устройство для измерения сопротивления резисторов, образующих замкнутую цепь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

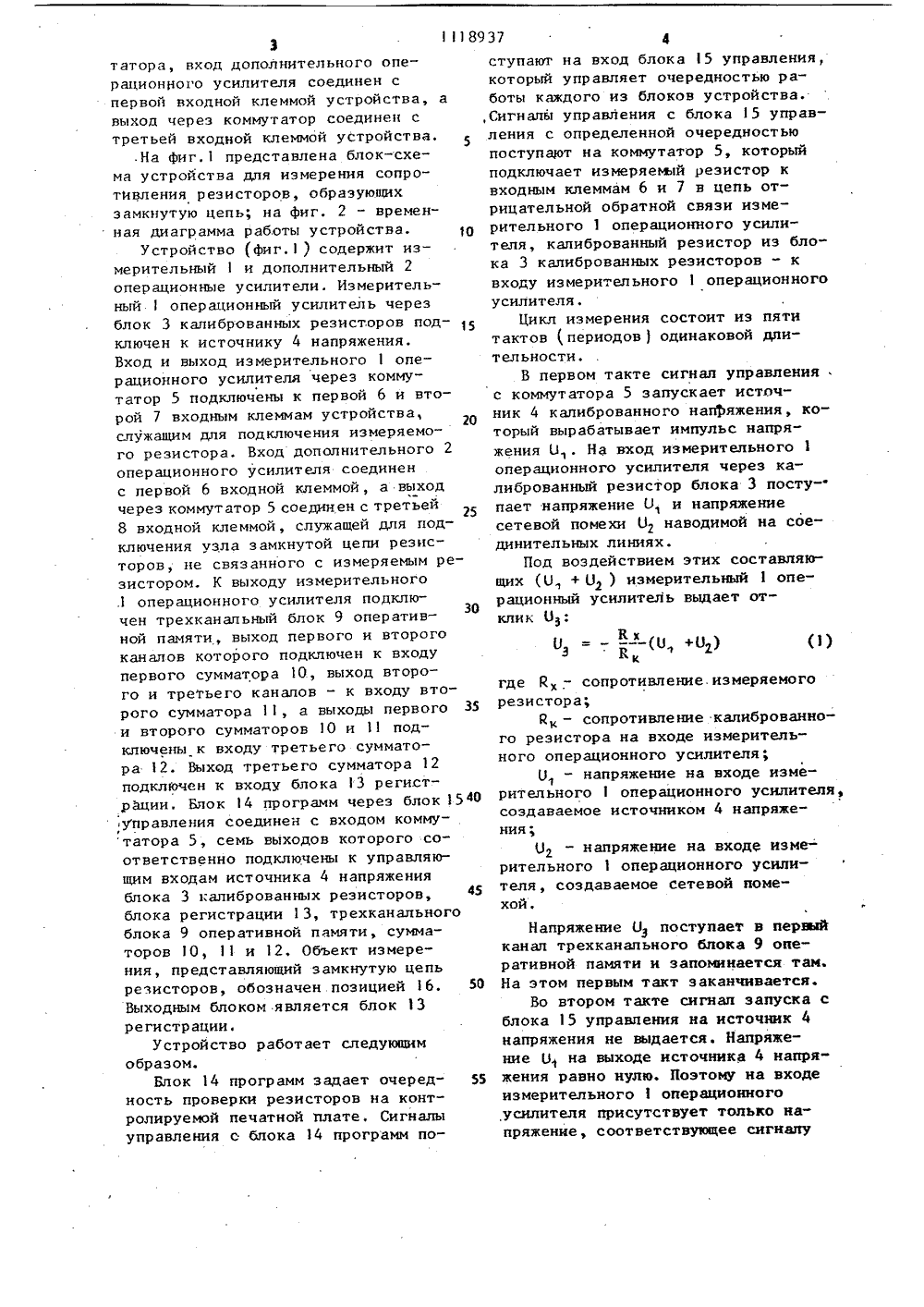

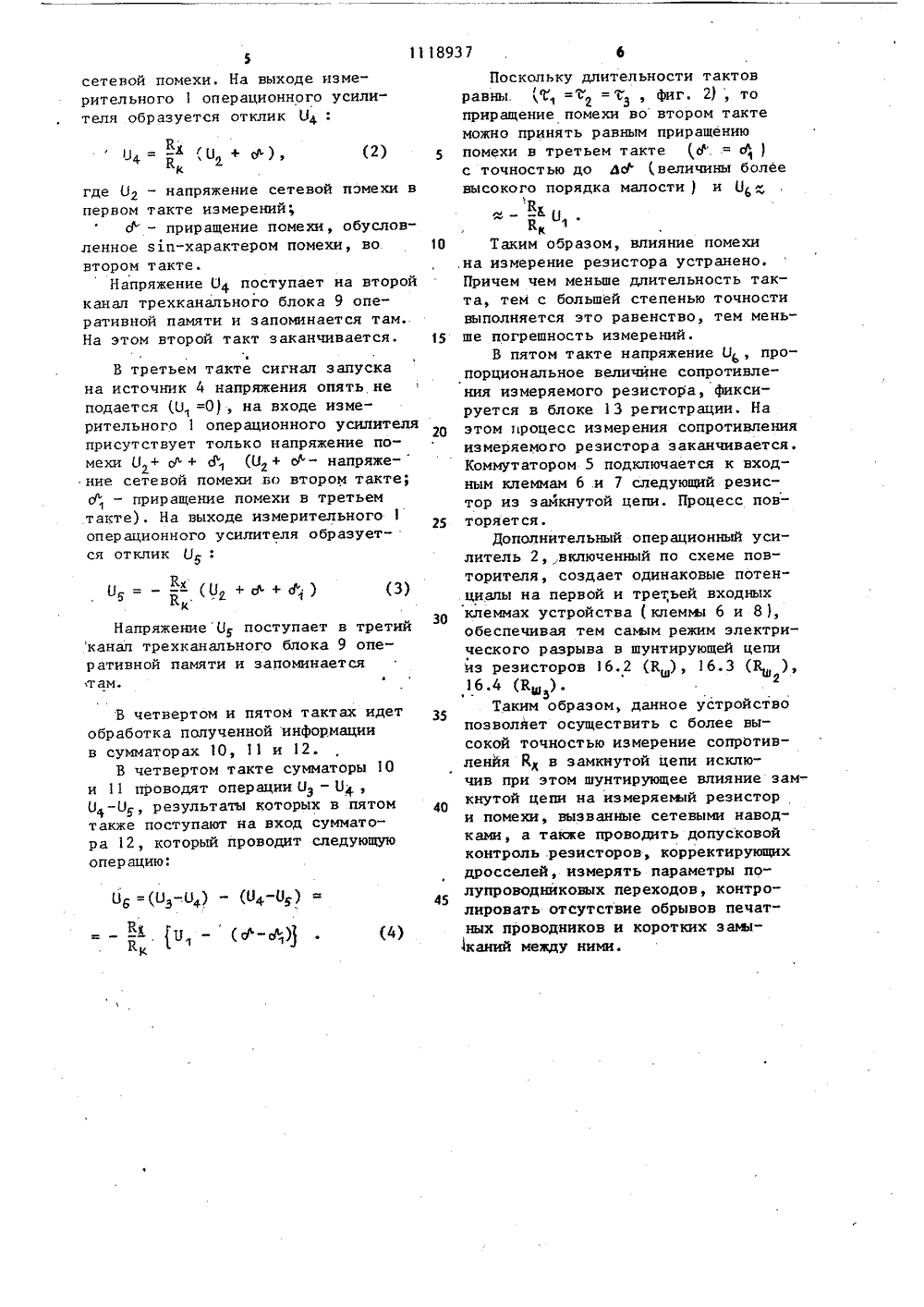

СОЮЗ СОВЕТСКИХСЭЮЛПМЕиРЕСПУБЛИН 8937 ю а 01 В. 27/00 О НИЕ ИЗОБРЕТЕН ВТОРСИОМУ СВИДЕТЕЛЬСТВУ(21) (22) (46) (72) (53) (56) У 71 Андр оно тво СССР29.08.78,о СССР27. 11. 78 2 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ 3614412/18-2127.06,8315.О. 84. Бюл.У 38В.С.Полынкин и П.И.621.37.033(088.8).1. Авторское свидетель804, кл. С 01 К 27 /00,Авторское свидетельст567, кл. С 01 К 27/00,отип).(54) (57) УСТРОЙСТВО ЛЯ ИЗМЕРЕНИЯСОПРОТИВЛЕНИЯ РЕЗИСТОРОВ, ОБРАЗУЮЩИХ ЗАМКНУТУЮ ЦЕПЬ, содержащее источник напряжения, аыход которогочерез блок калиброванных резисторовподключен к входу измерительногооперационного усилителя, вход и выход которого через коммутатор соединены с первой и второй входнымиклеммамй устройства, служащимидля подключения измеряемого резистора,дополнительный операционныйусилитель, блок регистрации, блокпрограмм, выход которого через блокуправления соединен с входом коммутатора, три выхода которого соответственно подключены к управляющимвходам источника напряжения, блокакалиброванных резисторов и блока регистрации, третью входную клемму устройства, служащую для подключения узла замкнутой цепи резисторов, не связанного с измеряемым резистором, отличающееся тем, что, с целью повьппения точности измерений, введены трехканальный блбк оперативной памяти и три сумматора, при чем входы всех трех каналов блока оперативной памяти объединены и подключены к выходу измерительного операционного усилителя, выходы первого и второго каналов блока оперативной памяти подключены к входу пер вого сумматора, выходы второго и третьего каналов блока оперативной памяти . - к. входу второго сумматора, а выходы первого и второго сумматоров - к входам третьего сумматора, выход которого подключен к блоку регистрации, управляющие входы трехканального блока оперативной памяти и сумматоров подключены соответственно к четвертому, пятому, шестому и седьмому выходам коммутатора, вход дополнительного операционного усилителя соединен с первой входной клеммой устройства, а выход через коммутатор соединен с третьей вход,ной клеммой устройства.Изобретение относится к измерению электрических величин, в частности к измерению элементов цепей с сосредоточенными постоянными, и может быть использовано для быстродействующего автоматического контроля радиокомпонентов радиоэлектронных схем, собранных на печатных платах в условиях массового производства.Известно устройство для измере О ния сопротивления резисторов, образующих замкнутую цепь, содержащее источник напряжения, подключенный через калиброванный резистор к входным зажимам для подключения измеряемого резистора, измерительный прибор, подключенный к этим же зажимам, повторитель сигнапа, неинвертирующий вход которого подключен к этим же зажимам, повторитель сигнала, неинвертирующий вход которого подключен к входному зажиму, а выход - к узлу замкнутой цепи резисторов, несвязанному с измеряемым резистором 11.Равенство потенциалов между входом и выходом повторителя позволяет устранить шунтирующее влияние резисторов замкнутой цепи на измеряемый резистор и таким образом повысить точность проводимых измерений.ЭО Однако погрешность измерений, свя- . занная с наличием сетевых помех, ,в данном устройстве не учитывается что приводит к невысокой точности измерений.Наиболее близким техническим решением к изобретению является устройство для измерений сопротивления резисторов, образующих замкнутую цепь, содержащее три входные клеммы, основной измерительный опеО рационный усилитель, вход которого через блок калиброванных резисторов подключен к выходу источника напряжения, вход и выход измерительного операционного усилителя через комму-, 45 татор соединены с первой и второй входными клеммами устройства, служащими для подключения измеряемого резистора, дополнительный операционный усилитель, блок регистрации, блок 50 программ, соединенный через блок управления с входом коммутатора, три выхода которого подкл 0 чены соответственно к управляющим входам источника напряжения, блока калиброванных 55 резисторов и блока регистрации, блок резисторов, включенньй между входом 1 и выходом дополнительного операционного усилителя, вход которого соединен с блоком регистрации и через коммутатор с третьей входной клеммой устройства, служащей для подключения узла замкнутой цепи резисторов, непосредственно несвязанного с измеряемым резистором, управляющий вход блока резисторов под-, ключен к четвертому выходу коммутатора 21.Однако известное устройство из-за наличия сетевых помех не обеспечивает необходимой точности измерений.Цель изобретения - повышение точности измерений.Поставленная цель достигается тем, что в устройство для измерения сопротивления резисторов, образующих замкнутую цепь, содержащее источник напряжения, выход которого через блок калиброванных резисторов подключен к входу измерительного операционного усилителя, вход и выход которого через коммутатор соединены с первой и второй входными клеммами устройства, служащими для подключения измеряемого резистора, дополнительный операционный усилитель, блок регистрации, блок программ, выход которого через блок управления соединен с входом коммутатора, три выхода которого соответственно подключен к управляющим входам источника напряжения, блока калиброванных резисторов и блока ре - гистрации, третью входную клемму устройства, служащую для подключения узла замкнутой цепи резисторов, не связанного с измеряемым резистором, введены трехканальный блок оперативной памяти и три сумматора, причем входы всех трех каналов блока Ьперативной памяти объединены и под -ключены к выходу измерительногооперационного усилителя, выходы первого и второго каналов блока оперативной памяти подключены к входупервого сумматора, выходы второгои третьего каналов блока оперативной памяти - к входу второго сумматора, а выходы первого и второго сумматоров - к входам третьего сумматора, выход которого подключен к блоку регистрации, управляющие входы трехканального блока оперативной памяти и сумматоров подключены соответственно к четвертому, пятому,шестому и седьмому выходам комму1118937 3татора, вход дополнительного операционного усилителя соединен с первой входной клеммой устройства, а выход через коммутатор соединен с третьей входной клеммой устройства,.На фиг.1 представлена блок-схема устройства для измерения сопротивления резисторов, образующих замкнутую цепь; на фиг. 2 - временная диаграмма работы устройства. 10Устройство (фиг,1) содержит измерительный 1 и дополнительный 2 операционные усилители. Измерительныйоперационный усилитель через блок 3 калиброванных резисторов подключен к источнику 4 напряжения. Вход и выход измерительного 1 операционного усилителя через коммутатор 5 подключены к первой 6 и второй входным клеммам устройства, служащим для подключения измеряемого резистора. Вход дополнительного 2 операционного усилителя соединен с первой б входной клеммой, а выход через коммутатор 5 соединен с третьей 8 входной клеммой, служащей для подключения узла замкнутой цепи резисторов, не связанного с измеряемым резистором. К выходу измерительного .1 операционного усилителя подклю 30 чен трехканальный блок 9 оперативной памяти, выход первого и второго каналов которого подключен к входу первого сумматора 10, выход второго и третьего каналов - к входу второго сумматора 11, а выходы первого 35 и второго сумматоров 1 О и 11 подключены к входу третьего сумматора 12. Выход третьего сумматора 12 подключен к входу блока 13 регистрации, Блок 14 программ через блок 15"0 управления соединен с входом комму- Гтатора 5, семь выходов которого соответственно подключены к управляющим входам источника 4 напряжения блока 3 калиброванных резисторов, блока регистрации 13, трехканального блока 9 оперативной памяти, сумматоров 10, 11 и 12. Объект измерения, представляющий замкнутую цепь резисторов, обозначен позицией 16. 50 Выходным блоком является блок 13 регистрации.Устройство работает следующим образом.Блок 14 программ задает очеред ность проверки резисторов на контролируемой печатной плате. Сигналы управления с блока 14 программ поступают на вход блока 15 управления,который управляет очередностью работы каждого из блоков устройства.,Сигналы управления с блока 15 управления с определенной очередностьюпоступают на коммутатор 5, которыйподключает измеряемый резистор квходным клеммам 6 и 7 в цепь отрицательной обратной связи измерительного 1 операционного усилителя, калиброванный резистор из блока 3 калиброванных резисторов - квходу измерительного 1 операционногоусилителя,Цикл измерения состоит из пятитактов 1,периодоводинаковой длительности.В первом такте сигнал управленияс коммутатора 5 запускает источник 4 калиброванного натяжения, который вырабатывает импульс напряжения О . На вход измерительного 1операционного усилителя через калиброванный резистор блока 3 поступает напряжение О и напряжениесетевой помехи 02 наводимой на соединительных линиях.Под воздействием этих составляющих (О + 02 ) измерительный 1 операционный усилитель выдает отклик 0.0 = --- (О +0)КхВ.(1) где Й - сопротивление. измеряемогорезистора;й - сопротивление калиброванного резистора на входе измерительного операционного усилителя;О - напряжение на входе измерительного 1 операционного усилителя,создаваемое источником 4 напряжения;0 - налряжение на входе изме 2рительного 1 операционного усилителя, создаваемое сетевой помехой,Напряжение О поступает в пераюй канал трехканального блока 9 оперативной памяти и запоминается там. На этом первым такт заканчивается.Во втором такте сигнал запуска с блока 15 управления на источник 4 напряжения не выдается. Напряжение 0 на выходе источника 4 напряжения равно нулю. Поэтому на входе измерительного 1 операционного усилителя присутствует только напряжение, соответствующее сигналуТираж 710 Государственного елам изобретений Иосква, Ж, Р Подпа СССРтий

СмотретьЗаявка

3614412, 27.06.1983

ПРЕДПРИЯТИЕ ПЯ В-8657

ПОЛЫНКИН ВЛАДИМИР СЕРГЕЕВИЧ, АНДРОНОВ ПАВЕЛ ИВАНОВИЧ

МПК / Метки

МПК: G01R 27/00

Метки: замкнутую, образующих, резисторов, сопротивления, цепь

Опубликовано: 15.10.1984

Код ссылки

<a href="https://patents.su/5-1118937-ustrojjstvo-dlya-izmereniya-soprotivleniya-rezistorov-obrazuyushhikh-zamknutuyu-cep.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для измерения сопротивления резисторов, образующих замкнутую цепь</a>

Предыдущий патент: Цифровое устройство для воспроизведения фазовых сдвигов

Следующий патент: Устройство для измерения омических сопротивлений электрических цепей, находящихся под напряжением переменного тока

Случайный патент: Быстроразъемное соединение трубопроводов