Устройство для формирования и хранения вычетов чисел по модулю три

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1109755

Автор: Глебович

Текст

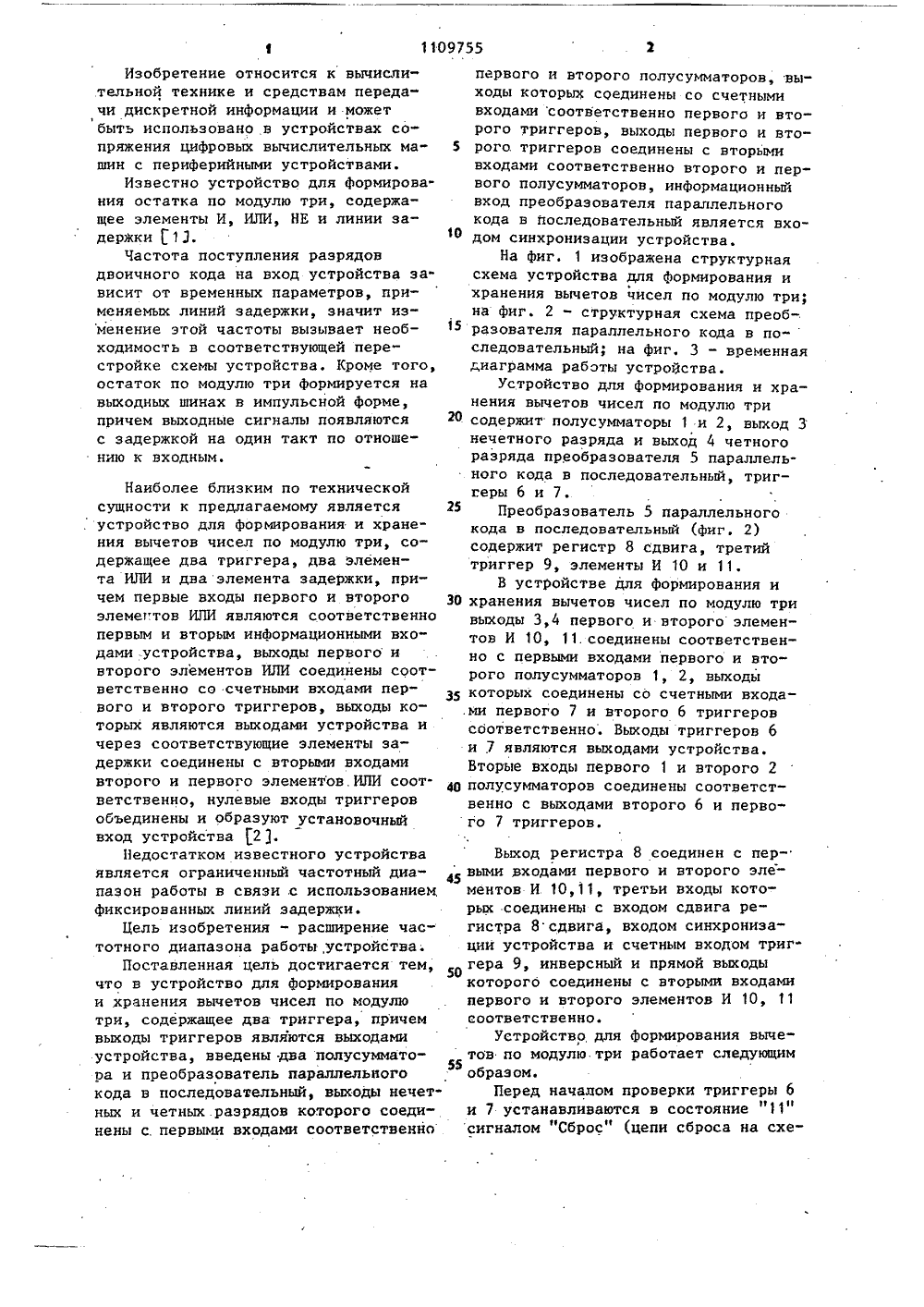

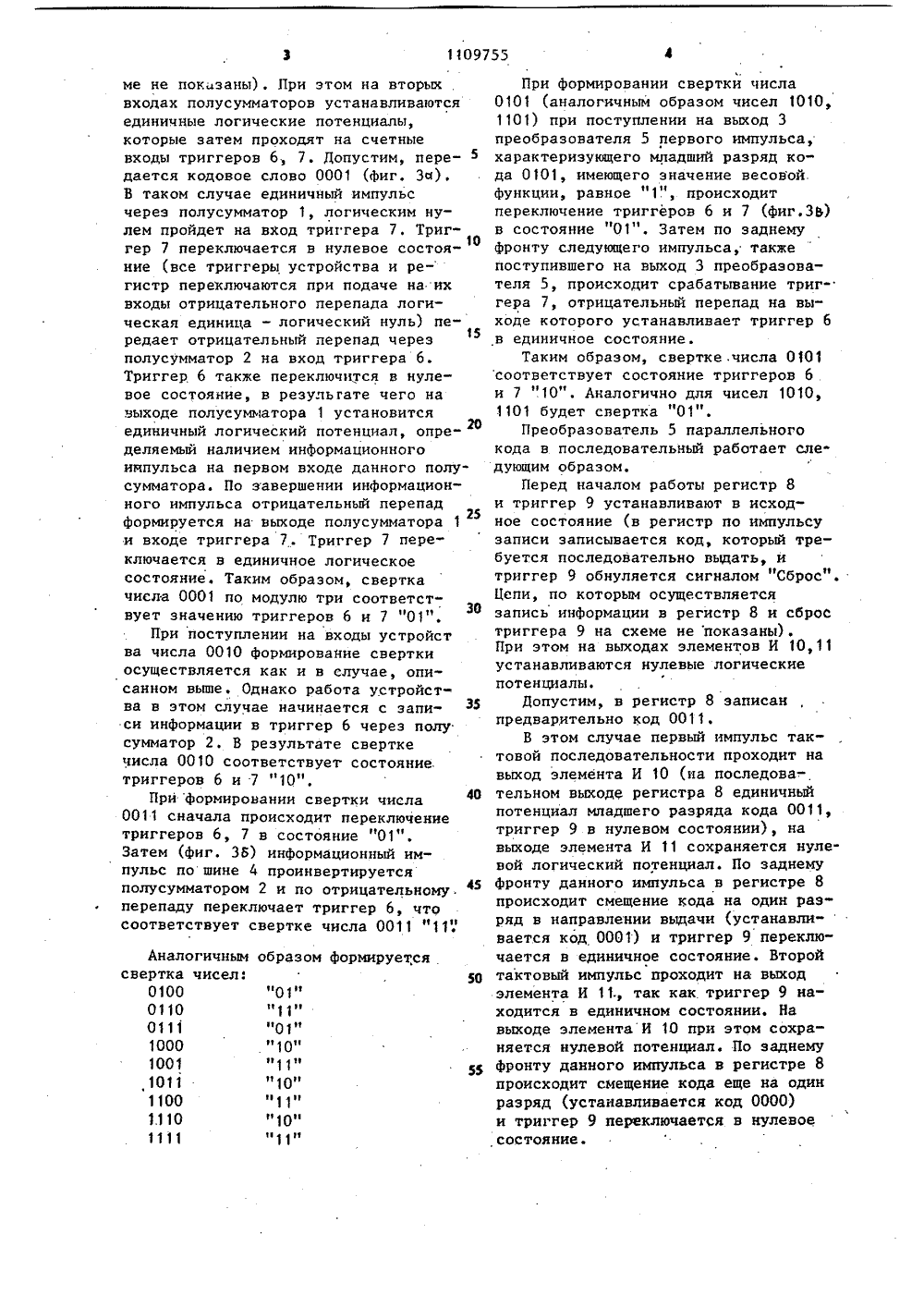

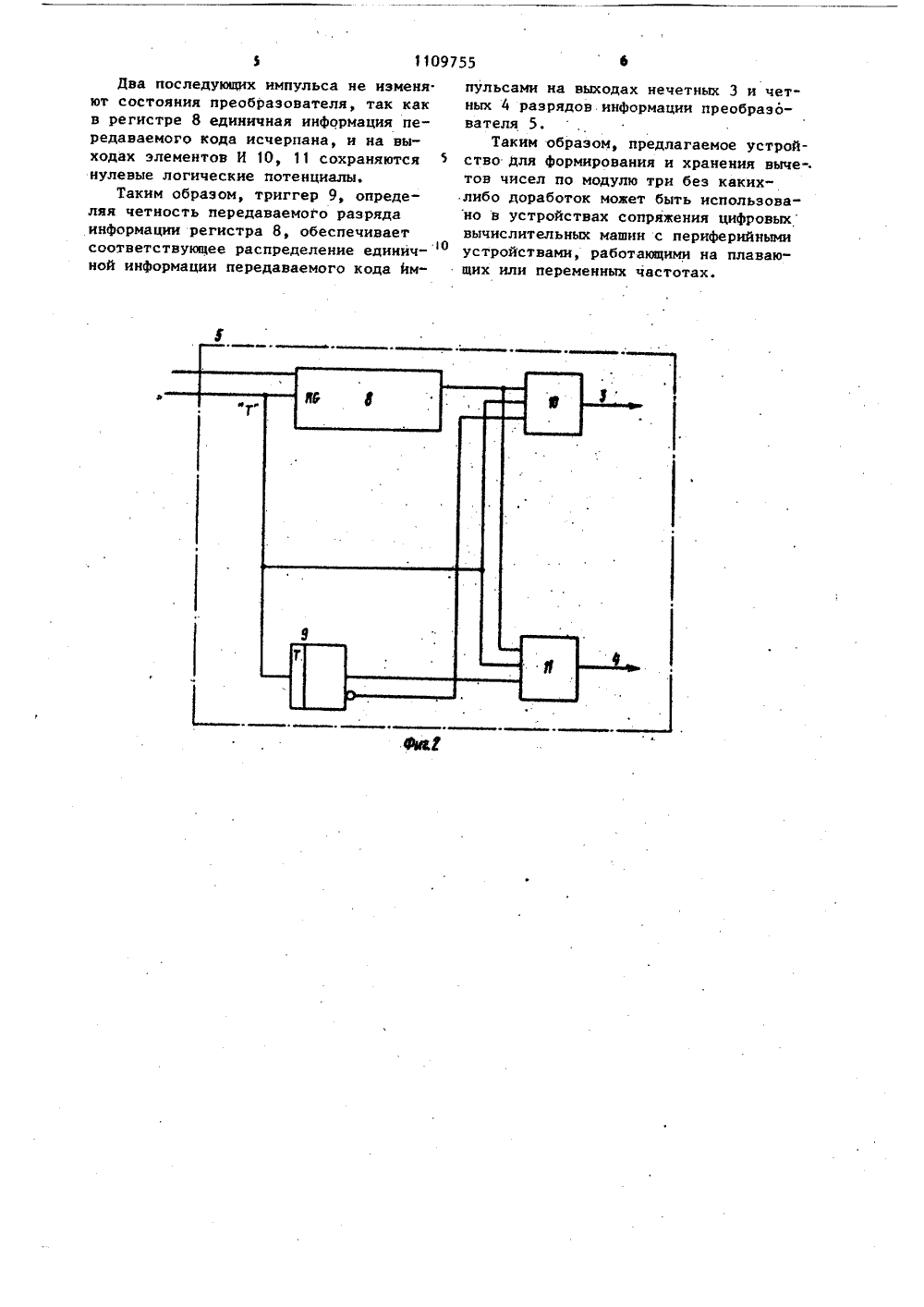

ОЮ 01) А зд) С 06 Р 11/10 ОПИСАНИЕ ИЗОБРЕТК АВТОРСКОМУ СВИДТЕЛЬСТВУ ьство ССС 1970. тво СССР 1973.ФОРМИРОВАНИЯ ПО МОДУЛ)б ера, причем выходами ще.е ся ния частич ГОСУДАРСТВЕННОЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕП.НИЙ И ОТНРЫТЮ(54)(57) УСТРОЙСТВО ДЛЯИ ХРАНЕНИЯ ВЫЧЕТОВ ЧИСЕЛТРИ, содержащее два триггвьмоды триггеров являютсяустройства, о т л и ч а ютем, что, с целью расшире ного диапазона работы устройства,в него введены два полусумматора ипреобразователь параллельного кодав последовательный, выходы нечетныхи четнйс разрядов которого соединеныс первыми входами соответственно первого и второго полусумматоров, выходыкоторых соединены со счетными входами соответственно первого и второготриггеров, выходы первого и второготриггеров соединены с вторыми входами соответственно второго и первогополусумматоров, информационный входпреобразователя параллельного кодав последовательный является входомсинхронизации устройства.Изобретение относится к вычислительной технике и средствам переда" чи дискретной информации и может быть использовано в устройствах сопряжения цифровых вычислительных ма" шин с периферийными устройствами.Известно устройство для Формирования остатка по модулю три, содержа" щее элементы И, ИЛИ, НЕ и линии задержки 11.Частота поступления разрядов двоичного кода на вход устройства за" висит от временных параметров, применяемых линий задержки, значит из" менение этой частоты вызывает необходимость в соответствующей пере" стройке схемы устройства, Кроме того, остаток по модулю три формируется на выходных шинах в импульсной форме, причем выходные сигналы появляются с задержкой на один такт по отношению к входным. Наиболее близким по техническойсущности к предлагаемому является устройство для формирования и хранения вычетов чисел по модулю три, со" держащее два триггера, два элемента ИЛИ и два элемента задержки, причем первые входы первого и второго элементов ИЛИ являются соответственно первым и вторым информационными вхо" дами .устройства, выходы первого и второго элементов ИЛИ соединены соответственно со счетными входами первого и второго триггеров, выходы которых являются выходами устройства и через соответствующие элементы задержки соединены с вторыми входами второго и первого элементов.ИЛИ сост. ветственно, нулевые входы триггеров объединены и образуют установочный вход устройства 2 1.Недостатком известного устройства является ограниченный частотный диапазон работы в связи .с использованием, фиксированных линий задержки.Цель изобретения - расширение частотного диапазона работы, устройства.Поставленная цель достигается тем, что в устройство для формирования и хранения вычетов чисел по модулю три, содержащее два триггера, причем выходы триггеров являются выходами устройства, введены два полусумматора и преобразователь параллельного кода в последовательный, выходы нечетных и четных. разрядов которого соединены с. первыми входами соответственно первого и второго полусумматоров, вы"ходы которых соединены со счетнымивходами соответственно первого и второго триггеров, выходы первого и вто 5 рого. триггеров соединены с вторымивходами соответственно второго и первого полусумматоров, информационныйвход преобразователя параллельногокода в последовательный является вхо 100 дом синхронизации устройства.На фиг, 1 изображена структурнаясхема устройства для формирования ихранения вычетов чисел по модулю три;на фиг. 2 - структурная схема преоб 15 разователя параллельного кода в по-следовательный; на фиг. 3 - временнаядиаграмма работы устройства.Устройство для Формирования и хранения вычетов чисел по модулю три200 содержит волусумматоры 1 и 2, выход 3нечетного разряда и выход 4 четногоразряда преобразователя 5 параллельного кода в последовательный, триггеры 6 и 7,Преобразователь 5 параллельногокода в последовательный (фиг. 2)содержит регистр 8 сдвига, третийтриггер 9, элементы И 10 и 11,В устройстве для формирования и30 хранения вычетов чисел по модулю тривыходы 3,4 первого и второго элементов И 1 О, 11. соединены соответственно с первыми входами первого и второго полусумматоров 1, 2, выходыЗ 5 которых соединены со счетными входа.ми первого 7 и второго 6 триггеровсоответственно. Выходы триггеров 6иявляются выходами устройства.Вторые входы первого 1 и второго 240 полусумматоров соединены соответственно с выходами второго 6 и первого 7 триггеров. Выход регистра 8 соединен с пер выми,входами первого и второго элементов И 10,11, третьи входы которых соединены с входом сдвига регистра 8 сдвига, входом синхронизации устройства и счетным входом триггера 9, инверсный и прямой выходыкоторого соединены с вторыми входамипервого и второго элементов И 10, 11соответственно,Устройство для формирования вычетов по модулю три работает следующимобразом.Перед началом проверки триггеры 6и 7 устанавливаются в состояние "11"сигналом "Сброс" (цепи сброса на схеобразом формируется Аналогичнымсвертка чисел:01000110011110001001101111001.1 101111 50 ме не показаны) . При этом на вторых .входах полусумматоров устанавливаютсяединичные логические потенциалы,которые затем проходят на счетныевходы триггеров 6, 7. Допустим, передается кодовое слово 0001 (Фиг. Зю).В таком случае единичный импульсчерез полусумматор 1, логическим нулем пройдет на вход триггера 7, Триггер 7 переключается в нулевое состоя 1 Оние (все триггеры устройства и регистр переключаются при подаче на ихвходы отрицательного перепада логическая единица - логический нуль) передает отрицательный перепад черезполусумматор 2 на вход триггера 6.Триггер 6 также переключится в нулевое состояние, в резульгате чего навыходе полусумматора 1 установитсяединичный логический потенциал, определяемый наличием информационногоияпульса на первом входе данного полусумматора. По завершении информационного импульса отрицательный перепадформируется на выходе полусумматора 125и входе триггера 7Триггер 7 переключается в единичное логическоесостояние. Таким образом, сверткачисла 0001 по модулю три соответствует значению триггеров б и 7 "01".30При поступлении на входы устройства числа 0010 формирование сверткиосуществляется как и в случае, описанном выше, Однако работа устройства в этом случае начинается с записи информации в триггер 6 через полусумматор 2. В результате сверткечисла 0010 соответствует состояниетриггеров 6 и 7 "10",При Формировании свертки числа0011 сначала происходит переключениетриггеров 6, 7 в состояние "01".Затем (фиг. 36) информационный импульс по шине 4 проинвертируетсяполусумматором 2 и по отрицательному. 45перепаду переключает триггер 6, чтосоответствует свертке числа 0011 "11". При Формировании свертки числа 0101 (аналогичным образом чисел 1010, 1101) при поступлении на выход 3 преобразователя 5 первого импульса, характеризующего младший разряд кода 0 101, имеющего значение весовой. функции, равное , происходит переключение триггеров 6 и 7 (фиг.ЗЬ) в состояние "01", Затем по заднему фронту следующего импульса, также поступившего на выход 3 преобразователя 5, происходит срабатывание триг" гера 7, отрицательный перепад на выходе которого устанавливает триггер б в единичное состояние.Таким образом, свертке .числа 0101 соответствует состояние триггеров б . и 7 "10". Аналогично для чисел 1010, 1101 будет свертка "01".Преобразователь 5 параллельного кода в последовательный работает сле" дующим образом.Перед началом работы регистр 8 и триггер 9 устанавливают в исходное состояние (в регистр по импульсу записи записывается код, который требуется последовательно выдать, и триггер 9 обнуляется сигналом "Сброс". Цепи, по которым осуществляется запись информации в регистр 8 и сброс триггера 9 на схеме не показаны). При этом на выходах элементов И 10, 11 устанавливаются нулевые логические потенциалы.Допустим, в регистр 8 записан предварительно код 0011.В этом случае первый импульс тактовой последовательности проходит на выход элемента И 10 (иа последовательном выходе регистра 8 единичный потенциал младшего разряда кода 0011, триггер 9 в нулевом состоянии), на выходе элемента И 11 сохраняется нулевой логический потенциал. По заднему фронту данного импульса в регистре 8 происходит смещение кода на один разряд в направлении выдачи (устанавли" вается код 0001) и триггер 9 переключается в единичное состояние. Второй тактовый импульс проходит на выход элемента И 11 так как. триггер 9 находится в единичном состоянии. На выходе элемента И 10 при этом сохраняется нулевой потенциал. По заднему фронту данного импульса в регистре 8 происходит смещение кода еще на один разряд (устанавливается код 0000) и триггер 9 переключается в нулевое состояние.1109755Два последующих импульса не изменя. пульсами на выходах нечетных 3 и чет" ют состояния преобразователя, так как ных 4 разрядов информации преобразов регистре 8 единичная информация пе- вателя 5.редаваемого кода исчерпана, и на вы- Таким образом, предлагаемое устрой- ходах элементов И 10, 1 сохраняютсяство для формирования и хранения выче-. нулевые логические потенциалы, тов чисел по модулю три без какихТаким образом, триггер 9, опреде- либо доработок может быть использоваляя четность передаваемого разряда но в устройствах сопряжения цифровых информации регистра 8, обеспечивает вычислительных машин с периферийными соответствующее распределение единич- устроиствами, работающими на плаваюочной информации передаваемого кода им- щих или переменных частотах.

СмотретьЗаявка

3579265, 13.04.1983

ПРЕДПРИЯТИЕ ПЯ В-2969

ГЛЕБОВИЧ ВЯЧЕСЛАВ ГЕННАДЬЕВИЧ

МПК / Метки

МПК: G06F 11/10

Метки: вычетов, модулю, три, формирования, хранения, чисел

Опубликовано: 23.08.1984

Код ссылки

<a href="https://patents.su/5-1109755-ustrojjstvo-dlya-formirovaniya-i-khraneniya-vychetov-chisel-po-modulyu-tri.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования и хранения вычетов чисел по модулю три</a>

Предыдущий патент: Многоканальное устройство для подключения абонентов к общей магистрали

Следующий патент: Устройство для контроля и диагностики дискретных объектов

Случайный патент: Устройство для измерения перемещений объекта