Аналоговый интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 896633

Авторы: Могилевский, Славный

Текст

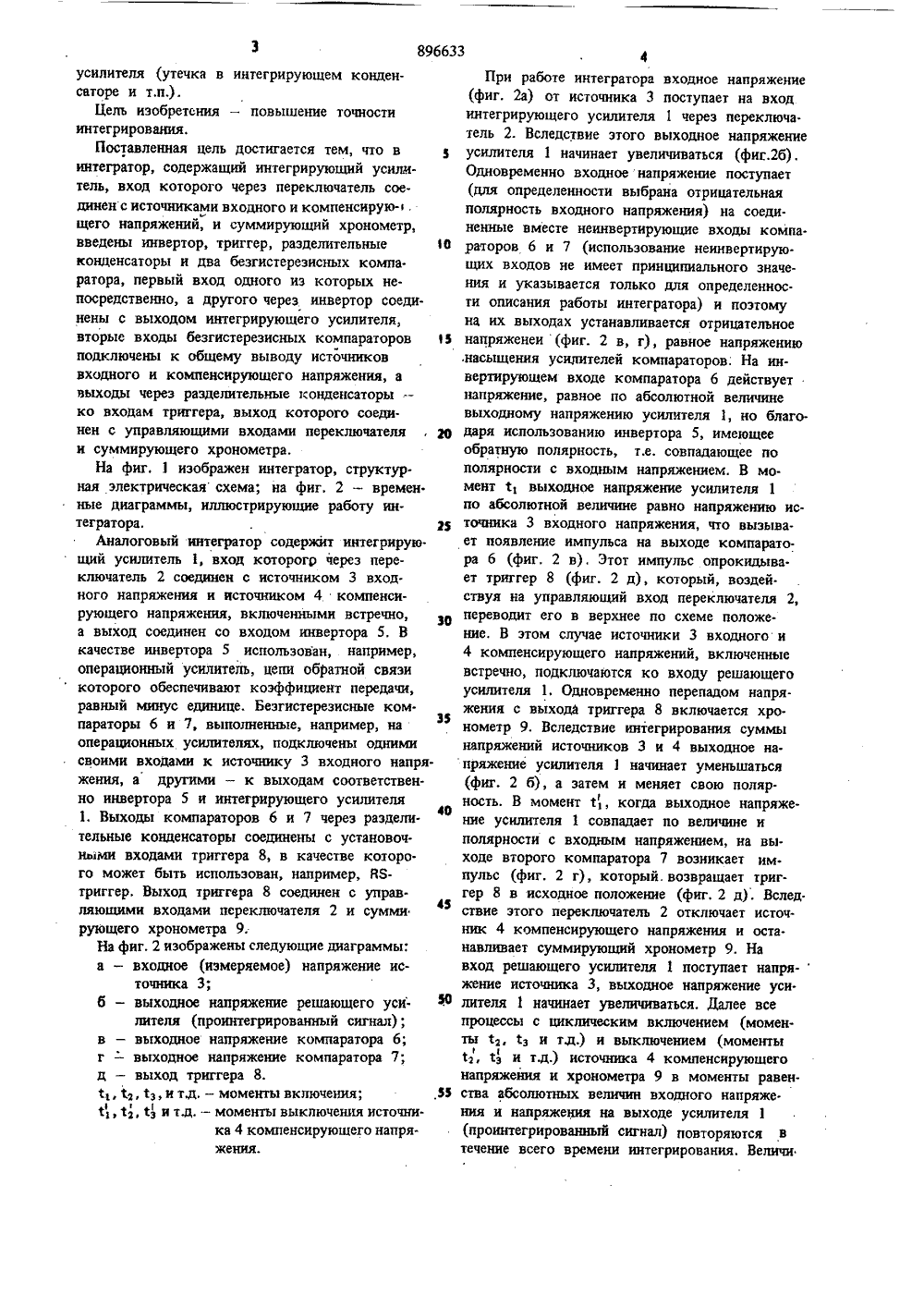

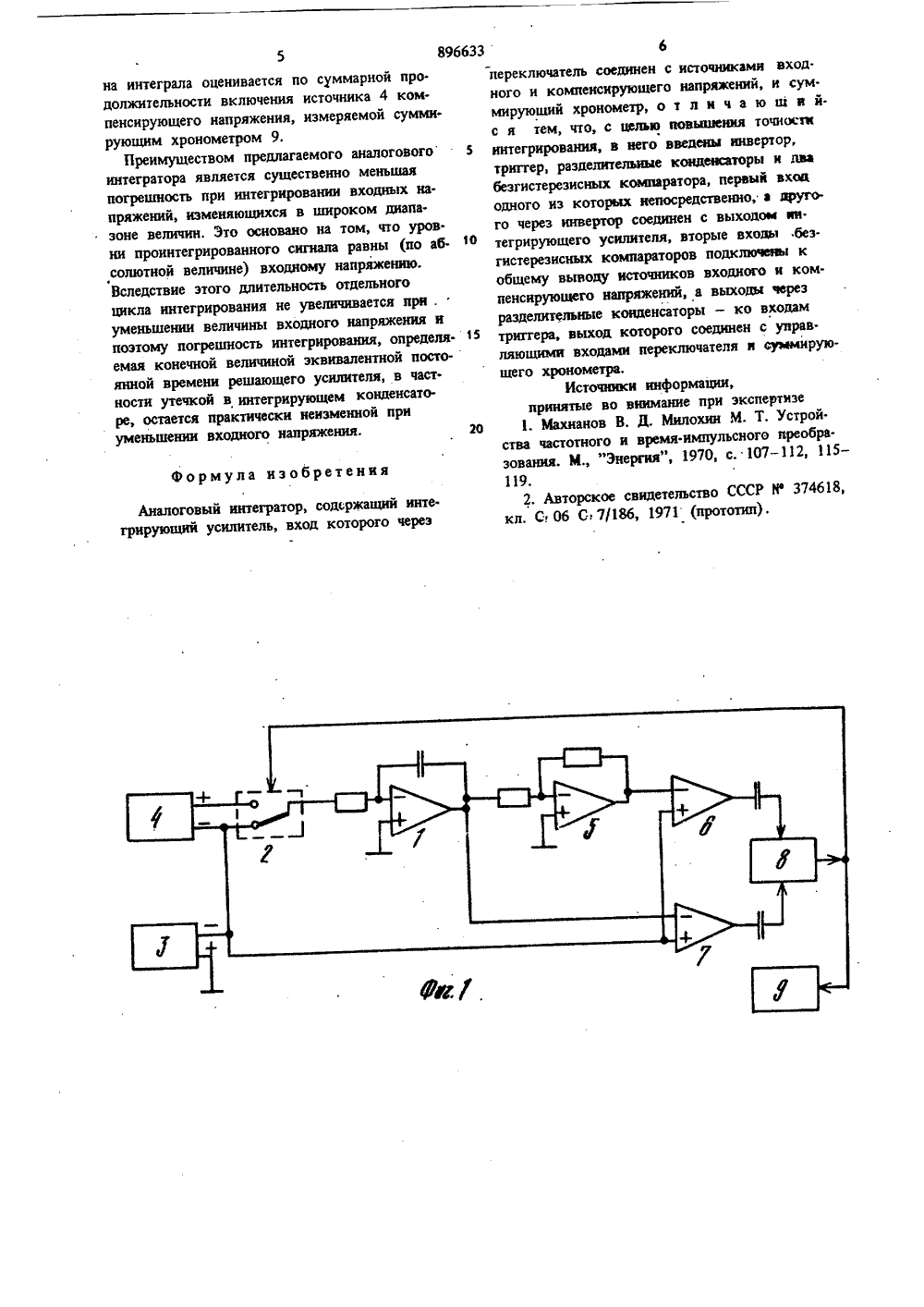

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советск ихСоциалистическихРеспублик оц 896633(22) За и влево 23.04,80 (2 ) 2915961/18-24с присоединением заявки рй(51)М, Кл. 6 06 6 7 Л 861 ваударстееввй квинтет СССР в далан кзебретеннй в етнрытвй(50) АНАЛОГОВЫЙ ИНТЕГРАТОР Изобретение относится к электронной измерительной технике, в частности к электронным аналоговым интеграторам длительныхпроцессов, и может быть использовано, например, в кулонометрии с контролируемым потен.циалом.Известны электронные аналоговые интеграторы, работа которых основана на использовании решающих усилителей с емкостной обратной связью. В этих усилителях сначалаинтегрируют измеряемый (входной) сигнал,а затем компенсационный сигнал или суммувходного и компенсационного сигналов 1.Недостатками этих интеграторов являютсяперерывы в интегрировании входного сигна.ла и недостаточно высокая точность,Наиболее близким к предлагаемому является аналоговый интегратор, содержащий интегрирующий решающий усилитель, источниккомпенсирующего (эталонного) напряжения,гистерезисное нереключаюшее устройство исуммирующий хронометр 2,Недостатком известного интегратора является возрастание погрешности интегрирования при уменьшении величины входного напряжения, Это особенно существенно приислольэовании интегратора в кулонометриис контролируемым потенциалом, в которомподлежащий интегрированию сигнал экспоненциально уменьшается во времени. Недостаток обусловлен тем, что уровни проинтегрированного сигнала (напряжение на выходе усилителя), соответствующие моментам включения и выключения источника компенсирующего напряжения, постоянны и определяются толь.ко величиной гнстерезиса переключающегоустройства (его уровнями срабатывания и опус.кания). Поэтому длительность каждого отдельного цикла интегрирования, состоящего изинтегрирования входного напряжения и последующего интегрирования суммы входного нкомпенсирующего напряжений, зависит от ве.личины входного напряжения, увеличиваясьпри уменьшении последнего, Увеличениежедлительности отдельного цикла интегрированияприводит к соответствующему увеличению погрешности вследствие конечного значения эквивалентной постоянной времени решающего896633 5 20 30 33 40 43 усилителя (утечка в интегрирующем конденсаторе и т.п,).Цель изобретения - повышение точностиинтегрирования,Поставленная цель достигается тем, что винтегратор, содержащий интегрирующий усилитель, вход которого через переключатель соединен с источниками входного и компенсирую,щего напряжений, и суммирующий хронометр,введены инвертор, триггер, разделительныеконденсаторы и два безгистерезисных компа.ратора, первый вход одного из которых непосредственно, а другого через инвертор соединены с выходом интегрирующего усилителя,вторые входы безгистерезисных компараторовподключены к общему выводу источниковвходного и компенсирующего напряжения, авыходы через разделительные конденсаторы -ко входам триггера, выход которого соединен с управляющими входами переключателяи суммирующего хронометра.На фиг. 1 изображен интегратор, структур.ная электрическая схема; на фиг. 2 - временные диаграммы, иллюстрирующие работу интегратора.Аналоговый интегратор содержит интегрирую.щий усилитель 1, вход которогр через переключатель 2 соединен с источником 3 входного напряжения и источником 4 компенсирующего напряжения, включенными встречно,а выход соединен со входом ннвертора 5, Вкачестве инвертора 5 использован, например,операционный усилитель, цепи обратной связикоторого обеспечивают коэффициент передачи,равный минус единице. Безгистерезисные ком.параторы 6 и 7, выполненные, например, наоперационных усилителях, подключены однимисвоими входами к источнику 3 входного напряжения, а другими - к выходам соответственно инвертора 5 и интегрирующего усилителя1, Выходы компараторов 6 и 7 через разделительные конденсаторы соединены с установочными входами триггера 8, в качестве которо.го может быть использован, например, ЯЗтриггер. Выход триггера 8 соединен с управляннцими входами переключателя 2 и суммирующего хронометра 9,На фиг, 2 изображены следующие диаграммы.а - входное (измеряемое) напряжение источника 3;б - выходное напряжение решающего усилителя (проинтегрированный сигнал);в - выходное напряжение компаратора б;г -выходное напряжение компаратора 7;д - выход триггера 8.11, Сг, 1 г, и тд, - моменты включения;т 1 г, Ф, и т.д. - моменты выключения источника 4 компенсирующего напряжения. При работе интегратора входное напряжение(фиг. 2 а) от источника 3 поступает на входинтегрирующего усилителя 1 через переключа.тель 2. Вследствие этого выходное напряжение усилителя 1 начинает увеличиваться (фиг.2 б), Одновременно входное напряжение поступает (для определенности выбрана отрицательная полярность входного напряжения) на соединенные вместе неинвертирующие входы компа. раторов б н 7 (использование неинвертирующих входов не имеет принципиального значения и указывается только для определенности описания работы интегратора) и поэтому на их выходах устанавливается отрицательное напряженен (фнг, 2 в, г), равное напряжению насыщения усилителей компараторов: На инвертирующем входе компаратора б действует напряжение, равное по абсолютной величине выходному напряжению усилителя 1, но благодаря использованию инвертора 5, имеющееобратную полярность, т,е. совпадающее по полярности с входным напряжением. В момент 1, выходное напряжение усилителя 1по абсолютной величине равно напряжению источника 3 входного напряжения, что вызывает появление импульса на выходе компаратора б (фиг, 2 в), Этот импульс опрокидывает триггер 8 (фиг. 2 д), который, воздей. ствуя на управляющий вход переключателя 2, переводит его в верхнее по схеме положение. В этом случае источники 3 входного и 4 компенсирующего напряжений, включенные встречно, подключаются ко входу решающего усилителя 1. Одновременно перепадом напряжения с выхода триггера 8 включается хронометр 9, Вследствие интегрирования суммы напряжений источников 3 и 4 выходное на. пряжение усилителяначинает уменьшаться (фиг, 2 б), а затем и меняет свою полярность. В момент 1 когда выходное напряжение усилителя 1 совпадает по величине и полярности с входным напряжением, на выходе второго компаратора 7 возникает им. пульс (фиг. 2 г), который. возвращает триггер 8 в исходное положение (фиг, 2 д). Вслед. ствие этого переключатель 2 отключает источник 4 компенсирующего напряжения и оста. навливает суммирующий хронометр 9. На вход решающего усилителя 1 поступает напря-жение источника 3, выходное напряжение уси.лителя 1 начинает увеличиваться, Далее все процессы с циклическим включением (моменты 1 г. 1 з и тд.) и выключением (моменты 1 г, 1 э и тд.) источника 4 компенсиРУюшего напряжения и хронометра 9 в моменты равенства абсолютных величин входного напряже. ния и напряжения на выходе усилителя 1 (проинтегрированный сигнал) повторяются в течение всего времени интегрирования. Величи896633на интеграла оценивается по суммарной продолжительности включения источника 4 компенсирующего напряжения, измеряемой суммирующим хронометром 9.Преимуществом предлагаемого аналогового 5 интегратора является существенно меныааяпогрешность при интегрировании входных напряжений, изменяющихся в широком диана.зоне величин. Это основано на том, что уровни проинтегрированного сигнала равны (по аб. 1 о солютной величине) входному напряжению.1Вследствие этого длительность отдельногоцикла интегрирования не увеличивается при .уменьшении величины входного напряжения и поэтому погрешность интегрирования, определя емая конечной величиной эквивалентной постоянной времени решающего усилителя, в частности утечкой в интегрирующем конденсаторе, остается практически неизменной приуменьшении входного напряжения. 2 ОФормула изобретенияАналоговый интегратор, содержащий инте.грирующий усилитель, вход которого через переключатель соединен с источниками вход.ного и компенсирующего напряжений, и сум.мирующий хронометр, о т л и ч а ю щ и й.с я тем, что, с целью повышения точностиинтегрирования, в него введены инвертор,триггер, разделительные конденсаторы и двабезгнстерезисных компаратора, первый входодного из которых непосредственно, а другого через инвертор соединен с выходом ии.тегрирующего усилителя, вторые входы безгистерезисных компараторов подключены кобщему выводу источников входного и компенсирующего напряжений, а выходы черезразделительные конденсаторы - ко входамтрипера, выход которого соединен с управляющими входами переключателя и суммирующего хронометра.Источники информапии,принятые во внимание при экспертизе1. Махнанов В. Я, Милохии М. Т, Устрой.ства частотного и время-импульсного преобразования. М., "Энергия", 1970, с, 107- 112, 115119.2. Авторское свидетельство СССР К 4 374618,кл. С, 06 С 7/186, 1971 (прототип),

СмотретьЗаявка

2915961, 23.04.1980

ОРДЕНА ЛЕНИНА ИНСТИТУТ ГЕОХИМИИ И АНАЛИТИЧЕСКОЙ ХИМИИ ИМ. В. И. ВЕРНАДСКОГО АН СССР

МОГИЛЕВСКИЙ АЛЕКСАНДР НАУМОВИЧ, СЛАВНЫЙ ВИКТОР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06G 7/186

Метки: аналоговый, интегратор

Опубликовано: 07.01.1982

Код ссылки

<a href="https://patents.su/4-896633-analogovyjj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый интегратор</a>

Предыдущий патент: Цифровой экстраполятор

Следующий патент: Аналоговый интегратор

Случайный патент: Модульный железобетонный элемент сборной тоннельной обделки