Аналого-цифровой преобразователь с параллельным кодированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

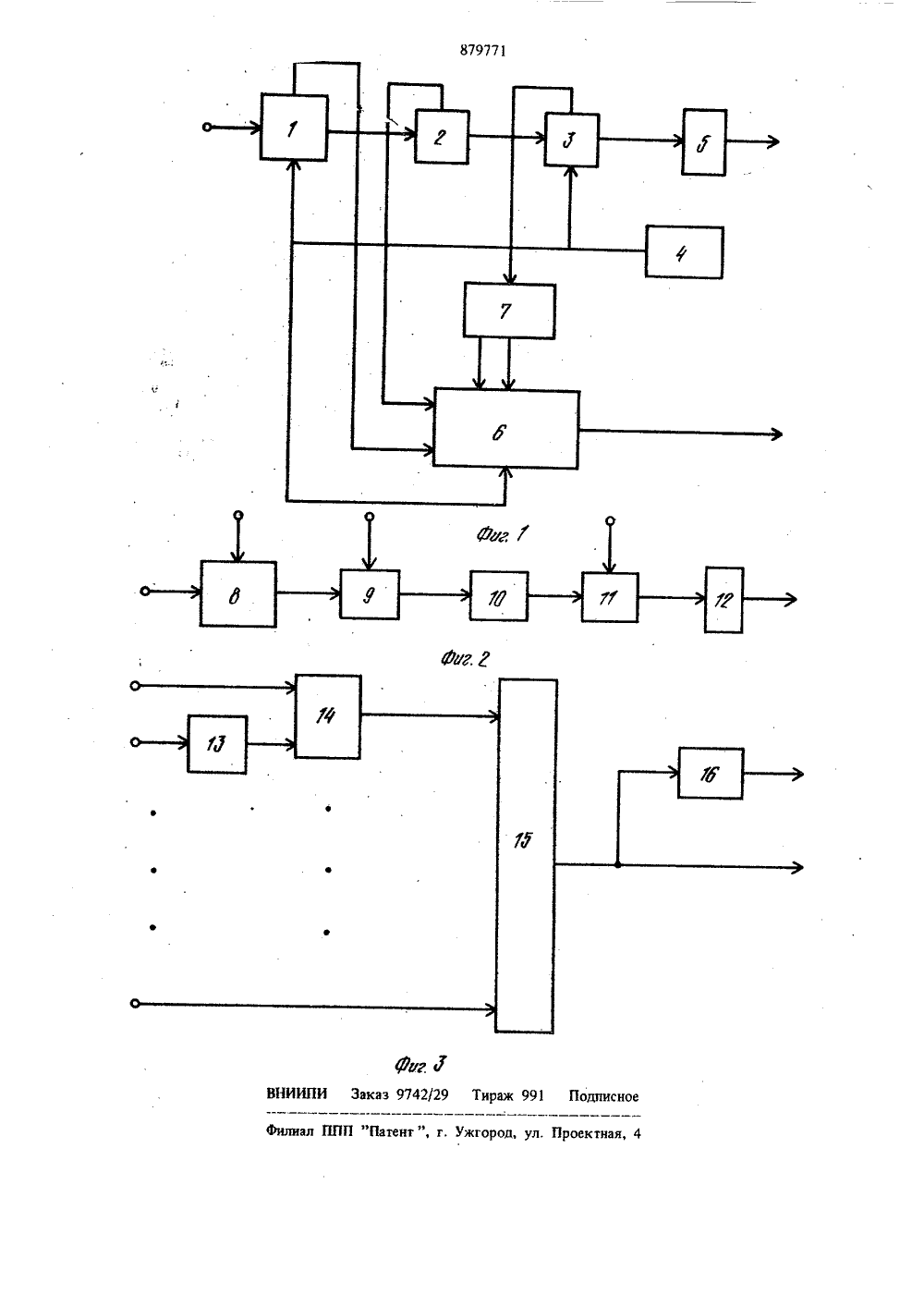

О П И С А Н И Е (ц)879771ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскмкСоциалистическиеРеспублик(22) За ивлеио 11.02,80 (2 ) 2878976/8 - 21с присоединением заявки НЙдо делам изобретений н открытийОпубликовано 07,11,81, Бюллетень Юе 41 Дата опубликования описания 07,11.81(72) Авторы изобретения имов и(7) Заявитель Саратовский политехнический 4) АНАЛОГО - ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПАРАЛЛЕЛЬНЫМ КОДИРОВАНИЕМ Изобретение относится к технике непрерывно - дискретного преобразования информации и применяется в информационно-измерительных системах и устройствах для преобразования широкополосных электрических сигналов в двоичный цифровой код,Известен преобразователь, содержащий блок эталонных уровней напряжения, подключенный к первому входу блока элементов сравнения и к входу блока зон ограничений и нечувствительности, который своим выходом через блок масштабных усилителей соединен с вторым входом блока схем сравнения, а выход блока схем сравнения связан с входом шифратора 1Недостатком данного преобразователя явля. ется низкая надежность его работы.Целью изобретения является повышение нздежности преобразования.Эта цель достигается тем, что в известный аналого-цифровой преобразователь с параллельным кодированием, содержащий блок зон ограничения и нечувствительности, первый вход которой соединен с входной шиной, второй вход - с выходом блока эталонных уровней напряжения, а первый выход - с входом блокамасштабных усилителей, первый выход которого соединен с первым входом блока элементовсравнения, второй вход которого соединен с выходом блока эталонных уровней напряжения, апервые выходы соединены с шифратором, дополнительно введены формировзтель кодамладших разрядов, блок управления, приэтом входы блока управления соединены свторыми выходами блока элементов сравнения,первый н второй выходы соединены, соответ.ственно с первым и вторым входами формнро.вателя кода младших разрядов, третий входкоторого соединен с выходом блока этзлонныхуровней напряжения, четвертый вход - с вторым выходом блока зон ограничений и нечувствительности, а пятый вход - с вторым выходом блока масштабных усилителей.Формирователь кода младших разрядов вы. полнен в виде суммирующих усилителей, блока дополнительных элементов сравнения, шифратор блока элементов И и блока элементов ИЛИ, пргчем первый и второй входы блока суммиру ющих усилителей соединены с четвертыми87977и пятыми входами формирователя кола младшихразрядов соответственно, а выход подключенк первому входу блока дополнительных элементов сравнения, второй вход которого соединенс третьим входом формирователя кода младшихразрядов, выход блока дополнительных элемен.тов сравнения через шифратор соединен с первым входом блока элементов И, второй итретий входы которого соединены с первым ивторым входами формирователя кода младших 10разрядов, выход блока элементов И соединенс входом блока элементов ИЛИ, выход которого соединен с выходом формирователя кода младших разрядов.Блок управления выполнен в виде блоковэлементов И, ИЛИ, НЕ, элемента НЕ, причемвходы блока элементов ИЛИ подключены к выходам блока элементов И, нечетные входы кото.рого непосредственно соединены с входами блока управления, а четные входы соединены свходами блока управления через первый блокэлементов НЕ, выход блока элементов ИЛИнепосредственно и через элемент НЕ соединенс первыми и вторым выходами блока управления соответственно.25На фиг. 1 представлена схема аналого-цифрового преобразователя", на фиг.2 - схемаформирователя кода младших разрядов; нафиг. 3 - схема блока управления блоком формирования кода младших разрядов,Преобразователь содержит (фиг, 1) блок 130зон ограничений и нечувствительности, блок 2масштабных усилителей, блок 3 элементов сравнения, блок 4 эталонных уровней напряжения,шифратор 5, блок 6 формирования кода младших разрядов и блок 7 управления каналом, 55Выход шифратора и выход блока формирования.кода младших разрядов являются выходамипреобразователя. Формирователь кода младшихразрядов (фиг. 2) содержит блок 8 суммирующих усилителей, блок 9 элементов сравнения, 40шифратор 10, блок 11 элементов И и блок 12элементов ИЛИ,На фиг, 3 представлена схема блока 1управления блоком формирования кода младших разрядов, который содержит 2 - 1 элеЕ ментов НЕ 13, 2 - 2 элементов И 14, 21 И И1 элементов ИЛИ 15, элемент НЕ 16.Работа устройства осуществляется следующимобразом,Преобразуемое напряжение ОВХ(т) подается 50на первые входы блока 1, на вторые входыкоторого (кроме первой зоны нечувствительности, на которую подан потенциал "земли")с блока 4 подаются эталонные напряжения, соответственно равные отрицательным потенциалам 55в диапазоне -О, - : (2 - 1)Я, где величинаИ"х (+) махьнЬа К ааааа максимальное анас2 1чение преобразуемого сигнала О (т),го= -- ко- .ИХ2ничества разрядов и одного положительногоуровня напряжения, равного 0,5 О, а и - число двоичных разрядов на выходе преобразователя,Зоны ограничения ограничивают сигналыс зон нечувствительности диапазоном от О до0,5 9, при этом первая комбинированная нелинейность имеет нулевую зону нечувствительности, вторая комбинированная нелинейность -зону нечувствиетельностн ,равную 9, третья комбинированная нелинейность - зону нечувстви-.тельности, равную 2 9, четвертая - равную 3 9,и т. д, У последней комбинированной нелинейности зона нечувствительности равна (2 - 1) 9.С выходов блока 1 на входы блока 2В 4поступают сигналы, которые усиливаются в 2раз и подаются на блок 3 с помощью которыхосуществляется сравнение указанных выше сигналов с уровнем напряжения, равным (2 Ч ).Если в процессе сравнения окажется,.что сигнала снимаемый с выхода масштабного усилителя, равен или превышает уровень напряжения2 Д, то элемент сравнения срабатывает. Вдальнейшем единичный код с выходов элементов сравнения подается на шифратор 5, гдеон преобразуется в двоичный, при этом шифратор 5 будет преобразовывать параллельныйединичный код с разрядностью, равной 2 а-в параллельный двоичный код с разрядностью,равной щ, который представляет собой кодстарших разрядов М .Одновременно с вторых выходов блоков 1 и 2напряжения поступают на четвертые и пятыевходы блока 6, на третьи входы - эталонноенапряжение с блока 4 на первые и вторыевходы поступают управляющие сигналы блока 7,В зависимости от величины входного напряжения срабатывает один или несколько элементов сравнения блока 9 формирователя кодамладших разрядов. Если напряжение О Х(т) изменяется в диапазоне 9ОХ(т) (Я, то напряжение поступает только на вход первого суммирующего усилителя блока 8, усиливается ипоступает на первый элемент сравнения блока9, где преобразуется в параллельный единичный код. Этот код посредством шифратораИ10 или 12 преобразуется в двоичный код Йи через блок 11 элементов И и блоком элемента ИЛИ 12;. подается на выход формирователя6, При достижении напряжением значенияО(т)=Ц сигнал с выхода блока 7 обнуляетвйход блока 6,Аналогично будут формироваться сигналыпри изменении О Х(т) в диапазонахЧ(ОВХ(т) сгч; г ИО,(т)3 9 (т)и т. д. При этом канал формирования кодамладших разрядок при значениях Овх(1) = Я,2 Я,З О ит.д. до (2 - 1) Чне будет879771 Формула изобретения 1. Аналого - цифровой преобразователь с параллельным кодированием, содержащий блок зон ограничений и нечувствительности, первый вход которой соединен с входной шиной, второй вход - с выходом блока эталонных уровней напряжения, а первый выход - с входом блока масштабных усилителей, первый выход которого соединен с первым входом блока элементов сравнения, второй вход которого соединен с выходом блока эталонных уровней напряжения, а первые выходы соединены с шифратором, о т л и ч а ю щ и й с я тем, что, с целью повышения надежности преобра 40 5выдавать цифровой информации (Иа =0) При значениях(1), лежащих в диапазонах Я(ОЗ(1) (й, 2 9 ОрХ(1) 3 9 и т. д. до (2 - 2)Я(0 (1) (2 - 1) Ч, формированиеИкода Ибудет осуществляться с помощью 5 нечетных масштабных усилителей при значениях 0(1), лежащих в диапазонах Яч (1) 2 Я, 3 9(08 х(1) 4 Я и т. д. до (2 -1) ЦО (1)2 Я, формирование кода. 1 ч с1 О помощью четных масштабных усилителей, Блок 7 формирует управляющие сигналы следующим образом, При изменении сигнала 011) в диапазоне 0( 08(1)Я на один элемент сравнения блока 3 и на входы блока 7 поступает ло гический нуль, при этом на его первом выходе появится управляющий сигнал, поступающий на первый вход формирователя 6. При достижении О, (1) =Я выход формирователя 6 кода младшихВХразрядов обнуляется.10При изменении напряжения ОХ(1) в диапазоне О.сО(1)2 9 сработает первый элемент сравнения блока 3 элементов сравнения и на вход блока 7 поступит. единичный сигнал, при этом управляющйй сигнал появится на втором выходеблока 7, который поступит на второй вход блока 6, который снова формирует код младших разрядов. При изменении напряжения ОХ(1) в диапазоне 2 ЯО Х(1)3 Ц комбинация управляющих сигналов изменится на обратную, т. е, станет такой, как при изменении напряжения Ос (1) в диапазоне ЯОХ (1)9; уменьшение числа элементов в аналого-цифровом преобразователе повышает надежность его работы,Ьзования, в него введены формирователь кодамладших разрядов, блок управления, приэтом входы блока управления соединены с вто.рыми выходами блока элементов сравнения,первый и второй выходы соединены соответ.ственно с первым и вторым входами формирователя кода младших разрядов, третий входкоторого соединен с выходом блока эталонных уровней напряжения, четвертый вход -с вторым выходом блока для ограничений инечувствительности, а пятый вход - с вторымвыходом блока масштабных усилителей,2. Преобразователь по п. 1, о т л и ч а ющ и й с я тем, что формирователь кодамладших разрядов выполнен в виде блокасуммирующих усилителей, блока дополнитель -ных элементов сравнения, шифратора, блокаэлементов И и блока элементов ИЛИ, причемпервый и второй входы блока суммирующихусилителей соединены с четвертыми и пятымивходами формирователя кода младших разрядов соответственно, а выход подключен кпервому входу блока дополнительных элементов сравнения, второй вход которого соединенс третьим входом формирователя кода младшихразрядов, выход блока дополнительных элементов сравнения через шифратор соединен с первым входом блока элементов И, второй и тре.тий входы которого соединены с первыми ивторыми входами формирователя кода младших разрядов, выход блока элементов И сое динен с входом блока элементов ИЛИ, выходкоторого соединен с выходом формирователякода младших разрядов.3, Преобразователь по п. 1, о т л и ч а ющ и й с я тем, что блок управления выполненв виде блоков элементов И, ИЛИ, НЕ, элемента НЕ, причем входы блока элементов ИЛИподключены к выходам блока элементов И,нечетные входы которого непосредственно соединены с входами блока управления, а четныевходы соединены с входами блока управлениячерез первый блок элементов НЕ, выход блокаэлементов ИЛИ непосредственно и через элемент НЕ соединен с первым и вторым выходами блока управления соответственно.Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР Нф 678554,кл. Н 01 Н 33/66, 1977,

СмотретьЗаявка

2878976, 11.02.1980

САРАТОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КАРИМОВ РАВИЛЬ НУРГАЛИЕВИЧ, ТРЕТЬЯКОВ ВИКТОР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: аналого-цифровой, кодированием, параллельным

Опубликовано: 07.11.1981

Код ссылки

<a href="https://patents.su/4-879771-analogo-cifrovojj-preobrazovatel-s-parallelnym-kodirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой преобразователь с параллельным кодированием</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Цифровой интегрирующий вольтметр

Случайный патент: Накопитель ленточного материала