826567

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 826567

Автор: Аралбаев

Текст

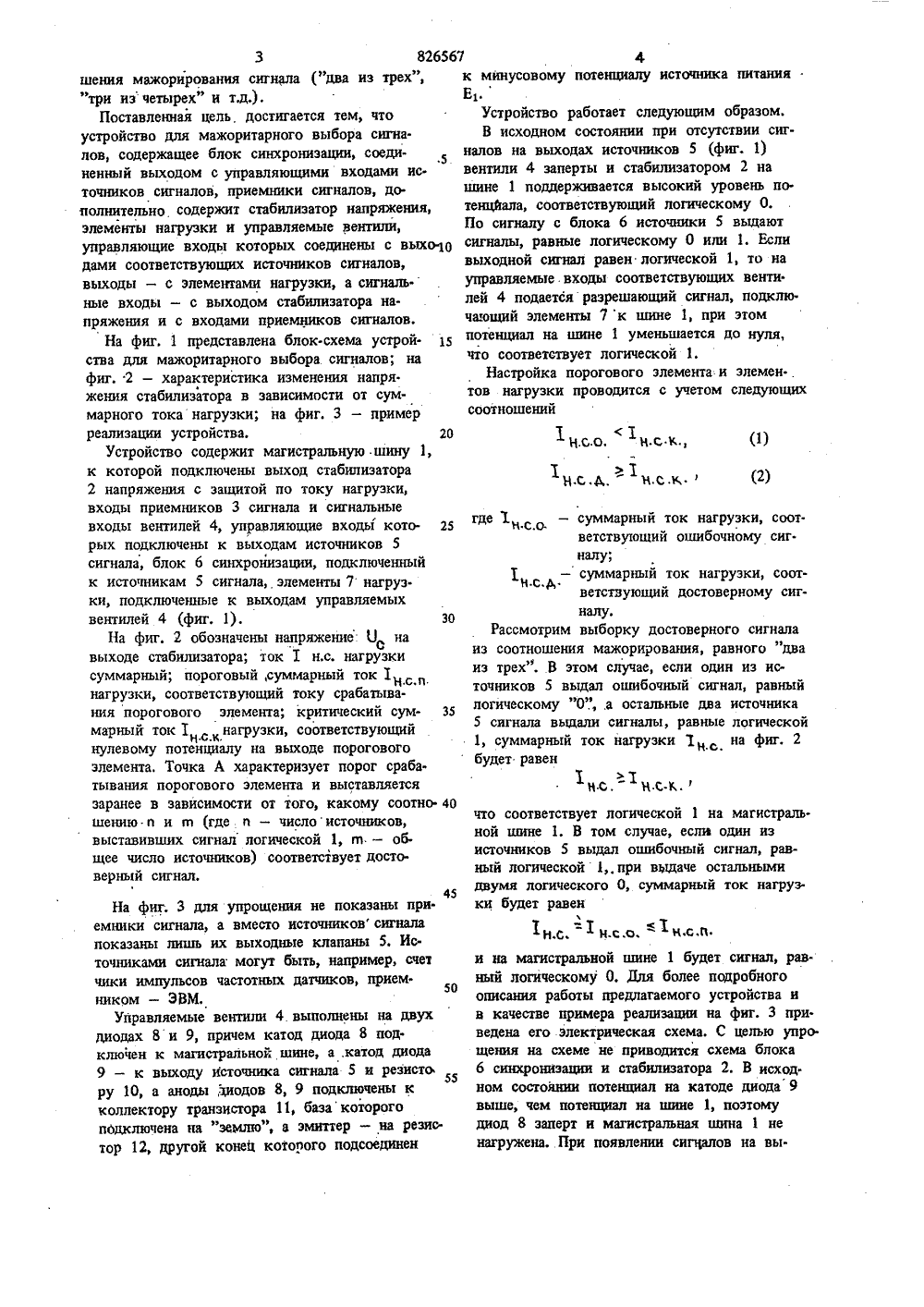

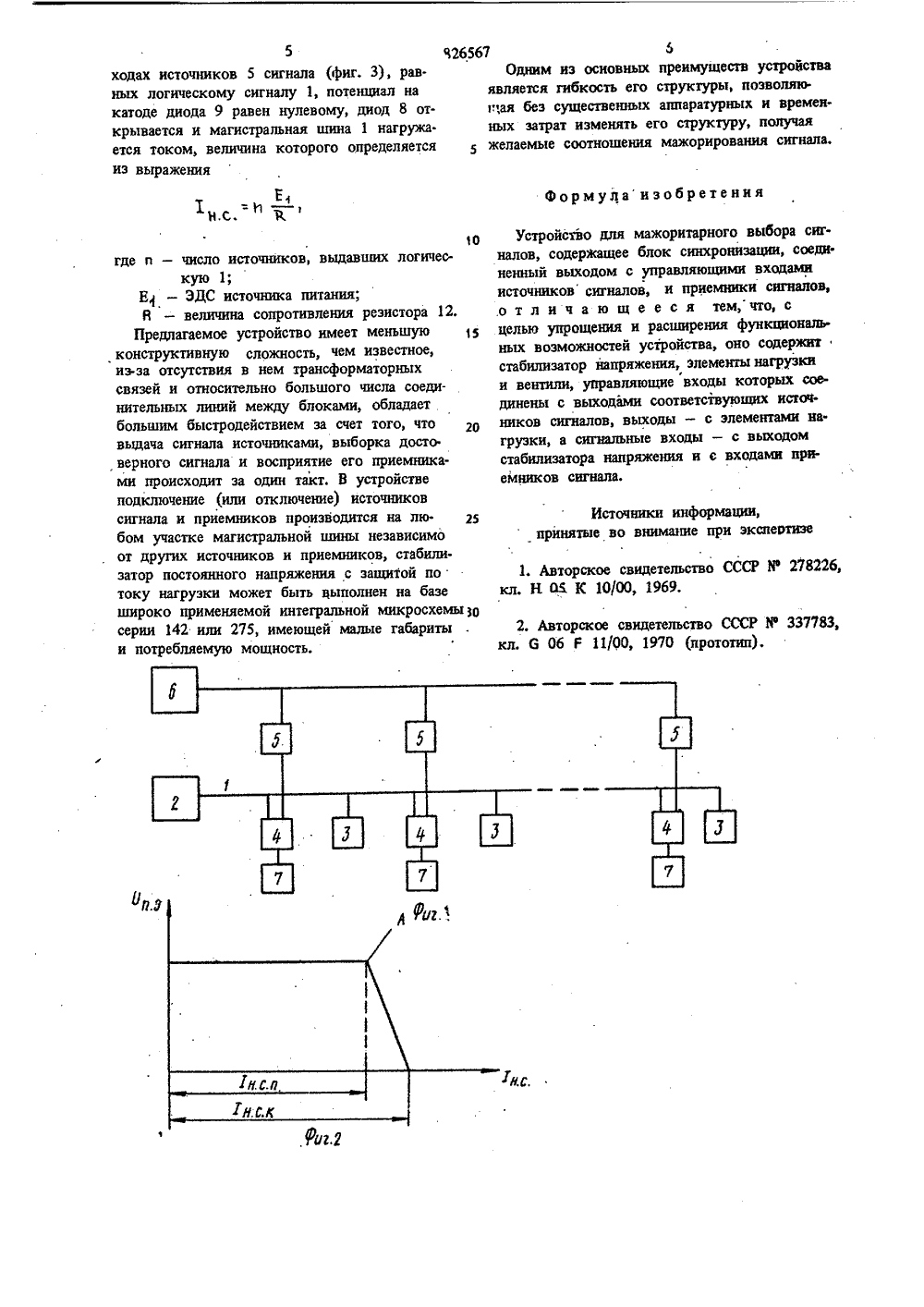

и 826567 ОП ИСАНИЕИЗЬБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическикРеспублик(5 М. Кл. Н 03 К 19/23 6 06 Р 11/00 Н 05 К 10/00 Гасударственный камнтет СССР по делам нзобретеннй н отнрмтнй/Ордена Ленина институт кибернетики АН Украинской(54) УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ Изобретение относится к вычислительной технике и может быть использовано в цифро вых вычислительных устройствах с магистраль но.модульной структурой для мажоритарного ,выбора сигналов на магистралях при передаче их от источников к приемникам.Известно устройство для мажоритарного выбора сигналов, содержащее кольцевой трех- разрядный релаксатор, выходы разрядов кото. рого попарно подключены к источникам входных сигналов, а выход последнего разряда соединен через дифференцирующий элемент с выходом устройства 1).Недостаток устройства состоит в сложности изменения его структуры в целях расширения его функциональных возможностей, например, для изменения соотношения мажорирования, позволяющего выбрать достоверный сигнал из соотношений, отличных от соотношения "два из трех"обеспечения реконфигурации блоков устройства без существенных аппаратурных и . временных затрат 1).На 1 тболее близким техническим решением к предлагаемому изобретению является устройство для мажоритарного выбора сигналов,содержащее блок синхронизации, соединенныйс управляющими входами ключей, через которые резервируемые блоки подключены ксоответствующим информационным входамф мажоритарного элемента, управляющий входкоторого соединен с выходом управляемогоключа, соединенного с выходом блока син.хронизации и соответствующими входами мажоритарного элемента 2).Недостатки устройства состоят в его сложности, обусловленной наличием большого числатрансформаторных связей и связей между блоками, и. ограниченными функциональнымивозможностями - мажоритарным выборомтч по принципу "два из трех".,Цель изобретения - упрощение устройстваи расширение его функциональных возможностей, в частности обеспечение гибкостиструктуры устройства, которая позволила быбез существенных аппаратурных и временныхзатрат осуществлять реконфигурацию блоковустройства, для получения различного соотнес7 4к минусовому потенциалу источника питания . Е.Устройство работает следующим образом.В исходном состоянии при отсутствии сигналов на выходах источников 5 (фиг. 1) вентили 4 заперты и стабилизатором 2 на шине 1 поддерживается высокий уровень по. тенцйала, соответствующий логическому О. По сигналу с блока 6 источники 5 вьщают сигналы, равные логическому О или 1. Если выходной сигнал равен логической 1, то на управляемые входы соответствующих венти. лей 4 подается разрешающий сигнал, подключаощий элементы 7 к шине 1, при этом потенциал на шине 1 уменьшается до нуля, что соответствует логической 1.Настройка порогового элемента и элемен. тов нагрузки проводится с учетом следующих соотношений(г) 25 де 1 н с о суммаРный ток нагрузки, соот.ветствуюшнй ошибочному сиг.налу;- суммарный ток нагрузки, соотг.с.дветствующий достоверному сиг 30 калу.Рассмотрим выборку достоверного сигналаиз соотношения мажорнрования, равного "дваиз трех"В этом случае, если один из источников 5 выдал ошибочный сигнал, равныйлогическому "О" .а остальные два источника5 сигнала вьщали сигналы, Равные логической1, суммарный ток нагрузки 1 на фиг, 2будет равенНС. Н СИ,3 82656щения мажорирования сигнала ("два из трех""три из четырех" и т,д.),Поставленная цель достигается тем, чтоустройство для мажоритарного выбора сигналов, содержащее блок синхронизации, соединенный выходом с управляющими входами ис.точников сигналов, приемники сигналов, дополнительно содержит стабилизатор напряжения,элементы нагрузки и управляемые вентили,управляющие входы которых соединены с выхо дами соответствующих источников сигналов,выходы - с элементами нагрузки, а сигналь-ные входы - с выходом стабилизатора напряжения и с входами приемников сигналов.На фиг. 1 представлена блок. схема устройства для мажоритарного выбора сигналов; нафиг. 2 - характеристика изменения напря.жения стабилизатора в зависимости от суммарного тока нагрузки; на фиг. 3 - примерреализации устройства. 20Устройство содержит магистральную шину 1,к которой подключены выход стабилизатора2 напряжения с защитой по току нагрузки,входы приемников 3 сигнала и сигнальныевходы вентилей 4, управляющие входы кото.рых подключены к выходам источников 5сигнала, блок 6 синхронизации, подключенныйк источникам 5 сигнала, элементы 7 нагрузки, подключенные к выходам управляемыхвентилей 4 (фиг, 1).На фиг. 2 обозначены напряжение Ц, навыходе стабилизатора; ток 1 н.с. нагрузкисуммарный; пороговый, суммарный ток 1нагрузки, соответствующий току срабатывания порогового элемента; критический суммарный ток 1 нагрузки, соответствующийнулевому потенцйалу на выходе пороговогоэлемента. Точка А характеризует порог срабатывания порогового элемента и выставляетсязаранее в зависимости от того, какому соотно 40шению и и т (где и - числоисточников,выставивших сигнал логической 1, в - общее число источников) соответствует досто.верный сигнал.45На фиг. 3 для упрощения не показаны приемники сигнала, а вместо источников сигналапоказаны лишь их выходные клапаны 5. Источниками сигнала могут быть, например, счетчики импульсов частотных датчиков, прием.50ником - ЭВМ.Управляемые вентили 4. выполнены на двухдиодах 8 и 9, причем катод диода 8 под.ключен к магистральной шине, а .катод диода9 - к выходу источника сигнала 5 и резистору 10, а аноды диодов 8, 9 подключены кколлектору транзистора 11 базакоторогоподключена на "землю", а эмиттер - на резистор 12, другой коней которого подсоединен что соответствует логической 1 на магистральной шине 1. В том случае, если один из источников 5 выдал ошибочный сигнал, равный логической 1 при выдаче остальными двумя логического О, суммарный ток нагрузки будет равенн,с, =Т н.с.о. -Тн.с,п. и на магистральной шине 1 будет сигнал, равный логическому О, Для более подробногоописания работы предлагаемого устройства ив качестве примера реализации на фиг. 3 приведена его электрическая схема. С целью упро.щения на схеме не приводится схема блока6 синхронизации и стабилизатора 2, В исход.ном состоянии потенциал на катоде диода 9выше, чем потенциал на шине 1, поэтомудиод 8 заперт и магистральная шина 1 ненагружена, При появлении сигналов на вы.Ч 26567 5ходах источников 5 сигнала (фиг. 3), равных логическому сигналу 1, потенциал на катоде диода 9 равен нулевому, диод 8 открывается и магистральная шина 1 нагружается током, величина которого определяется из выражения 1 О где и - число источников, выдавших логическую 1;Е - ЭДС источника питания;В - величина сопротивления резистора 12.Предлагаемое устройство имеет меньшую конструктивную сложность, чем известное, из.за отсутствия в нем трансформаторных связей и относительно большого числа соединительных линий между блоками, обладает большим быстродействием за счет того, что выдача сигнала источниками, выборка досто.верного сигнала и восприятие его приемниками происходит за один такт. В устройстве подключение (или отключение) источников сигнала и приемников производится на лю з бом участке магистральной шины независимо от друтих источников и приемников, стабилизатор постоянного напряжения с защитой по току нагрузки может быть цыполнен на базе широко применяемой интегральной микросхемыщ серии 142 или 275, имеющей малые габариты и потребляемую мощность. 6Одним иэ основных преимуществ устройства является гибкость его структуры, позволяю. п,ая беэ существенных апнаратурных и временных затрат изменять его структуру, получая желаемые соотношения мажорирования сигнала,Формула изобретения Устройство для мажоритарного выбора сигналов, содержащее блок синхронизации, соеди. пенный выходом с управляющими входами источников сигналов, и приемники сигналов, .о т л и ч а ю щ е е с я тем,что, с целью упрощения и расширения функциональ ных воэможностей устройства, оно содержит стабилизатор напряжения, элементы нагрузки и вентили, управляющие входы которых соединены с выходами соответствующих истЮ- ников сигналов, выходы - с элементамн на. грузки, а сигнальные входы - с выходом стабилизатора напряжения и с входами нриемников сигнала. Источники информапии,принятые во внимание при экспертизе1. Авторское свидетельство СССР У 278226,кл. Н М К 10(00, 1969,2. Авторское свидетельство СССР У 337783,кл. 6 06 Р 11(00, 1970 (протопщ).82 б 567 Составитель В, МаксимовТехред М. Рейвес Корректор С, Шекмар едак пасе ПодписноеСССР наб д, 4/5 пвл ППП "Патент", г. Ужгород, ул. Проектная, 4 Заказ 2335/24 Тираж 988ВНИИПИ Государственного комитетапо делам изобретений и открытий113035, Москва, Ж, Раушская

СмотретьЗаявка

2814298, 23.08.1979

АРАЛБАЕВ ТАШБУЛАТ ЗАХАРОВИЧ

МПК / Метки

МПК: G06F 11/18

Метки: 826567

Опубликовано: 30.04.1981

Код ссылки

<a href="https://patents.su/4-826567-826567.html" target="_blank" rel="follow" title="База патентов СССР">826567</a>

Предыдущий патент: Логический элемент равнозначности

Следующий патент: Генератор импульсов

Случайный патент: Устройство для осланцевания горных выработок