Система передачи дискретной инфор-мации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 818026

Автор: Порохов

Текст

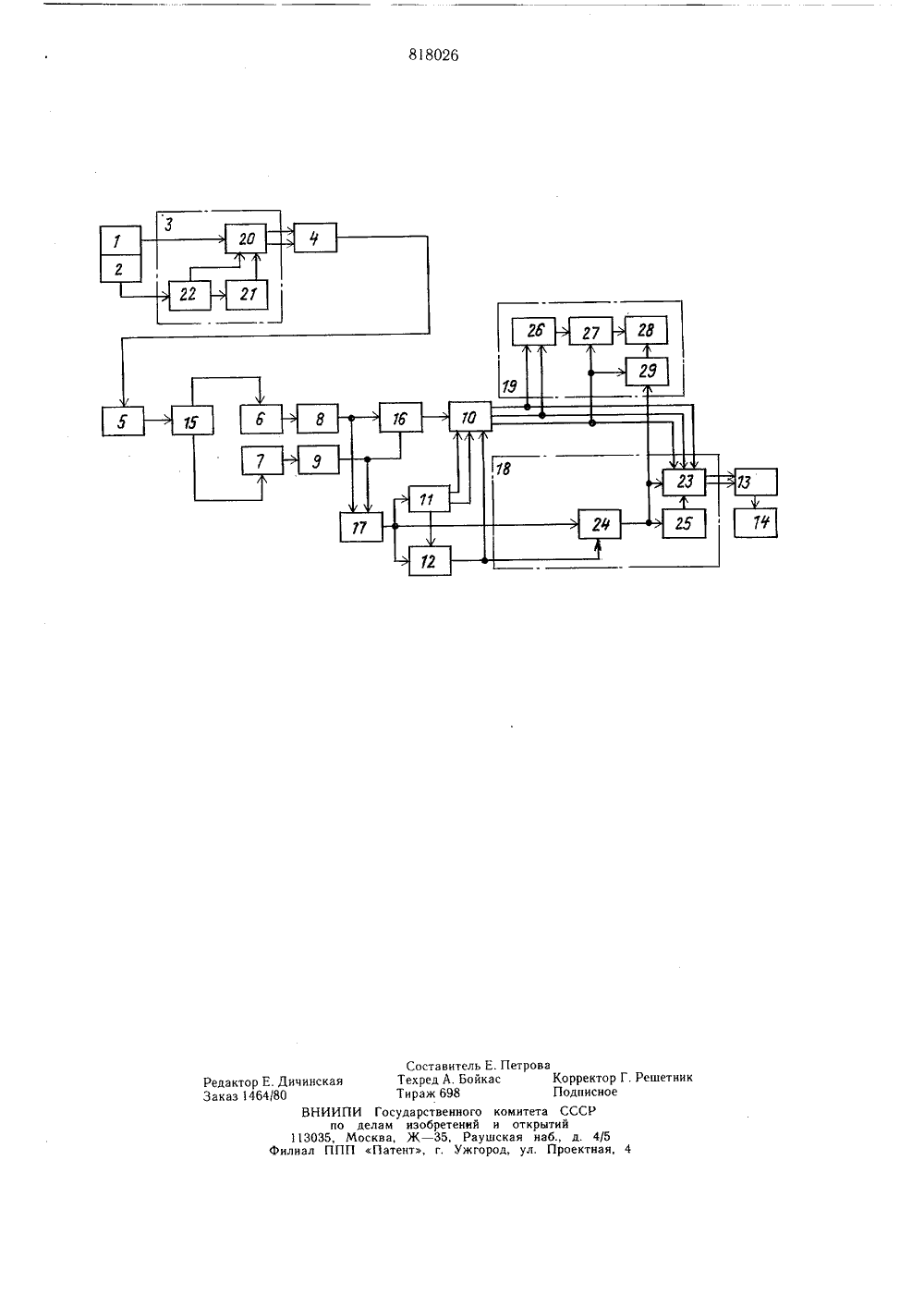

(,818026 Оп ИСАНИЕ ИЗОБРЕТЕЫ ИЯ Союз СоветскихСоциалистическихРеспублик К АВТОРСКОМУ СВИ ЕТ ЕЛЬ СТВУ.62 (088:8) Опубликовано 30.03.81. Бюллетень 12Дата опубликования описания 05.04.81 да делам иаобретеиий и открытий(54) СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ Изобретение относится к связи и может использоваться для передачи дискретной информации.Известна система передачи дискретной информации, содержащая на передающей стороне источник дискретной информации, формирователь импульсного сигнала и блок синхронизации, а на приемной стороне линейный усилитель, две ветви, каждая из которых состоит из последовательно соединенных блока оптимальной обработки сигнала и выпрямителя, а также решающий блок, входы которого соединены с выходами блока формирования напряжения порога и блока восстановления границ линейных посылок, входы которых соединены вместе, и последовательно соединенные формирователь двоичного сигнала и потребитель дискретной информации 1.Однако известная система имеет недостаточную пропускную способность.Цель изобретения - повышение пропуск-. ной способности.Для этого в систему передачи дискретной информации, содержащую на передающей стороне источник дискретной инфор.мации, формирователь импульсного сигнала и блок синхронизации, а на приемной стороне - линейный усилитель, две ветви, каждая из которых состоит из последовательно соединенных блока оптимальной обработки сигнала и выпрямителя, а также решающий блок, входы которого соединены с выходами блока формирования напряжения порога и блока восстановления границ линейных посылок, входы которых соединены вместе, и последовательно соединенные формирователь двоичного сигнала и потребитель дискретной информации, на передающей стороне введен кодер, а на приемной стороне - детектор фазоразностного сигнала, сумматор, элемент ИЛИ, декодер и регистратор ошибок, при этом источник дискретной информации через кодер подключен к входу формирователя импульсного сигнала, выход блока синхронизации соединен с другим входом кодера, выход линейного усилителя подключен к входу детектора фазоразностного 20 сигнала, выходы которого подключены к входам блоков оптимальной обработки сигнала, выходы выпрямителей подключены к входам сумматора и входам элемента ИЛИ,выход сумматора подключен к другому входу решающего блока, выходы которого подключены к входам регистратора ошибок через декодер - к входам формирователя двоичных сигналов, выход элемента ИЛИ подключен к входу блока формирования напряжения порога и дополнительному входу декодера, другой дополнительный вход которого соединен с выходом блока восстановления границ линейных посылок, другой выход декодера подключен к другому входу регистратора ошибок, причем формирователь импульсного сигнала выполнен в виде формирователя трехпозиционного фазоразностного сигнала, а решающий блок - в виде блока принятия троичных решений.Кодер выполнен в виде преобразователя основания сигнала, синхронизируюшие входы которого соединены с выходами формирователя синхросигнала линейных посылок и формирователя синхросигнала кодовых групп, при этом вход формирователя синхросигнала линейных посылок соединен с другим выходом формирователя синхросигнала кодовых групп, вход которого соединен с выходом блока синхронизации.Декодер выполнен в виде обратного преобразователя основания сигнала, синхронизирующие входы которого соединены с выходом блока восстановления границ кодовых групп и выходом блока восстановления границ информационных посылок, вход которого соединен с выходом блока восстановления границ кодовых групп, входы которого соединены с выходом элемента ИЛИ и выходом блока восстановления границ линейныхых посылок.Кроме того, регистратор ошибок выполнен в виде последовательно соединенных элемента ИЛИ, первого счетчика и блока индикации, другой вход которого соединен с вторым входом первого счетчика через второй счетчик, причем входы элемента ИЛИ и второй вход первого счетчика соединены с выходами решающего блока, а другой вход второго счетчика соединен с выходом блока восстановления границ кодовых групп.На чертеже приведена структурная электрическая схема предлагаемой системы,Система передачи дискретной информации содержит на передающей стороне источник 1 дискретной информации, блок 2 синхронизации, кодер 3, формирователь 4 импульсного сигнала, выполненный в виде формирователя трехпозиционного фазоразностного сигнала, а на приемной стороне - линейный усилитель 5, блоки 6 и 7 оптимальной обработки сигнала, выпрямители 8 и 9, решающий блок 10, выполненный в виде блока принятия троичных решений, блок 11 формирования напряжения порога, блок 2 восстановления границ линейных посылок, формирователь 13 двоичного сигнала, потребитель 14 дискретной информации, детектор 15 фазоразностного сигнала,4сумматор 16, элемент ИЛИ 17, декодер 18 регистратор 19 ошибок.Кодер 3 содержит преобразователь 20основания сигнала, формирователь 21 синхросигнала линейных посылок, формирователь 22 синхросигнала кодовых групп, декодер 18 содержит обратный преобразователь 23 основания сигнала, блок 24 восстановления границ кодовых групп, блок 25 восстановления границ информационных посылок, регистратор 19 ошибок содержит элемент ИЛИ 26, первый счетчик 27, блок 28 индикации и второй счетчик 29.Система работает следующим образом.Двоичный цифровой сигнал источника1 поступает в преобразователь 20. Из периодической последовательности импульсов блока 2 синхронизации в формирователе 22 и формирователе 21 кодера 3 формируются две периодические последовательности импульсов, следующих с частотой кодовых групп и с частотой линейных посылок, На 20 выходе преобразователя 20 формируютсядве импульсные последовательности, используемые в формирователе 4 для создания трехпозиционного фазоразностного сигнала.Сформированный таким образом на передающей стороне трехпозиционный фазоразностный сигнал поступает через линейный усилитель 5 приемной стороны в детектор 15. Выделенные детектором 15 духуровневые сигналы, несущие в совокупности информацию о трехуровневом входном сигзц нале, поступают после обработки в блоках6 и 7 и выпримителях 8 и 9 в сумматор 16, который осуществляет операцию сложения выходных сигналов выпрямителей 8 и 9.Выходное напряжение сумматора 6 поступает на решающий блок 10. Выходные сигЗ налы выпрямителей 8 и 9 поступают такжечерез элемент ИЛИ 17 на блок 11 для управления формированием пороговых напряжений и блок 12 - для формирования синхросигнала линейных посылок.аВ решающем блоке 1 О на основании поступающих на его входы сигналов формируются решения о приеме троичных символов, Эти решения поступают в декодер 18 на обратный преобразователь 23. Его нормаль ная работа обеспечивается последовательностями импульсов, поступающих с блока 24 и блока 25. Полученные в результате обратного преобразования троичных решений в довичные два цифровых потока с выходов 50обратного преобразователя 23 поступают на формирователь 13. С помощью этих потоков формирователь 13 создает для потребителя 14 сигнал, совпадаюгций по форме с исходным. Контроль за качеством прохождения информации на участке регенерации осуществляется в регистраторе 19 ошибок. Решения, принятые в решающем блоке О по второму и третьему троичным символам, через элемент ИЛИ 26 сбрасывают первый счетчик 27, счетный вход которого управляется импульсами решений по первому троичному символу. Блок 28 индикации усредняет показания первого счетчика 27 и регистрирует вероятность появления ошибок. Ошибки, имеющиеся в принимаемом сигнале, обнаруживаются вторым счетчиком 29 по появлению запрещенной кодовой группы, Для этого на счетный вход второго счетчика 29 подаются импульсы решений по первому троичному символу, а сброс его в исходное состояние осуществляется импульсами, поступающими с блока 24.Предлагаемая система позволяет повысить пропускную способность, так как при снижении в полтора раза линейной скорости не требует введения в сигнал дополнительной информации для формирования синхросигнала частоты линейных посылок и обнаружения ошибок.Формула изобретения1, Система передачи дискретной информации, содержащая на передающей стороне источник дискретной информации, формирователь импульсного сигнала и блок синхронизации, а на приемной стороне - линейный усилитель, две ветви, каждая из которых состоит из последовательно соединенных блока оптимальной обработки сигнала и выпрямителя, а также решающий блок, входы которого соединены с выходами блока формирования напряжения порога и блока восстановления границ линейных посылок, входы которых соединены вместе, и последовательно соединенные формирователь двоичного сигнала и потребитель дискретной информации, отличающаяся тем, что, с целью повышения пропускной способности, на передающей стороне введен кодер, а на приемной стороне - детектор фазоразностного сигнала, сумматор, элемент ИЛИ, декодер и регистратор ошибок, при этом источник дискретной информации через кодер подключен к входу формирователя импульсного сигнала, выход блока синхронизации соединен с другим входом кодера, выход линейного усилителя подключен к входу детектора фазоразностного сигнала, выходы которого подключены к входам блоков оптимальной обработки сигнала, выходы выпрямителей подключены к входам сумматора и входам элемента ИЛИ, выход сумматора подключен к другому входу решающего блока, выходы которого подключены к входам регистратора ошибок и через декодер -к входам формирователя двоичных сигналов,выход элемента ИЛИ подключен к входу5 блока формирования напряжения порога идополнительному входу декодера, другойдополнительный вход которого соединен свыходом блока восстановления границ линейных посылок, другой выход декодера подключен к другому входу регистратора оши 1 Обок, причем формирователь импульсного сигнала выполнен в виде формирователя трехпозиционного фазоразностного сигнала, арешающий блок - в виде блока принятиятроичых решений.2, Система по и. 1, отличающаяся тем,что кодер выполнен в виде преобразователяоснования сигнала, синхронизирующие входы которого соединены с выходами формирователя синхросигнала линейных посылоки формирователя синхросигнала кодовыхгрупп, при этом вход формирователя синхросигнала линейных посылок соединен с другим выходом формирователя синхросигнала кодовых групп, вход которого соединенс выходом блока синхронизации.3. Система по пп. 1 и 2, отличающаясятем, что декодер выполнен в виде обратногопреобразователя основания сигнала, синхронизирующие входы которого соединеныс входом блока восстановления границ кодовых групп и выходом блока восстановлеЗО ния границ информационных посылок, входкоторого соединен с выходом блока восстановления границ кодовых групп, входы которого соединены с выходом элемента ИЛИи выходом блока восстановления границ линейных посылок.4. Система по пп. 1, 2 и 3, отличающаясятем, что регистратор ошибок выполнен в виде последовательно соединенных элементаИЛИ, первого счетчика и блока индикации,другой вход которого соединен с вторым4 О входом первого счетчика через второй счетчик, причем входы элемента ИЛИ и второйвход первого счетчика соединены с выходами решающего блока, а другой вход второго счетчика соединен с выходом блока восстановления границ кодовых групп.45 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРМо 524469, кл. Н 04 1. 27/22, 1973 (прототип),Составитель Е. Петрова Редактор Е. Дичинская Техред А. Бойкас Корректор Г. Решетник Заказ 1464/80 Тираж 698 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5 Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2363577, 20.05.1976

ПОРОХОВ ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: H04L 5/00

Метки: дискретной, инфор-мации, передачи

Опубликовано: 30.03.1981

Код ссылки

<a href="https://patents.su/4-818026-sistema-peredachi-diskretnojj-infor-macii.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи дискретной инфор-мации</a>

Предыдущий патент: Система передачи дискретной информа-ции

Следующий патент: Многопозиционное коммутирующееустройство

Случайный патент: Ультразвуковой резонансный толщиномер