Дискретно-аналоговый фурье-преоб-разователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 813307

Автор: Бабенко

Текст

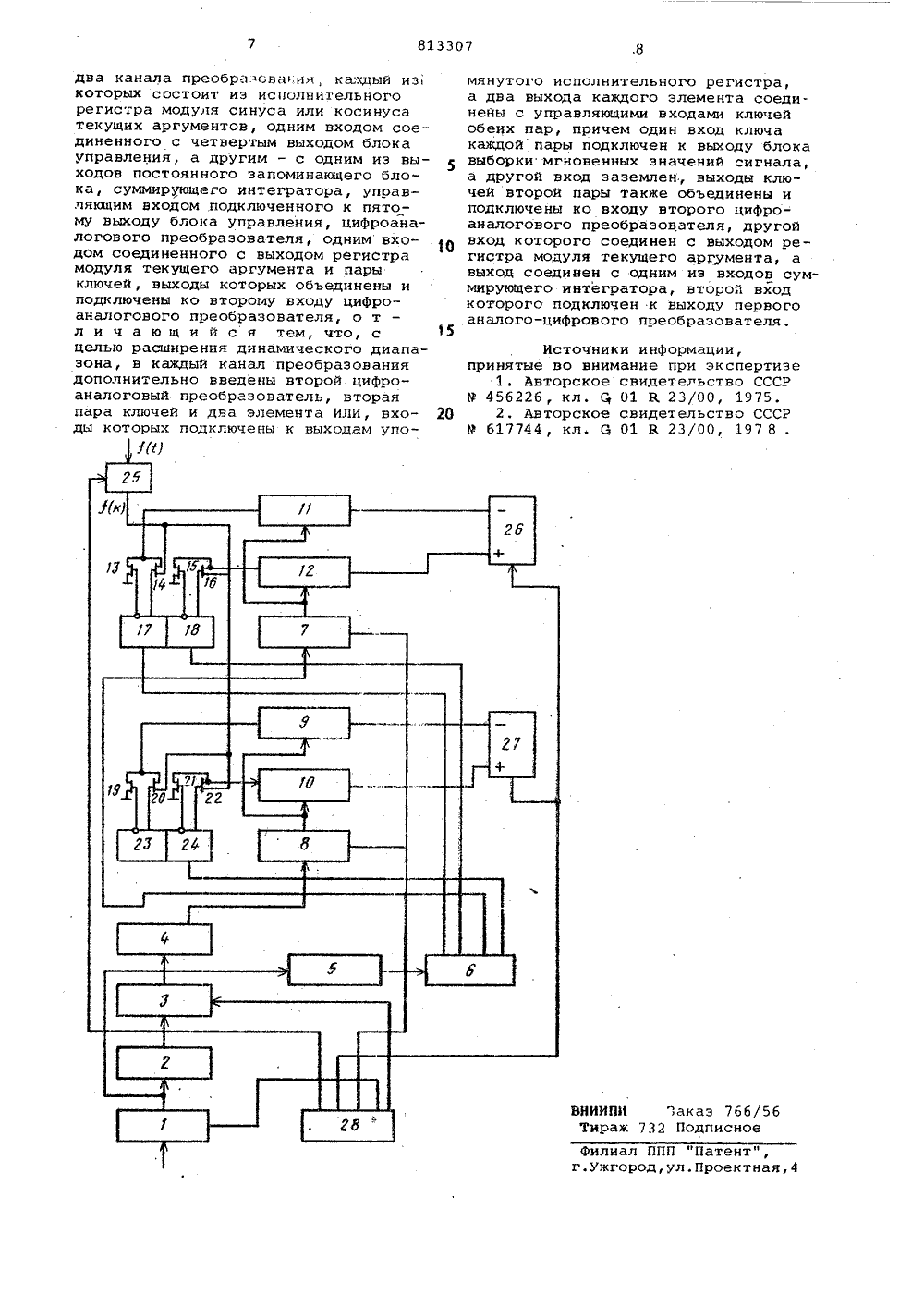

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИ ОЙЯЬСТВУСоюз Севетскик Социалистичесинк Республик(61) Дополнительное к авт. саид-ву(22) Заявлено 24.04.79(21) 2756637)18-21с присоединением заявки ИУ(М)М, Кл. с 01 К 23/16 о Государственник коинтет СССР по аелаи нзобретеннй н открытая( 54 ) ДИСКРЕТНО-АНАЛОГОВЫЙ ФУРЬЕ-ПРЕОБРАЗОВАТЕЛЬ Изобретение относится к вычисли-.тельной технике и может быть использовано для определения коэффициентовФурье исследуемого сигнала.%Известен Фурье-преобразователь,в котором генерация синусных и косинусных коэффициентов объединяется сумножителями в виде резисторно-переключающейся ячейки, В таком устройстве коэффициенты Фурье определяютсядля всех частот анализа (1.Недостаток этого устройства заключается в невысоком динамическом диапазоне.Известно другое устройство, содержащее блок выборки мгновенных значений сигнала, суммирующие интеграторы,резисторные матрицы (т.е. цифроаналоговые преобразователи, регистр номера частоты, сумматор, регистр адреса весового коэффициента, постоянный запоминакщий блок-схему управления, позволякщий осуществлять перестройку частоты по заданной программе 1.21,Недостатком такого устройства является несимметричная нагрузка инверсных входов операционного усилителя, что приводит к смещению его.выходного напряжения (и, как след- ЗО ствие этого - к уменьшению динамического диапазона устройства по выходу) при отсутствии сигнала на входе.Цель изобретения - увеличение динамического диапазона.Для достижения указанной цели в дискретно-аналоговый Фурье-преобразователь, содержащий блок выборки мгновенных значений сигнала, управлякщий вход которого соединен с первым выходом блока управления, последовательно соединенные регистр номера частоты, сумматор; регистр номера весового коэффициента и постоянный эапоминакщий блок, блок формирования знаков, выход которого соединен с исполнительным регистром знаков, а вход .подключен к объединенным выходам регистра номера частоты и регистра номера весового коэффициента, управляющие входы которых соединены соответственно со вторым и третьим выходами блока управления, два канала преобразования, каждый из которых состоит из исполнительного регистра модуля синуса или косинуса текущих аргументов, одним входом соединенного с четвертым выходом блока управления, а другим - с одним из выходов постоянного запоминающегоблока, суммирующего интегратора, упявляющим входом подключенного к пятому выходу блока управления, цифроаналогового преобразователя, однимвходом соединенного с выходом регистрамодуля текущего ар",умента и парыключей, выходы котОрых объединены Иподключены ко второму входу цифроаналогового преобразователя, в каждыйканал преобразования дополнительновведены второй цифроаналоговый преобразователь, вторая пара ключей идва элемента ИЛИ, входы которых подключены к выходам исполнительного регистра знакон, а два выхода каждогоэлемента соединены .с управляющимивходами ключей обеих пар, причем одинвход ключа каждой пары подключен квыходу блока выборки мгновенных значений сигнала, а другой вход заземлен, выходы ключей второй пары такжеобъединены и подключены ко входу второго цифроаналогового преобразователя, другой вход которого соединен свыходом регистра модуля текущего аргумента, а выход соединен с одним извходов суммирующего интегратора, второй вход которого подключен к выходупервого аналого-цифрового преобразователя.На чертеже представлена Функциональная схема предлагаемого Фурьепреобразователя.устройство содержит;:регистр 1 номера частоты, сумматор 2, регистр 3номера весового;коэффициента, постоянный запоминающий блок 4 для хранения синусных (косинусных) значенийвесовых коэффициентов, блок 5 формирования знаков, исполнительные регистры 6 знаков и модулей синуса икосинуса текущих аргументов 7 и 8,цифроаналоговые преобразователи9-12, выполненные в виде декодирующих цифроаналоговых управляемых(с помощью ключей) делителей к к,ключи 13-16, элементы ИЛИ 17 и 18,ключи 19-22, элементы ИЛИ 23 и 24,блок 15 выборки мгновенных значенийсигнала, суммирующий инт гратор 26синусной составляющей преобразованияФурье, суммирующий интегратор 27 коеинусной составляющей преобразованияФурье и блок 28 управления,При изменении кода номера частотыР этот код записывается импульсом счетвертого выхода блока 28 управления в регистр 1 номера частоты передначалом обработки нулевого отсчетареализации и сохраняется до началаобработки нулевого отсчета следующейреализации. Перед началом обработкинулевого (по порядковому номеру безразмерного времени К ) отсчета реализации импульсаюж с выхода блока 28управления сбрасываются в нуль регистр 3 номера весового коэффициента,исполнительные регистры 7 и 8 и суммирующие интеграторы 26 и 27. После этого содержимое регистра Э номера весового коэффициента суммируется по модулю й в сумматоре 2 с содержимым регистра 1 номера частоты. В регистре 3 номера весового коэффициента Формируется полный номер (адрес)весового коэффициента по модулю й,и два старших разряда определяют знаксинусных и косинусных весовых коэффициентов.Результат суммирования следующимимпульсом управления, поступадцим спятого выхода блока 28 управления,переписывается в регистр Э номера весового коэффициента, По номеру весового коэффициента из постоянного запоминающего блока 4 синусных и косинусных значений весовых коэФфициентоввызываются модули синусов и косинусов. Следующим импульсом с третьеговыхода блока 28 управления модули весовых коэфФициентов и их знаки записываются в исполнительный регистр 7для модуля синуса и в регистр 8для модуля косинуса. С этого моментавремени начинается обработка К-того 25 отсчета исследуемого сигнала, т.е.код модуля синуса и код модуля коси -нуса (для фиксированной частоты Ри момента времени К) подается на управляющие входы ключей цифроаналоЗ 0 говых преобразователей 9 и 10 и 11и 12. Отсчет сигнала 1(М), декодированный на значение весового коэфФициента зп - ,РК и со - " РК для мо 2 Е 2мента времени к, подводится к инверсным входам интеграторов 26 и 27.В зависимости от знака весовыхкоэффициентов (определяемого двумястаршими разрядами полного номера весового коэффициента) блок 5 Формирования знаков формирует признак знака и через исполнительный регистр знаков б (в виде импульса, равного потенциалу логической единицы, по длительности совпадающего с длитель -ноетью интервала дискретизации) под водится на элементы ИЛИ 17, 18, 23 и24.При отрицательном значении весоного коэффициентазщ И.рк импульс сКпервого выхода исполнительного регистра знаков б (соответствукщий уровню логической единицы) подводится к элементу ИЛИ 17, и на ее прямом выходе появляется тот же импульс, который открывает ключ 14, обеспечивая прохождение отсчета. сигнала 1(К), с выхода блока выборки мгновенного значения сигнала 25 на вход цифроана- .логового преобразователя 11, где происходит его декодирование (взвешивание) по закону 1 з 1 п - РК и на 2 ГЮкопление в интеграторе 26.В то же самое время на инверсномвходе элемента ИЛИ 17 потенциал логического нуля, следовательно, ключ 13 закрыт, Для обеспечения симметрии ин813307 ВНИИПН "аказ 766 Тираж 732 Подписно Филиал ППП "Патент", .Ужгород,ул,Проектна два канала преобраэова.:ин, каждый изкоторых состоит из исполнительногорегистра модуля синуса или косинусатекущих аргументов, одним входом соединенного с четвертым выходом блокауправления, а другим - с одним из выходов постоянного запоминающего блока, суммирующего интегратора, управлякщим входом подключенного к пятому выходу блока управления, цифроаналогового преобразователя, одним входом соединенного с выходом регистрамодуля текущего аргумента и парыключей, выходы которых объединены иподключены ко второму входу цифроаналогового преобразователя, о тл и ч а ю щ и й с я тем что, с 15целью расширения динамического диапазона, в каждый канал преобразованиядополнительно введены второй. цифроаналоговый преобразователь, втораяпара ключей и два элемента ИЛИ, входы которых подключены к выходам упомянутого исполнительного регистра,а два выхода каждого элемента соединены с управляющими входами ключейобеих пар, причем один вход ключакаждой пары подключен к выходу блокавыборки мгновенных значений сигнала,а другой вход заземлен, выходы ключей второй пары также объединены иподключены ко входу второго цифроаналогового преобразователя, другойвход которого соединен с выходом регистра модуля текущего аргумента, авыход соединен с одним из входов суммирующего интегратора, второй входкоторого подключен к выходу первогоаналого-цифрового преобразователя,Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 456226, кл.01 К 23/00, 1975. 2, Авторское свидетельство СССР Р 617744, кл. 3 01 К 23/00, 197 8

СмотретьЗаявка

2756637, 24.04.1979

ПРЕДПРИЯТИЕ ПЯ Р-6292

БАБЕНКО ВЛАДИМИР ИОСИФОВИЧ

МПК / Метки

МПК: G01R 23/16

Метки: дискретно-аналоговый, фурье-преоб-разователь

Опубликовано: 15.03.1981

Код ссылки

<a href="https://patents.su/4-813307-diskretno-analogovyjj-fure-preob-razovatel.html" target="_blank" rel="follow" title="База патентов СССР">Дискретно-аналоговый фурье-преоб-разователь</a>

Предыдущий патент: Устройство для контроля высшихгармонических составляющихэлектрического toka

Следующий патент: Измеритель фазовых шумов смеси-телей

Случайный патент: Установка для разбора пакетов плоских предметов