Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 783789

Авторы: Антоненко, Бердинских, Моисеева, Селезнев

Текст

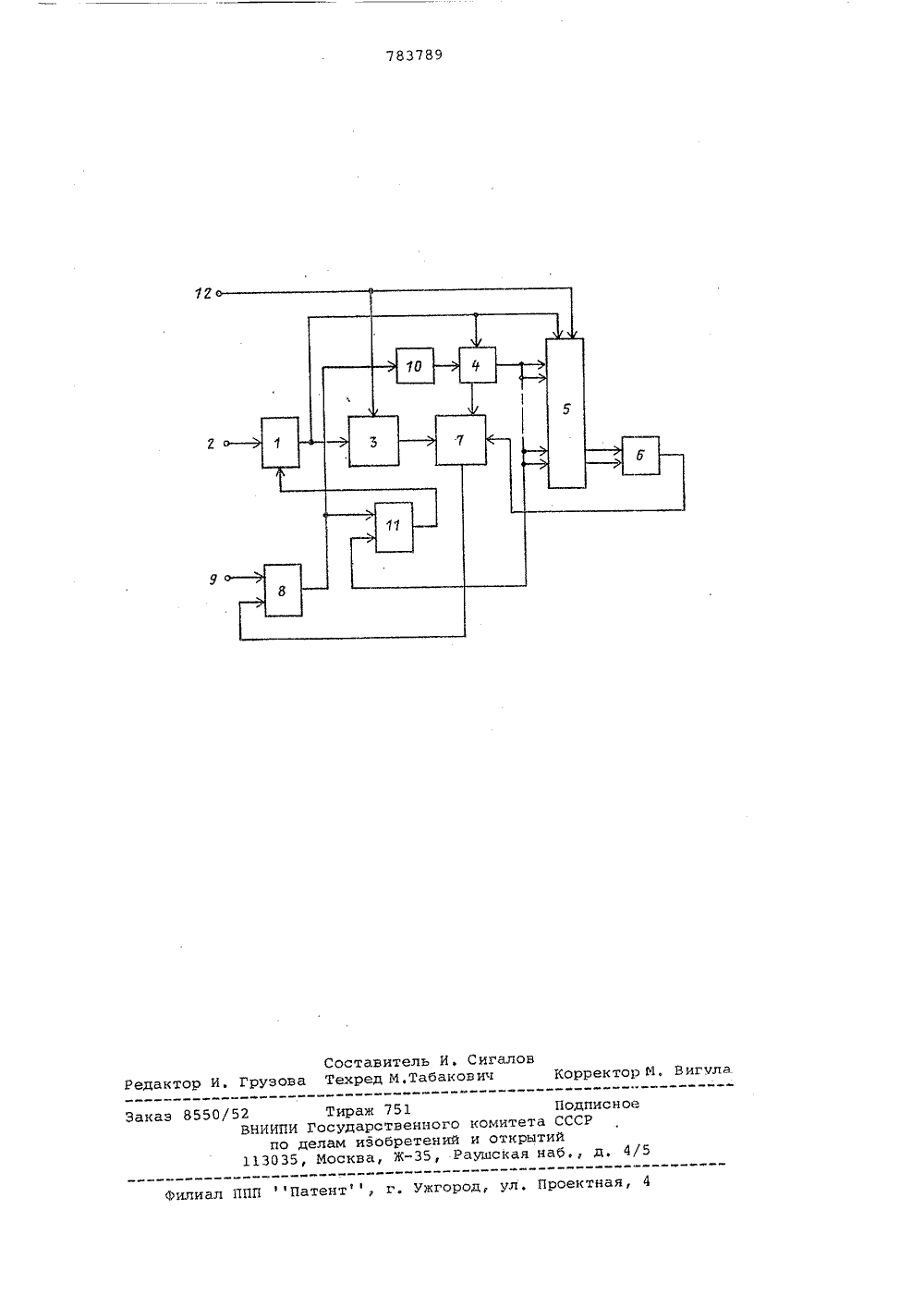

Союз Советских Социалистических Республик(23) ПриоритетОпубликовано 30,1180, Бюллетень М 44Дата опубликования описания 30,1180 С 06 Р 5/04 Государственный комитет СССР по делам изобретений н открытий(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫИ Изобретение относится к вычислительной технике и может быть исполь зовано для преобразования последовательного двоичного кода в параллельный. 5 В вычислительных машинах, а также в системах и комплексах часто возникает необходимость передачи информации между блоками к системам. Более экономичной является передача информации в последовательном коде, так как для этого требуется гораздо меньШе оборудования, чем при передаче информации в параллельном кодеНо поскольку, с целью повышения быстродействия, обработку информации в вычислительных устройствах ведут в параллельном коде, то для связи передающих и обрабатывающих устройств разработаны преобразователи последователь ного кода в параллельный.В .частности, известен преобразо- ватель последовательного двоичного кода в параллельный двоично-десятичный, содержащий счетчик двоичных раз рядов последовательного кода, старшие два разряда которого соединены с одним из входов дешифратора, генератор тактовых импульсов, выход котооого соединен со входами, счетчика весовых эквивалентов, и выходной регистр, в который, с целью повышения надежности, введены схема сравнения, счетчик повторения, блок запрещения тактового импульса младшего разряда и блок выделения младшего разряда последовательного кода 1) .Это устройство отличается узкими функциональными возможностями, и в нем отсутствует контроль достоверности принимаемой информации.Наиболее близким по технической сущности к заявляемому преобразователю является преобразователь последовательного двоичного кода в параллельный, содержащий сдвиговый регистр, принимающий последовательно передаваемые шестираэрядные слова. Прием длится до тех пор, пока слово полностью не загрузитсяв сдвиговый регистр. В преобразователе имеется также схема синхрониэирующих импульсов, с помощью которых осуществляются в сдвиговом регистре сдвиги информации. Как только сдвиговый регистр заполнится всеми шестью разрядами слова, схема синхрониэирующих импульсов выдает импульс в буферную, память для приема информации в параллельной Форме 2 .Схема данного преобразователя обеспечивает преобразование последовательного потока информации в блоки параллельной ныходной информации. Поток последонательной входной информации имеет большое количество знаков, каждый из которых содержит Б бит цифровой информации, которой предшествует начальный бит, предстанленный одним уровнем напряжения и за которым следует по крайней мере один бит остановки, представленный другим уровнем напряжения. Преобразователь содержит сдвиговый регистр со входным зажимом синхронизации и входным информационным зажимом, накоторый подается поток последовательной входной информации. Регистр имеет И+Х каскадов, где Х соответствует числу начальных и конечных битон.у каждого каскада регистра есть соответствующий входной зажим. При помощи установочного входа И+Х каскадов сднигового регистра сбрасывают"ся н начальное состояние. Кроме того, имеется схема обнаружения начальных бит слова, выполненная в виде ждущего мультинибратора, упранляемый генератор и триггер управления, вход которого соединен с установочным входом преобразонателя, а выходс управляемым генератором.К недостаткам такого преобразователя относятся отсутствие контроля достоверности принимаемой информации, жесткая привязка к началу слова принимаемой информации, чтоможет привести к ныдаче потребителю ложной информации при наличии случайного сбоя в поступающей информации.Цель изобретения - повышение достоверности приема информации.Для достижения поставленной целив преобразователь последовательногокода в параллельный, содержащий сдвиговый регистр, триггер управления, дешифратор, управляемый генератор,причем информационный вход преобра" зователя соединен с информационным входом сднигового регистра, выходы которого подключены к входу дешифратора, установочный вход преобразователя соединен с нулевым входом триггера управления, выход которого связан со входдм управляемого генератора, введены первый и второй элементы И, блок контроля по нечетности, триггер включения и счетчик, Причем синхронизационный вход преобразователя соединен с первым входом первого элемента И, выход которого подключен к синхронизационным входам блока контроля по нечетности, счетчика и сдвигового регистра. Выход управляемого, генератора соединен совторым синхронизационным входом счетчика, первый выход которого связан с установочным входом сдвнгового регистра и с единичным входом триггера включения, выход триггера управпения - с нулевым входом триггера. включения, выход которого соединен со вторым входом первого элемента И. Информационный вход преобразователя соединен с информационным входом блока контроля по нечетности, выход которого связан с первым входом второго элемента И, выход которого соединен со счетным входом триггера управления. Второй выход счетчика подключен к второму входу второго элемента И, третий вход которого соединен с выходом дешифратора,Схема преобразователя последовательного кода в параллельный изображена на чертеже.Она содержит первый элемент И 1, первый вход которого соединен со входом 2 синхронизации преобразователя, а выход - с синхронизационным нходом блока 3 контроля по нечетности входом счетчика 4 и входом синхронизации сднигоного регистра 5, Выходы первых двух младших разрядов регистра 5 соединены со входом дешифратора б, выполняющего функцию обнаружения начальных бит слова, выход которого подключен к третьему входу второго элемента И 7. Выход элемента И 7 соединен со счетным входом триггера 8 управления, вход установки нуля которого соединен с установочным входом 9 преобразователя Выход триггера 8 управления связан со входом управляемого генератора 10 и входом установки нуля триггера 11 включения. Информационный вход 12 последовательного ввода данных преобразователя соединен с информационным входом блока 3 контроля нечетности и информационным входом сднигового регистра 5.Преобразователь работает следующим образом.Запуск преобразователя осуществляется импульсом, подаваемым на вход 9. Этим импульсом на выходе триггера 8 управления устанавливается логический О, запускающий управляемый генератор 10. Управляемый генератор 10 формирует импульсы. Счетчик 4 при поступлении определенного числа импульсов управляемого генератора 10 формирует импульс, поступающий на входы установки нуля сдвигоного регистра 5, и устанавливает на его выходах логический О. Этот же импульс на выходе триггера 11 включения устанавливает логическую 1, разрешающую прохождение импульсов синхронизации со входа 2 преобразователя на нь,ход первого элемента И 1.По импульсам синхронизации, каждьй из которых соответствует определенному разряду последонателнио передаваемого слона, осущестнляется ввод слова младшими разрядами вперед в сдниговый регистр 5 и ныполформула изобретения 15 20 25 30 35 45 50 55 са со счетчика 4. Последний, обнаружив конечные биты преобразуемого слова, выдает импульс на входы установки нуля сдвигового регистра 5 дляего исходной установки, тем самым Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 562814 кл. 6 06 Г 5/04, 20,05,75,2. Патент США 9 3946379,кл, 340-347, опублик. 1976 (прототип).60 Няется контроль принимаемого словаблоком 3 контроля нечетности. Кактолько начальные биты преобразуемого слова установятся в соответствующих для них разрядах сдвиговогорегистра 5, дешифратор 6 обнаружения начальных бит слова выдаст наодин из входов вторсго элемента И7 логическую 1. При этом надругой вход второго элемента И 7 свыхода блока 3 контроля нечетности поступит также логическая 1, если преобразуемое слово не было искажено при передаче, Счетчик 4 определяет отсутствие импульсов синхронизации на входе 2 синхронизации, так как конечные биты преобразуемого слова не сспровождаются импульсами синхронизации, и формирует импульс, поступающий на третий вход второго элемента И 7. С выхода элемента И 7 этот импульс подается на счетный вход триггера 8 управления и устанавливает на его выходе логическую 1,. которая устанавливает на выходе триггера 11 включения логический О, запрещающий прохождение импульсов синхронизации через первьй элемент И 1, и выключает управляемый генератор 10.Пс окончании указанного процесса преобразования на выходах сдвигового регистра 5 будет находиться параллельный код преобразованного слова.В случае обнаружения блоком 3 ошибки в преобразуемом слове второй элемент И 7 будет закрыт (логическим О с выхода блока 3 контроля нечетности для прохождения импульподготовив преобразователь к повторному преобразованию. При запуске преобразователя асинхронно с поступакщим на его входсловом, т.е. импульс .запуска на входе 9 появляется в момент времени, когда уже часть слова была передана, в нем выполняется процесс, аналогичный случаю обнаружения ошибки в преобразуемом слове, с той лишь разны" цей, второй элемент И 7 закрыт логическим О по крайней мере от дешифратора.Изобретение отличается высокой достоверностью прицимаемой информа 1 ии вВведение двух элементов И, блока контроля нечетности, триггера вклю" чения и счетчика позволило намного повысить достоверность принимаемой информации и обеспечить асинхронную работу преобразователя по отношению к источнику последовательно передаваемого слова.Высокая достоверность принимаемого слова обеспечивается блоком контроля нечетности, так как в передаваемом слове кроме начальных, конечных и информационных бит есть по крайней мере один контрольный бит, который совместно с информационными битами анализируется блоком контроля нечетности. Преобразователь последовательного кода в параллельный, содержащий сдвиговый регистр, триггер управления, дешифратор, управляемый генератор, причем информационный вход преобразователя соединен с информационным входом сдвигового регистра, выходы которого соединены со входом дешифратора, установочный вход преобразователя соединен с нулевым входом триггера управления, выход которого соединен со входом управляемого генератора, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности, в него введены первый и второй элементы И, блок контроля по нечетности, триггер включения и счетчик, причем синхронизационный вход преобразователя соединен с первым входом первого элемента И, выход которого соединен с синхронизационными входами блока контроля по нечет- ности, счетчика и сдвигового регистра, выход управляемого генератора соединен со вторым синхронизационным входом счетчика, первый выход которого соединен с установочным входом сдвигового регистра и с единичным входом триггера включения, выход триггера управления соединен с нулевым входом триггера включения, выход которого соединен со вторым входом первого элемента И, информационный, вход преобразователя соединен с информационным входом блока контроля по нечетности, выход которого соединен с первым входом второго элемента И, выход которого соединен со счетным входом триггера управления, второй выход счетчика соединен со вторым входом второго элемента И, третий вход которого соединен с выходом дешифратора.783789Составитель И. СигаловРедактор И. Грузова Техред М,Табакович Корректор М, Вигила Заказ 8550/52 Тираж 751 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д, 4/5Филиал ППП Патент г. Ужгород, Ул. Проектная, 4

СмотретьЗаявка

2705602, 03.01.1979

ПРЕДПРИЯТИЕ ПЯ А-7240

БЕРДИНСКИХ ВЛАДИМИР АЛЕКСАНДРОВИЧ, МОИСЕЕВА АЛЛА ВАСИЛЬЕВНА, АНТОНЕНКО НЕЛЛЯ ПЕТРОВНА, СЕЛЕЗНЕВ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G06F 5/04

Метки: кода, параллельный, последовательного

Опубликовано: 30.11.1980

Код ссылки

<a href="https://patents.su/4-783789-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь двоичного кода в двоично-десятичный

Следующий патент: Устройство для сравнения чисел

Случайный патент: Устройство для измерения температуры