Устройство для деления десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

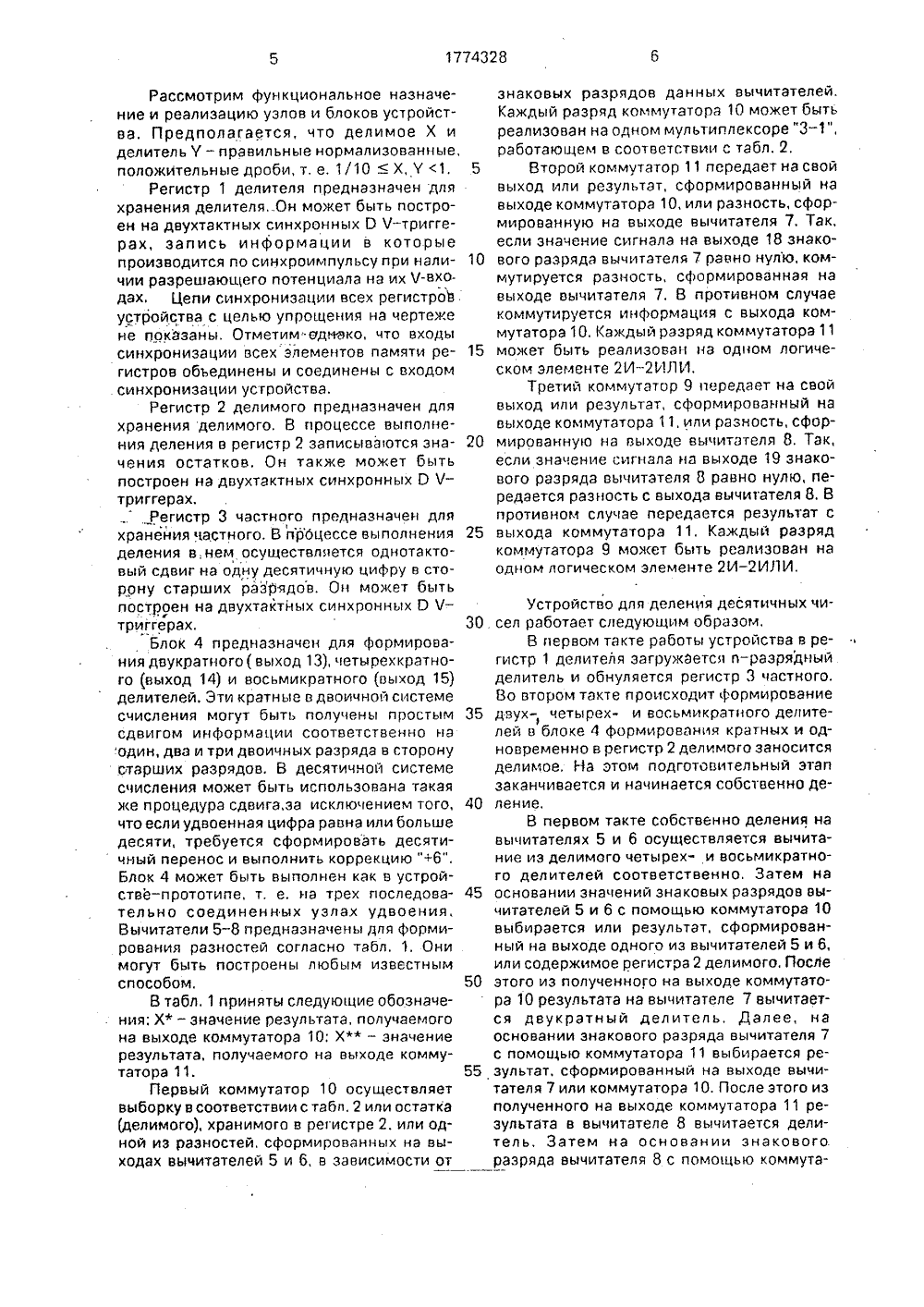

(54) УСТРОЙСТВО ТИЧНЫХ ЧИСЕЛ (57) Изобретение ной технике и мож быстрого деления изобретения явля турных затрат на Устройство содер го, делителя и час ния кратных дели 5-8, первый и вто нововведенный ко Я ДЕЛЕНИЯ ДЕСЯ(21) 4811735/24(71) Научно-исследовательский инсэлектронных вычислительных машин(56) Авторское свидетельство СССРМ 1241235, кл. 6 06 Р 7/52, 1984.Авторское свидетельство СССРМ 1688239, кл, 6 06 Р 7/52, 1989,относится к вычислительет быть использовано для десятичных чисел. Целью ется сокращение аппарареализацию устройства, жит регистры 1 - 3 делимотного, блок 4 формирователя, четыре вычитателя рой коммутаторы 10 - 11 и ммутатор 9, 1 ил. 2 табл.Изобретение относится к вычислительной технике и может быть использовано и риразработке быстродействующих устройствделения десятичных чисел.Известно устройство для деления десятичных чисел, содержащее регистры делимого, делителя и частного, блокформирования кратных, восемь вычитэтелей, сумматор и блок формирования цифрычастного, 10Недостатком известного устройства является большое количество аппаратуры,Наиболее близко к предлагаемому - устройство для деления десятичных чисел, содержащее регистры делимого, делителя и 15частного, два коммутатора, пять вычитателей, сумматор, блок формирования кратныхи блок формирования цифры частного, причем входы уменьшаемых первого и второговычитателей соединены с выходом регистра 20делимого и первым информационным входом первого коммутатора, выход которогосоединен с входами уменьшаемых третьего,четвертого и пятого вычитателей и первыминформационным входом второго коммутатора, второй, третий и четвертый информационные входы которого соединенысоответственно с выходами третьего, четвертого и пятого вычитателей, вход вычитаемого третьего вычитателя соединен с 30первым выходом блока формирования кратных и первым информационным входомсумматора, вход вычитаемого четвертоговычитателя соединен с выходом регистраделителя, входом блока формирования 35кратных и вторым информационным входомсумматора, выход которого соединен с входом вычитаемого пятого вычитателя. второйи третий выходы блока формирования кратных соединены с входами вычитэемых соответственно первого и второго вычитателей,выходы которых соединены с вторым итретьим информационными входами соответственно первого коммутатора, выходвторого коммутатора соединен с информационным входом регистра делимого, управляющий вход устройства соединен свходами разрешения записи регистров делимого, делителя и частного, выходы знаковых разрядов вычитателей соединены с 50входами блока формирования цифры частного, первый выход которого соединен синформационным входом младшего разряда регистра частного, а второй и третий выходы - с управляющими входами первого и 55второго коммутаторов соответственно,Недостаток известного устройства -большие аппарэтурные затраты,Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что в устройство для деления десятичных чисел, содеркащее регистры делимого, делителя и частного, два коммутатора, четыре вычитателя, блок формирования кратных, причем входы уменьшаемых первого и второго вычитателей соединены с выходом регистра делимого и первым информационным входом первого коммутатора, выход которого соединен с входом уменьшаемого третьего вычитателя и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом третьего вычитателя, вход которого соединен с первым выходом блока формирования кратных, второй и третий выходы которого соединены с входами вычитаемых первого и второго вычитателей, выходы которых соединены с вторым и третьим информационными входами соответственно первого коммутатора, выход регистра делителя соединен с входом блока формирования кратных и входом вычитаемого четвертого вычитателя, управляющий вход устройства соединен с входами разрешения записи регистров делимого, делителя и частного, введен третий коммутатор. выход которого соединен с информационным входом регистра делимого,выход второго коммутатора соединен с входом уменьшаемого четвертого вычитателя и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом четвертого вычитателя, выходы знаковых разрядов первого и второго вычитателей соединены соответственно с первым и вторым управляющими входами первого коммутатора и входами двух старших бит младшего разряда регистра частного, входы двух младших битмладшего разряда которого соединены с управляющими входами второго и третьего коммутаторов и выходами знаковых разрядов третьего и четвертого вычитателей соответственно.На чертеже приведена Структурная схема устройства для деления десятичных чисел.Устройство содержит регистры 1 - 3 делителя,. делимого и частного соответствен, но, блок 4 формирования кратных, вычитатели 5-8 с первого по четвертый соответственно; первый 10, второй 11 и третий 9 коммутаторьг, управляющий вход 12 устройства, выходы 13-15 соответственно двукратного, четырехкратного и восьмикратного делителей блока 4, выходы 1 бзнаковых разрядов вычитателей 6, 5, 7 и 8 соответственно, 17743285 10 15 20 25 Рассмотрим функциональное назначение и реализацию узлов и блоков устройства, Предполагается, чта делимое Х иделитель У - правильные нормализованные,положительные дроби, т. е, 1/10Х, У 1,Регистр 1 делителя предназначен дляхранения делителя,.Он может быть построен на двухтактных синхронных 0 Ч - триггерах, запись информации в которыепроизводится по синхроимпульсу при наличии разрешающего потенциала на их Ч-вхо.дах. Цепи синхронизации всех регистровустройства с целью упрощения на чертежене показаны. Отметим"одеко, что входысинхронизации всех элементов памяти регистров абьединены и соединены с входомсинхронизации устройства.Регистр 2 делимого предназначен дляхранения делимого. В процессе выполнения деления в регистр 2 записываются значения остатков. Он также может бытьпостроен на двухтактных синхронных 0 Чтриггерах,Регистр 3 частного предназначен дляхранения частного, В процессе выполненияделения в, .нем осуществляется однотактовый сдвиг на одну десятичную цифру в сторрну старших разрядов. Он может бытьпостроен на двухтактных синхронных О Ч -триггерах,Блок 4 предназначен для формирования двукратного (выход 13), четырехкратного (выход 14) и восьмикратного (выход 15)делителей, Эти кратные в двоичной системесчисления могут быть получены простымсдвигом информации соответственно наодин, два и три двоичных разряда в сторонустарших разрядов, В десятичной системесчисления может быть использована такаяже процедура сдвига,эа исключением того,что если удвоенная цифра равна или большедесяти, требуется сформировать десятичный перенос и выполнить коррекцию "+6",Блок 4 может быть выполнен как в устройстве - прототипе, т. е, на трех последовательно соединенных узлах удвоения,Вычитатели 5 - 8 предназначены для формирования разностей согласно табл. 1. Онимогут быть построены любым известнымспособом,В табл, 1 приняты следующие обозначения: Х - значение результата, получаемогона выходе коммутатора 10; Х - значениерезультата, получаемого на выходе коммутатора 11.Первый коммутатор 10 осуществляетвыборку е соответствии с табл, 2 или остатка(делимого), хранимого в регистре 2, или одной из разностей, сформированных на выходах еычитателей 5 и 6, в зависимости от знаковых разрядов данных вычитателей. Каждый разряд кол 1 лутатара 10 может быть реализован на одном мультиплексоре "3 - 1", работающем в соответствии с табл. 2.Второй коммутатор 11 передает на свой выход или результат, сформированный на выходе кол 1 мутатора 10, или разность, сформированную на выходе вычитателя 7, Так, если значение сигнала на выходе 18 знакового разряда вычитателя 7 равно нулю, коммутируется разность, сформированная на выходе еычитателя 7, В противном случае коммутируется информация с выхода коммутатора 10, Каждый разряд коммутатора 11 может быть реализован на одном логическом элементе 2 ИИЛИ.Третий коммутатор 9 передает на свой выход или результат, сформированный на выходе коммутатора 11, или разность, сформированнуа на выходе вычитателя 8. Так, если значение сигнала на выходе 19 знакового разряда вычитателя 8 равно нулю, передается разность с выхода вычитателя 8, В противном случае передается результат с выхода коммутатора 11, Каждый разряд коммутатора 9 может быть реализован на одном логическом элементе 2 И - 2 ИЛИ,Устройство для деления десятичных чи. сел работает следующим образам,В первом такте работы устройства в регистр 1 делителя загружается и - разрядный делитель и обнуляется регистр 3 частного, Во втором такте происходит формирование 35 двух- четырех- и восьмикратного делителей в блоке 4 формирования кратных и одновременно в регистр 2 делимого заносится делимое, На этом подготовительный этап заканчивается и начинается собственно де ление.В первом такте собственно деления навычитателях 5 и 6 осуществляется вычитание иэ делимого четырех- и восьмикратного делителей соответственно, Затем на 45 основании значений знаковых разрядов вычитателей 5 и 6 с помощью коммутатора 10 выбирается или результат, сформированный на выходе одного из вычитателей 5 и 6, или содержимое регистра 2 делимого, После 50 этого из полученного на выходе коммутатора 10 результата на вычитателе 7 вычитается двукратный делитель, Далее, на основании знакового разряда еычитателя 7 с помощью коммутатора 11 выбирается ре зультат, сформированный на выходе вычитателя 7 или коммутатора 10. После этого из полученного на выходе коммутатора 11 результата в вычитателе 8 вычитается делитель, Затем на основании знакового разряда вычитателя 8 с помощью коммута1774328 Таблица 1 Таблица 2 ный нэ выходе вычитателя 8 или коммутатора 11.Первый такт собственно деления заканчивается с приходом на вход 12 управляющих сигналов, по которым в регистре 3 5частного осуществляется однотактныйсдвиг информации на один десятичный разряд в сторону старших разрядов с одновременной записью в его младший разрядпервой (старшей) десятичной цифры частного, а также осуществляется запись результата (он является первым остатком),образованного на выходе коммутатора 9, сосдвигом на один десятичный разряд в сторону старших разрядов в регистр 2 делимого.Во всех остальных тактах собственноделения устройство работает аналогично.После выполнения и тактов в регистре 3частного формируется п - разрядное частное,Формула изобретенияУстройство для деления десятичных чисел, содержащее регистры делимого, дели теля и частного, два коммутатора, четыре вычитателя, блок формирования кратных, причем входы уменьшаемых первого и второго вычитателей соединены с выходом регистра делимого и с первым информационным 30 входом первого коммутатора, выход которого соединен с входом уменьшаемого третьего вычитателя и первым информационным входом второго коммутатора, второй инфор 35 мационный вход которого соединен с выходом третьего вычитателя, вход вычитаемого которого соединен с первым выходом блока формирования кратных, второй и третий выходы которого соединены с входами вычитаемых первого и второго вычитателей, выходы которых соединены с, вторым и третьим информационными входами соответственно первого коммутатора, выход регистра делителя соединен с входом блока формирования кратных и входом вычитаемого четвертого вычитателя, управляющий вход устройства соединен с входами разрешения записи регистров делимого, делителя и частного, о тл и ч а ю щ ее с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит третий коммутатор, выход которого соединен с информационным входом регистра делимого, выход второго коммутатора соединен с входом уменьшаемого четвертого вычитателя и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом четвертого вычитателя, выходы знаковых разрядов первого и второго вычитателей соединены соответственно с первым и вторым управляющими входами первого коммутатора и входами двух старших бит младшего разряда регистра частного, входы двух младших бит младшего разряда которого соединены с управляющими входами второго и третьего коммутаторов и выходами знаковых разрядов третьего и четвертого вычитателей.

СмотретьЗаявка

4811735, 09.04.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

БАРАН ЮРИЙ АЛЕКСАНДРОВИЧ, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: деления, десятичных, чисел

Опубликовано: 07.11.1992

Код ссылки

<a href="https://patents.su/4-1774328-ustrojjstvo-dlya-deleniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для деления десятичных чисел</a>

Предыдущий патент: Устройство для ранговой фильтрации

Следующий патент: Генератор случайных чисел

Случайный патент: Питательная среда для определения титра-коли молока и молочных продуктов