Преобразователь цифрового кода в последовательность импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

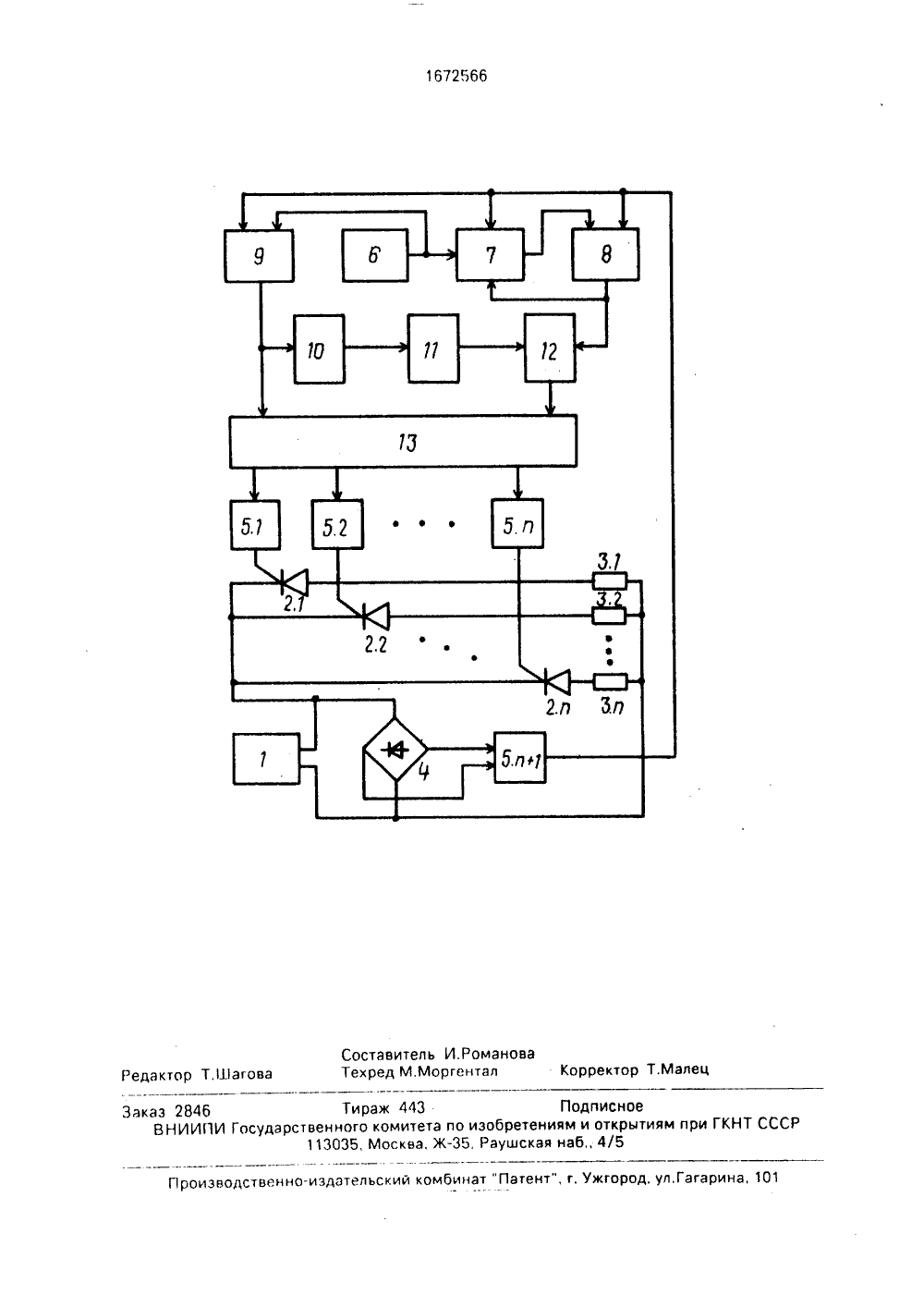

3 фФ СОГОЗ СО 11 РТСКИХ со 11 ИАлис 1 и 1 Гских РГ С 11 УБЛИК 51)5 Н 03 М 1/66 ИЯ 4 ы шение надеж авек ля при одноабаритов удешевленииНа чертесхема.Устройстния и коммуненных на ти е приведена кциональнд ГОСУДАРСТВЕН 11 ЫЙ КОМИТГТ110 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Институт оптики атмосферы СОАН СССР(56) Авторское свидетельство СССРМ 285379, кл, Н 03 М 1/04, 1969,Авторское свидетельство СССРМ 828396. кл. Н 03 М 1/ОС, 1981,(51) ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ПОСЛЕДОВАТЕЛЬНОСТЬ ИМПУЛЬСОВ(5 1) Изобретение относится к автоматизированным системам управления и автоматизации научных исследовании и может бытьиспользовано в качестве лногоканальногоэлектропривода различного назначения, например силового привода электротермических установок, Цел изобретения -повышение надежности работы преобразователя при одновременном снижении е 1 огабари гав и стоимости, Для достижения поставленной цели в преобразоьатель цифровога кода в последовательность импульсов,содержащий источник питания, диодныймост, резисторы нагрузки, опгронные ключи, тиристары, катоды которых через резиИзобретение относится к преобразователям цифрового кода в импульсы зажигания управляемых вентилей, например тиристаров, и мажет быть использовано в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований совместно с управляющей цифровой вычислительной машиной. как выходное устройство. 5 Ц 1672566 А стары нагрузки подключены к однои из шин источника питания и одной из шин входной диагонали диодного моста, другая шина которого соединена с другой шиной источника питания и анодами тиристоров, управляющие электроды которых соединены с выходами оптронных ключей, отдельный оптронный ключ, входы которого соединены с выходной диагональю диодного моста, последовательно соединенные генератор тактовых импульсов, управляемый делитель частоты счетчик, сумматор, второй вход счетчика соединен с вторым входом управляемого делителя частоты и выходом отдельного оптронного ключа, введены дешифратор, последовательно соединенные второй счетчик, оперативное запоминающее устройство постоянное запоминающее устройства, выход которого соединен с вторым входом сумматора, выход сумматора соединен с первыл 1 входом дешифратора, второй вход дешифратора соединен с выходом второго сцетчика, выходы дешифратора соединены с входами оптроных ключей, первый вход второго счетчика соединен с выходом отдельного оптроннога ключа, второй вход второго счетчика соединен с выходом генератора тактовых импульсоь. 1 ил,Цель изобретения - павы ности работы преобразоват временном снижении его во содержит источник 1 питатирующих элементов, выполристорах 2.1 - 2.п, и резисторовнагрузки 3,1-3,п, диодный мост 4, (п+1) оптронн ых ключей 5.1-5. и+1. генератор 6 тактовых импульсов, управляемый делитель 7 частоты, первый счетчик 8 импульсов, второй счетчик 9 импульсов, оперативное запоминающее устройство 10, постоянное запоминающее устройство 11, сумматор 12, дешифратор 13.Преобразователь работает следующим образом.Цифровые коды, соответствующие необходимым, значениям мощности, выделяемой на резисторах 3 нагрузки, заносятся в последовательно расположенные ячейки оперативного запоминающего устройства 10. На выходе генератора б тактовых импульсов присутствует сигнал стабильной частоты. Напряжение источника 1 питания поступает на резисторы 3 нагрузки, аноды тиристоров 2, входные диагонали диодного моста 4, При прохождении переменного напряжения источника 1 питания через нулевое значение на выходе (и+1)-го оптронного ключа 5.пт 1 вырабатывается короткий импульс напряжения, который, приходя на первый вход второго счетчика 9, устанавливает его в нулевое состояние, далее этот импульс приходит на вход управляемого делителя частоты 7, при этом если число, поступающее из первого счетчика 8 на вход управляемого делителя 7 частоты не равно максимальному, которое определяется точностью, с которой работает устройство то в управляемом делителе 7 частоты производится коррекция коэффициента деления, далее импульс с оптронного ключа 5,п 1 переводит первый счетчик 8 в нулевое состояние. Коррекция коэффициента деления состоит в следующем. Если на момент прихода импульса с тп+1)-го оптронного клю та 5,п+1 на второй вход управляемого делителя 7 частоты число в первом счетчике 8, поступающее на третий вход управляемого делителя 7 частоты, оказывается больше максимального, то управляемый делитель 7 частоты увеличивает коэффициент деления, соответственно уменьшается частота на его выходе, соответственно к приходу следующего импульса с (п т 1)-го оптронного ключа 5,п+1 число в первом счетчике 8 будет меньшим, Аналогично, если к моменту прихода импульса с т,и+1)-го оптронного ключа 5 и т 1 число в первом счетчике будет меньше максимального, то коэффициент деления уменьшается, соответственно возрастает частота на выходе управляемого делителя 7 частоты, что приводит к моменту прихода следующего импульса, к увеличению числа в первом счетчике 8. Таким образом осуществляется жесткая привязка рзботы первогосчетчика 8 к периодам питающего напряжения. Наличие жесткой синхронизации гарантирует, что число импульсов, насчитанное первым счетчиком 8 за полупериод питающего напряжения, постоянно и в каждый момент времени соответствует времени, прошедшему от начала полупериода питающего напряжения. Используя это и зная форму питающего напряжения, можно вычислить поправку в значение цифрового кода, устраняющую влияние нелинейности питающего напряжения, Эта поправка будет всегда постоянна для конкретной формы питающего напряжения и конкретного значения цифрового кода. Устройства промышленной автоматики, для которых предназначено изобретение, питаются от сети переменного тока, изменяющегося по синусоидальному закону, Зная закон изменения питающего напряжения, можно просчитать поправки для каждого значения цифрового кода. Для этого составляется уравнение, связывающее исходное значение цифрово. го кода с скорректированным значением этого кода, Уравнение имеет следующий вид: иЛ 30 где п - исходный код;пт - скорректированный код;М - максимальное значение кода (определяется необходимой точностью преобразования),Приведенное уравнение не имеет аналитического решения и может быть решено численными методами на вычислительной машине, Результат расчета размещается в постоянном запоминающем устройстве таким образом, что при подаче на адресный вход постоянного запоминающего устрой ства исходного цифрового кода на его выходе считывается скорректированный цифровой код, который используется в дальнейшей работе устройства, После прохождения импульса с (и т 1)-го оптронного ключа 5 л 1 на второи счетчик 9 он начинает непрерывный счет импульсов генератора 6 тактовых импульсов что приводи к непрерывному увеличению числа на выходе второго счетчика 9 последующему его переполнению, сбросу и пов орению счета сначала Число с выхода второго счетчика 9 постуттает на первый вход дешифратора 13 и опера гивное запоминающее устройство 10. Иэ ячейки оперативного запоминающего устройства 10, номер которои соответствует числу во втором счетчике 9, данные 35 40 45 5055 5 10 15 20 25 и 1-- в 1 п ад а, М 2 о5 10 15 20 25 30 35 40 45 поступают на вход постоянного запоминающего устройства 11, при этом на его выходе получается скорректированный код, который поступает на первый вход сумматора 12. На второй вход сумматора 12 поступает число из первого счетчика 8, непрерывно нарастающее в течение всей полуволны питающего напряжения. При переполнении сумматора 12 на его выходе появляется сигнал, разрешающий работу дешифратора 13, при этом на выходе дешифратора 13 номер выхода соответствует числу во втором счетчике 9, появляется сигнал, который, пройдя через оптронный ключ 5, вскрываетсоответствующий тиристор 2. При этом, чем больше число в ячейке оперативного запоминающего устройства 10, тем большее число поступает на первый вход сумматора 12, тем при меньшем числе в первом счетчике 8 происходит переполнение сумматора 12, тем раньше после начала полупериода открывается тиристор 2, тем большая мощность выделяется на резисторе нагрузки 3, Аналогично, при меньшем числе в ячейке оперативного запоминающего устройства 10 происходит более позднее включение тиристора 2, что вызывает уменьшение мощности на резисторе 3 нагрузки. Так как второй счетчик 9 считаег с более высокой частотой, чем первый 8, то за время, пока перчый счетчик 8 увеличит свое значение, происходит вь:борка из всех ячеек оперативного запоминающего устройства 10, Таким образом, те тиристоры 2, которые должны включиться в данный моМент времени будут включены, Далее преобразователь продолжает работать в циклическом режим г.Формула изобретения Преобразователь цифрового кода в последовательность импульсов, содержащий п коммутирующих элементов, выполненных на тиристорах, катоды которых через соответствующие резисторы нагрузки объединены с первой шиной входной диагонали диодного моста и подключены к первому выходу источника питания, второй выход которого соединен с второй шиной входной диагонали диодного моста и анодами тиристоров, управляющие электроды которых соединены с выходами соответствующих с первого по и-й оптронных ключей, первый и второй входы и+1-го оптронного ключа соединены с выходной диагональю диодного моста, последовательно соединенные генератор тактовых импульсов, управляемый делитель частоты, первый счетчик импульсов, сумматор, вход установки в "О" счетчика импульсов объединен с первым управляющим входом управляемого делителя частоты и подключен к выходу и+1-го оптронного ключа, отл ича ю щи йс я тем,что, с целью повышения надежности при снижении габаритов преобразователя и его удешевлении, в него введены дешифратор. второй счетчик импульсов, оперативное запоминающее устройство и постоянное запоминающее устройство, выходы которого соединены с соответствующими вторыми информационными входами сумматора, выход переполнения которого соединен с входом разрешения дешифратора, входы которого объединены с соответствующими адресными входами оперативного запоминающего устройства и подключены к соответствующим выходам второго счетчика импульсов, а выходы дешифратора соединены с входами соответствующих с первого по и-й оптронных ключей, вход установки в "0" второго счетчика импульсов объединен с одноименным входом первого счетчика импульсов, а счетный вход соединен с выходом генератора тактовых импульсов, входы постоянного запоминающего устройства соединены с соответствующими выходами оперативного запоминающего устройства, информационные и управляющие входы которого являются соответственно шиной занесения и шиной управления, а выходы первого счетчика импульсов соединены с соответствующими вторыми управляющими входамиуправляемого делителя частоты.1672566 ректор Т.Малец аг дакт Заказ 2846 Тираж 443 ПодпВНИИПИ Государственного комитета по изобретениям и113035, Москва, Ж, Раушская наб КНТ С роизводственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина,Составитель И. РомановаТехред М.Моргентал исноеоткрытиям4/5

СмотретьЗаявка

4645190, 31.01.1989

ИНСТИТУТ ОПТИКИ АТМОСФЕРЫ СО АН СССР

ДЕСЯТОВ ВИТАЛИЙ АЛЕКСЕЕВИЧ, ГИНСАР ВИКТОР ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: H03M 1/66

Метки: импульсов, кода, последовательность, цифрового

Опубликовано: 23.08.1991

Код ссылки

<a href="https://patents.su/4-1672566-preobrazovatel-cifrovogo-koda-v-posledovatelnost-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь цифрового кода в последовательность импульсов</a>

Предыдущий патент: Интегрирующий преобразователь постоянного напряжения в код

Следующий патент: Преобразователь кода во временной интервал

Случайный патент: Роторно-дисковый экстрактор