Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

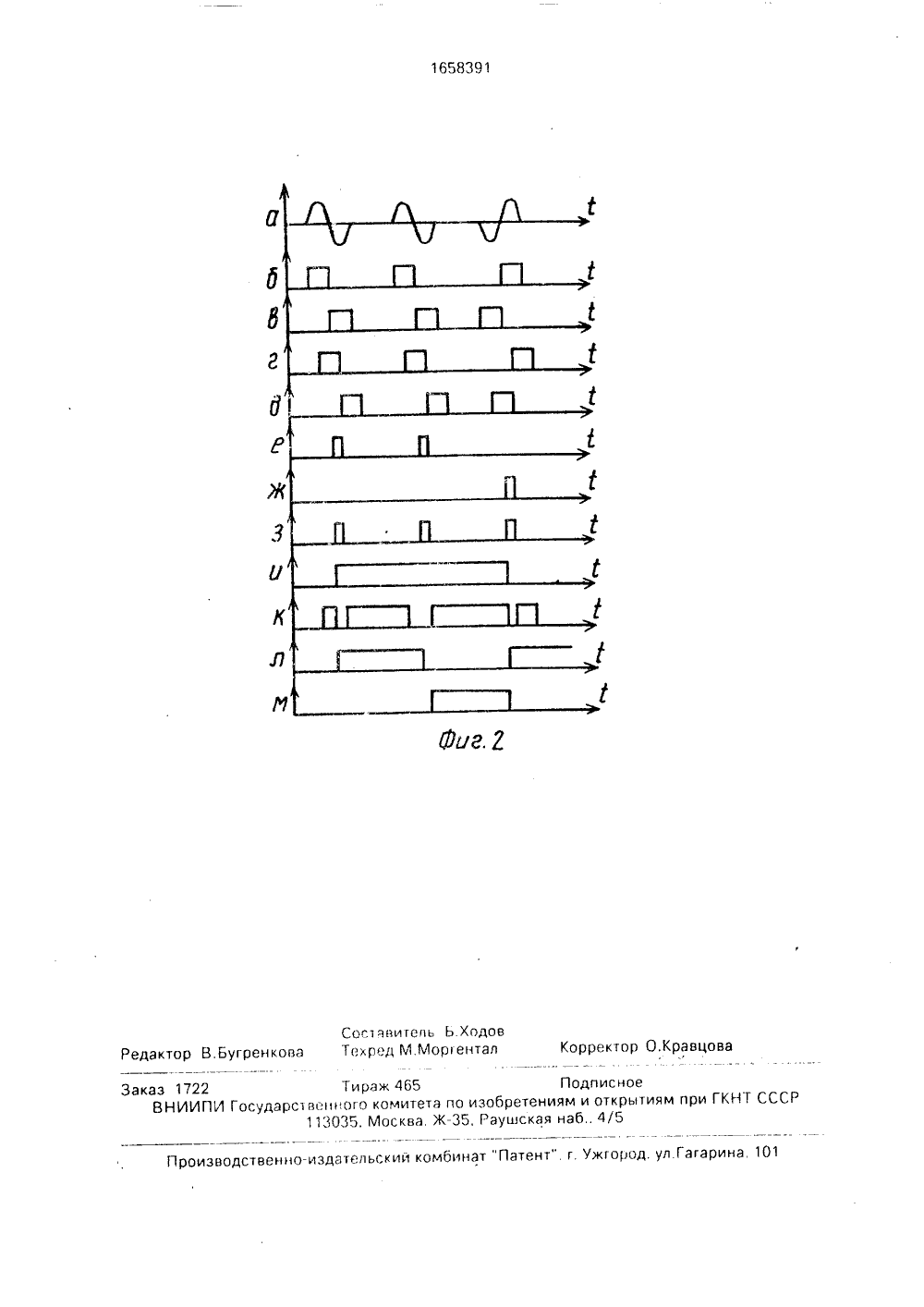

(51 САНИЕ ИЗОБРЕТЕН ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССМ 1305875, кл. Н 03 М 9/00, 198Авторское свидетельство СССМ 1283980, кл, Н 03 М 9/00, 1985.(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДО ТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных. Изобретение обеспечивает преобразования кода КИ (ГОСТ В 24152 - 83) в параллельный код, чем позволяет расширить область применения преобразователя. Преобразователь содержит элементы И 1 и 2, триггер 3, регистр 4 сдвига, формирователь 5 импульсов, блок 6 поэлементного сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент ИЛИ 8, элементы 9 и 10 задержки. 2 ил.Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных.Целью изобретения является расширение области применения преобразователя за счет обеспечения преобразования кода КИ.На фиг. 1 представлена функциональная схема преобразователя; на фиг. 2 - временные диаграммы, поясняющие его работу,Преобразователь содержит первый и второй элементы И 1 и 2. триггер 3, регистр 4 сдвига, формирователь 5 импульсов, блок 6 поэлементного сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент ИЛИ 8, первый и второй элементы 9 и 10 задержки, На фиг, 1 позициями 11-13 обозначены соответственно вход и первый и второй выходы преобразователя. На фиг, 2 соответствующими индексами обозначены следующие сигналы; а - сигнал на входе 11, б и в - сигналы на первом и втором выходе формирователя 5, г и д - сигналы на выходах элементов 9 и 10, е и ж - сигналы на выходах элементов 2 и 1, э - сигналы на выходе элемента 8, и - сигнал на выходе триггера 3, к - сигналы на выходе элемента 7, л - сигналы на выходе 12, м - сигналы на выходе 13,Код КИ представляет собой последовательность синусоидальных сигналов, В коде КИ логическая единица передается изменением фазы синусоидального сигнала на л по отношению к предыдущему синусоидальному сигналу, а логический нуль - повторением фазы предыдущего синусоидального сигнала.Регистр 4 сдвига может быть выполнен на 13-ти интегральных микросхемах 564 ПР 1. Информационный вход микросхемы является входом регистра 4 сдвига, информационный вход каждой следующей микросхемы соединен с выходом старшего разряда предыдущей микросхемы, тактовые входы всех микросхем обьединены и являются входом управления регистра 4 сдвига. Выходы разрядов "310","28 ,35", "4047", "5360", "6572", "7885", "9097" регистра 4 сдвига (в коде КИ в укаэанных разрядах передается полезная информация) являются первым выходом (групповым, состоящим из 56-ти линий) регистра 4 сдвига, а выходы разрядов "1,2,11"27", "3639", "48.61.64", "73,77", "8689", "98,100" регистра 4 сдвига - вторым выходом (групповым, состоящим иэ 44-х линий) регистра 4 сдвига.Блок 6 поэлементного сравнения представляет собой блок элементов И. прямые входы которого соединены с выходами30 35 40 45 50 55 5 10 15 20 25 разрядов "1", "11", "14", "26", "3639", "49,"51", "61", "62", "64". "74", "76", "86", "88", "89", "100" регистра 4 сдвига (в коде КИ в указанных разрядах передается логическая единица соответственно, а инверсные входы - с выходами разрядов "2", "12", "13", "15","25", "27", "48", "52". "73", "75", "77", "87", "98", "99" регистра 4 сдвига (в коде КИ в укаэанных разрядах передается логический нуль) и первым входом блока 6 соответственно. Высокий уровень сигнала на выходе блока 6 соответствует наличию высоких уровней сигналов на всех его прямых входах и низких уровней сигналов на всех его инверсных входах, Высокий уровень сигнала на первом (втором) выходе формирователя 5 формируется при наличии положительной (отрицательной) полуволны синусоидального сигнала на его входе, Импульсный сигнал, сформированный на первом выходе формирователя 5, поступает на вход элемента 9 задержки и второй вход элемента И 2. Импульсный сигнал, сформированный на втором выходе формирователя 5, поступает на вход элемента 10 задержки и второй вход первого элемента И 1. Время задержки сигналов, сформированных на выходах элементов 9 и 10 задержки (т), выбирают из условия то тТ т 1где т, - минимально допустимая длительность импульса на втором входе триггера 3;т - минимально допустимая длительность интервала между передними фронтами импульсов на втором и первом входе триггера 3;Т - длительность полуволны синусоидального сигнала в коде КИ.Импульсный сигнал, сформированный на выходе первого элемента 9 задержки, поступает на первый вход элемента 2 И, первый вход триггера 3 и первый вход элемента 7 ИСКЛЮЧАЮЩЕЕ ИЛИ.Импульсный сигнал, сформированный на выходе элемента 10 задержки, поступает на первый вход элемента И 1,Высокий уровень сигнала на выходе второго (первого) элемента 2 (1) формируется при наличии высоких уровней сигналов на его входах. Импульсы, сформированные на выходах элементов И 2 и 1, через элемент ИЛИ 8 поступают на второй вход триггера 3, управляющий вход регистра 4 сдвига и второй вход блока 6 анализа.По переднему фронту импульса, сформированного на выходе элемента ИЛИ 8. при наличии на входе триггера 3 высокого уровня сигнала на выходе триггера 3 уста 1658391навливается высокий (низкий) уровень сигнала. Импульсный сигнал, сформированный на выходе триггера 3, поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7.8 ысокий уровень сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 формируется при наличии высокого уровня сигнала на одном из его входов, Импульсный сигнал, сформированный на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7, поступает на вход регистра 4 сдвига,По переднему фронту импульса, сформированного на выходе элемента ИЛИ 8, при наличии высокого(низкого) уровня сигнала на входе регистра 4 сдвига в младший разряд регистра 4 сдвига записывается логическая единица (логический нуль), а ранее записанная в регистре 4 сдвига информация сдвигается на,один разряд в сторону старшего разряда,При установлении на втором выходе регистра 4 сдвига заданного кода в интервале между соседними импульсами на выходе элемента ИЛИ 8, на выходе блока 6 формируется высокий уровень сигнала, Импульс, сформированный на выходе блока 6, поступает на второй выход 13,Параллельный цифровой код, сформированный на первом выходе регистра 14 сдвига, поступает на первый выход 12,По переднему фронту импульса, сформированного на втором выходе 13, параллельный цифровой код, сформированный на первом выходе 12, и несущий полезную информацию, записывается в приемный (внешний) регистр системы обработки данных. Формула изобретенияПреобразователь последовательногокода в параллельный, содержащий элементы И, триггер, регистр сдвига первые выхо 5 ды которого являются первым выходомпреобразователя, о т л и ч а ю щ и й с я тем,что, с целью расширения области применения преобразователя за счет обеспеченияпреобразования кода КИ, в преобразова 10 тель введены блок поэлементного сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,элемент ИЛИ, элементы задержки и формирователь импульсов, первый выход которого соединен непосредственно с первым15 входом первого элемента И и через первыйэлемент задержки - с первыми входами второго элемента И, триггера и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которогосоединен с информационным входом20 регистра сдвига, вторые выходы которогосоединены с первыми входами блокапоэлементного сравнения, второй выходформирователя импульсов соединен непосредственно с вторым входом второго эле 25 мента И и через второй элемент эадержки -с вторым входом первого элемента И, выходы первого и второго элементов Исоединены с одноименными входами элемента ИЛИ, выход которого соединен с вто 30 рым входом триггера, с входом управлениярегистра сдвига и с вторым входом блокапоэлементного сравнения. выход которогоявляется вторым выходом преобразователя,выход триггера соединен с вторым входом35 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входформирователя импульсов является входомпреобразователя,1658391 г Ходовентал Сосавител Текред М М едактор В.Бугренкова каз 1722 ВНИИПИ о изобретени5, Раушская зводственно-издательскии комбинат "Патент" г. Ужгород, ул.Гагарина, 10 Тираж 465 арс венного комитета и 113035, Москва, Ж Корректор О.КравцоваПодписноем и открытиям при ГКНТ СССРаб 4/5

СмотретьЗаявка

4615951, 30.11.1988

ПРЕДПРИЯТИЕ ПЯ А-3706

ДОГАДКИН ИГОРЬ ВЛАДИМИРОВИЧ, СТАЛИН ЕВГЕНИЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.06.1991

Код ссылки

<a href="https://patents.su/4-1658391-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Устройство подавления радиоимпульсных помех

Случайный патент: Способ компенсации постоянных радиоэхо