Устройство для алгебраического суммирования сигналов в формате линейной дельта-модуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1587635

Автор: Бадалян

Текст

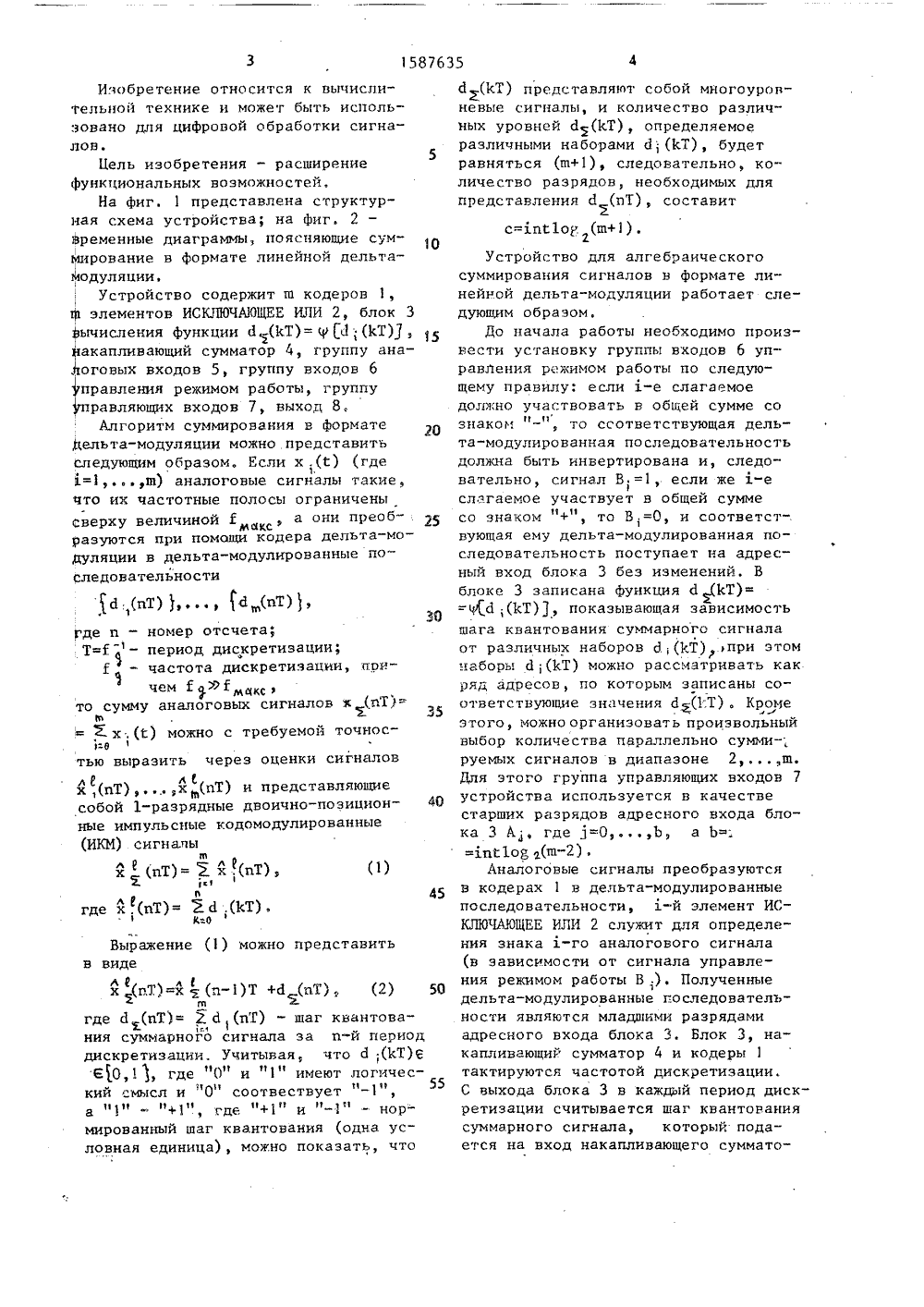

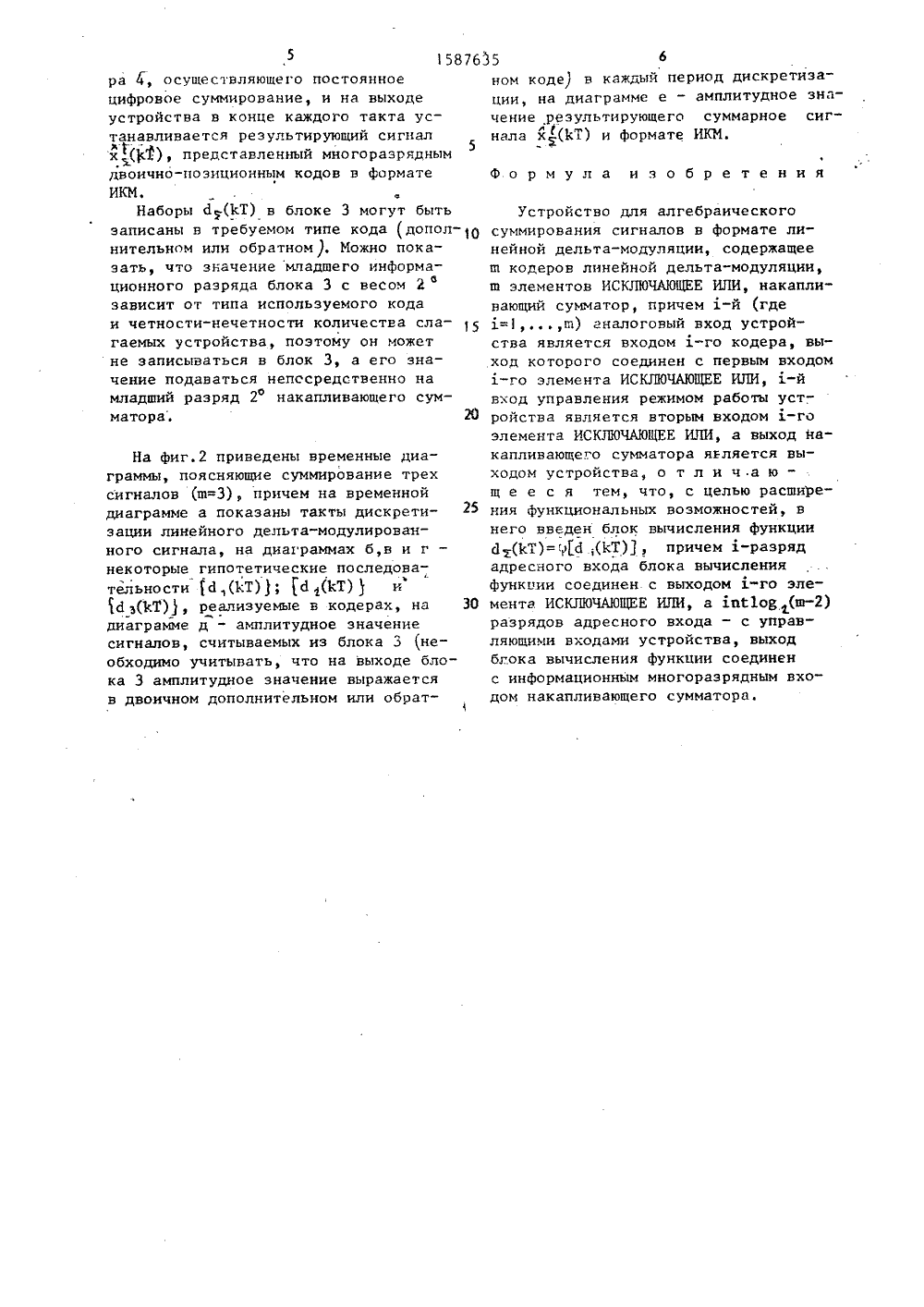

Изобретение относится к вычислительной технике и может быть использовано для цифровой обработки сигналов.Бель изобретения - расширениефункциональных возможностей,На фиг. 1 представлена структурная схема устройства; на фиг. 2 -временные диаграммы, поясняющие сумМирование в формате линейной дельтамодуляции,Устройство содержит ш кодеров 1,ш элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, блок 3вычисления функции й(1 сТ) = Ч Р 1(1 сТ)3накапливающий сумматор 4, группу аналоговых входов 5, группу входов буправления режимом работы, группууправляющих входов 7, выход 8,Алгоритм суммирования в формате,1 ельта-модуляции можно, представитьследующим образом, Если х .(с) (где1=1ш) аналоговые сигналы такие,что их частотные полосы ограниченыСверху величиной 1 , а они преоб- .макс фразуются при помощи кодера дельта-модуляции в дельта-модулированные последовательности1 й(пТ) )й (пТ) ),где п - номер отсчета;Т=К- период дискретизации;частота дискретизации, причем ЕГмаксто сумму аналоговых сигналов ж (пТ) = Е х . можно с требуемой точнос 1.-етью выразить через оценки сигналов х,(пТ)х,(пТ) и представляющие е есобой 1-разрядные двоично-позиционные импульсные кодомодулированные (ИКМ) сигналых Е (пТ) = Х х Е(пТ), (1)Е ;согде х,(пТ)=й .ОсТ),к:о ЗО 4 О Выражение (1) можно представить в видех (пТ)=х(и)Т +й (пТ),. (2) 50й Егде й (пТ)= 2. й (пТ) - шаг квантова.ния суммарного сигнала за и-й период дискретизации. Учитывая, что й;(1 сТ)Е ЯО,1 , где 0 и "1" имеют логический смысл иО соотвествует - 1л и юв 55л 1 ц ц+1 н и+1 ц ц 1 п1мированный шаг квантования (одна условная единица), можно показать, что йТ) представляют собой многоуровневые сигналы, и количество различных уровней й 5;Т), определяемое различными наборами й; Т), будет равняться (ш+1), следовательно, количество разрядов, необходимых для представления й (пТ), составитХс.=п 11 оЕ (ш+1).2Устройство для алгебраического суммирования сигналов в формате линейной дельта-модуляции работает следующим образом.До начала работы необходимо произвести установку группы входов б управпения режимом работы по следующему правилу: если д-е слагаемое должно участвовать в общей сумме со знаком "-", то соответствующая дельта-модулированная последовательность должна быть инвертирована и, следовательно, сигнал В;=1, если же 1-е слагаемое участвует в общей сумме со знаком "+ , то В,=О, и соответст-. вующая ему дельта-модулированная последовательность поступает на адресный вход блока 3 без изменений, В блоке 3 записана функция й (1 сТ)= =й;(1 сТ), показывающая зависимость шага квантования суммарного сигнала от различных наборов й;(1 сТ) при этом наборы й ЬТ) можно рассматривать как ряд адресов, по которым записаны соответствующие значения й(1.Т), Кроме этого, можно организовать произвольный выбор количества параллельно сумми-; руемых сигналов в диапазоне 2,ш. Для этого группа управляющих входов 7 устройства используется в качестве старших разрядов адресного входа блока 3 А, где з=ОЬ, а Ь =пс 1 о 8 (ш)Аналоговые сигналы преобразуются в кодерах 1 в дельта-модулированные последовательности, -й элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2 служит для определения знака х-го аналогового сигнала (в зависимости от сигнала управления режимом работы В .). Полученные дельта-модулированные госледовательности являются младшими разрядами адресного входа блока 3, Блок 3, накапливающий сумматор 4 и кодеры 1 тактируются частотой дискретизации. С выхода блока 3 в каждый период дискретизации считывается шаг квантования суммарного сигнала, который подается на вход накапливающего суммато1587635 бном коде в каждый период дискретизации, на диаграмме е - амплитудное значение результирующего суммарное сигнала х(1 сТ) и формате ИКМ. ра 4; осуществляющего постоянное цифровое суммирование, и на выходе устройства в конце каждого такта устанавливается результирующий сигнал х .фй), представленный многоразряднымддвоично-позиционным кодов в формате ИКМ,Наборы ЙТ) в блоке 3 могут быть записаны в требуемом типе кода (дополнительном или обратном ), Можно показать, что значение младшего информационного разряда блока 3 с весом 2 зависит от типа используемого кода и четности-нечетности количества слагаемых устройства, поэтому он может не записываться в блок 3, а его значение подаваться непссредственно на младший разряд 2 накапливающего сумматора. 20 На фиг.2 приведены временные диаграммы, поясняющие суммирование трех сигналов (ш=3), причем на временной диаграмме а показаны такты дискретизации линейного дельта-модулированного сигнала, на диаграммах б,в и г некоторые гипотетические последовательностиЙ, (Ъ:Т) ; Й Т)к Йэ(И, реализуемые в кодерах, на 30 диаграмме д - амплитудное значение сигналов, считываемых из блока 3 (необходимо учитывать, что на выходе блока 3 амплитудное значение выражается в двоичном дополнительном или обратФормула изобретения Устройство для алгебраического суммирования сигналов в формате линейной дельта-модуляции, содержащее ш кодеров линейной дельта-модуляции, ш элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, накапливающий сумматор, причем 1-й (где =. ш) аналоговый вход устройства является входом -го кодера, выход которого соединен с первым входом -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, 1-й вход управления режимом работы устройства является вторым входом -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход накапливающего сумматора является выходом устройства, о т л и ч а ю - щ е е с я тем, что, с целью расширения функциональных возможностей, в него введен блок вычисления функции Й-Т)=рЙ.;(1 Т), причем 1-разряд адресного входа блока вычисления функции соединен. с выходом 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а дпй 1 о (ш) разрядов адресного входа - с управляюп 1 ими входами устройства, выход блока вычисления функции соединен с информационным многоразрядным входом накапливающего сумматора.-1ЩВъз Тираж 656 енного комитета и 13035, Москва, Жизобретениям5, Раушская н открытиям при ГКНТ СССР д. 4/5 город, ул. Гагарина, 101

СмотретьЗаявка

4455792, 07.07.1988

ЕРЕВАНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. К. МАРКСА

БАДАЛЯН РАФАЕЛ РАФВАРОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: алгебраического, дельта-модуляции, линейной, сигналов, суммирования, формате

Опубликовано: 23.08.1990

Код ссылки

<a href="https://patents.su/4-1587635-ustrojjstvo-dlya-algebraicheskogo-summirovaniya-signalov-v-formate-linejjnojj-delta-modulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для алгебраического суммирования сигналов в формате линейной дельта-модуляции</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Формирователь многочастотных сигналов

Случайный патент: Щеточный скребок для очистки трубопроводов