Устройство детектирования амплитудно-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1525862

Авторы: Венскаускас, Николаев, Осокин, Шульц

Текст

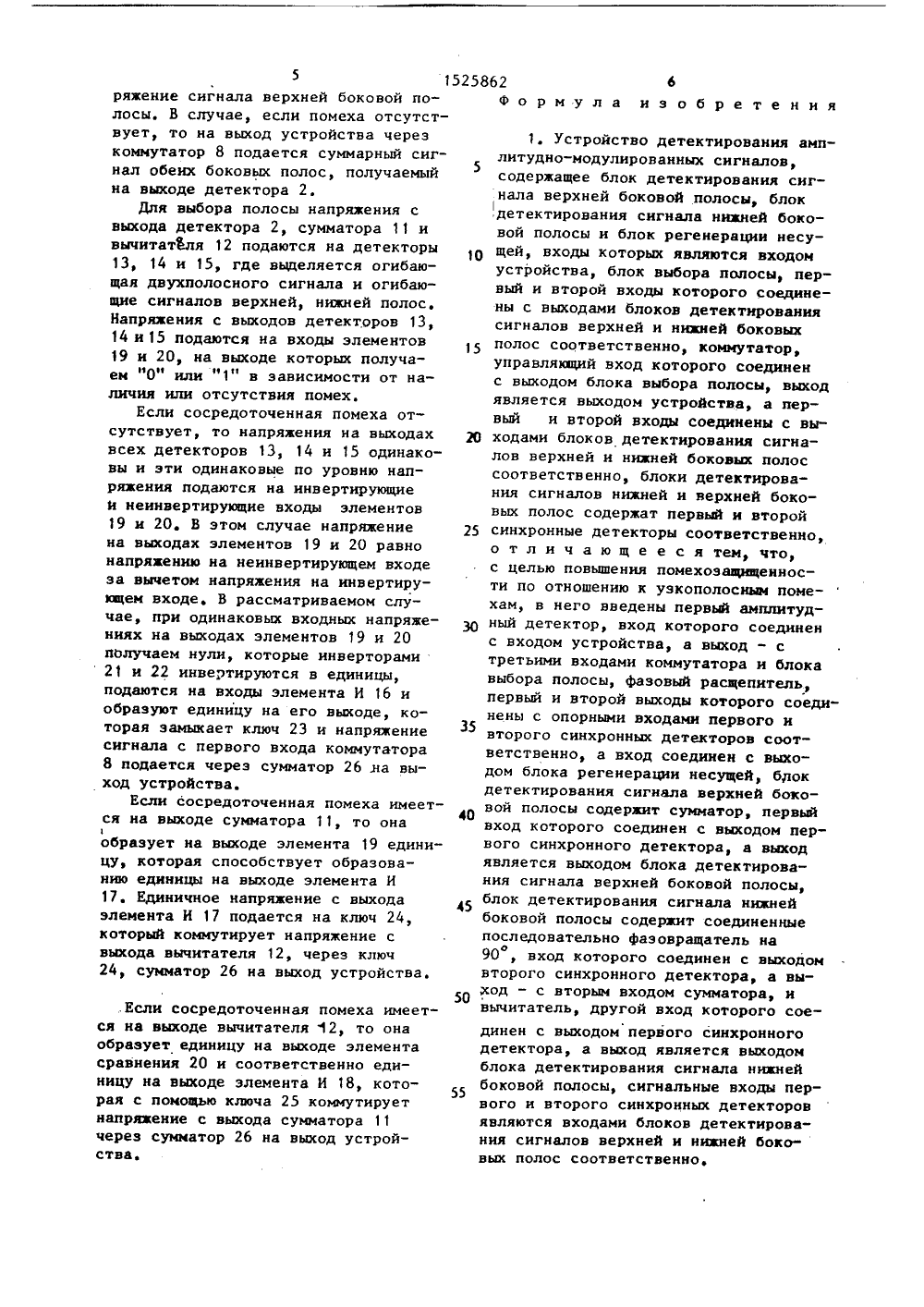

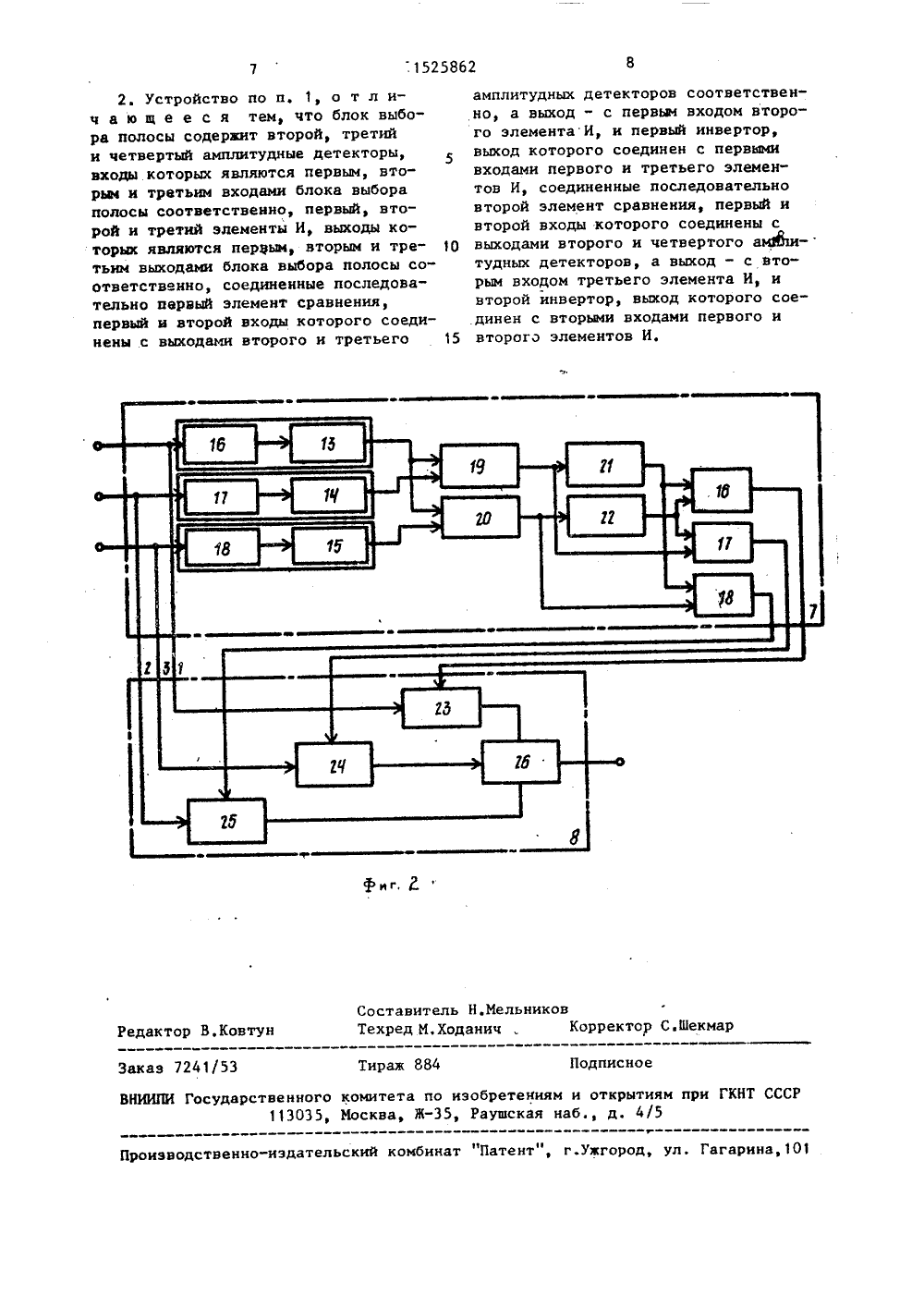

(54) УСТРОЙ АМПЛИТУДНО- (57) Изобретехнике. Це ние помехоз к узкополос содержит бл ла верхней о ОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГКНТ СССР ОПИСАНИЕ И АВТОРСКОМУ С 8 ИДЕ(56) Гцаепо 1., 1 попе М.Бе 1 есгче гесе 1 чег 1 ппяа ой где 6" МНК ТесЬпров 1 ап, То 1 суо, Арг 11, 196Заявка ВеликобританииВ 1593834, кл, Н 04 В 1/ ТВО ДЕТЕКТИРОВАНИЯ ОДУЛИРОВАННЫХ СИГНАЛОВ ение относится к радио - ь изобретения - повышеащищенности по отношению ым помехам. Устройство к детектирования 1 сигн оковой полосы, состоящии из синхронного детектора 3 и уммтора 11, амплитудный детектор 2,блок регенерации 5 несущей, блоктектирования 6 сигнала нижней бовой полосы, состоящий из синхрондетектора 4, фазовращателя 1 О наи вычитателя 12, блок выбора 7 псы, коммутатор 8 и фазовый расщетель 9, Если помехой поражена веняя (нижняя) боковая полоса принемого сигнала, то блоком выборана выход устройства через коммуттор 8 коммутируется напряжение снала нижней (верхней) боковой полсы. Если помеха отсутствует, товыход устройства через коммутатоподается суммарный сигнал обеихковых полос, получаемый на выходдетектора 2. Устройство по п. 2 фотличается выполнением блока выбра 7. 1 з,п. ф-лы, 2 ил,(8) Изобретение относится к радиотехнике и может быть использовано всоставе приеиников амплитудно-модулированных сигналов.5Цель изобретения - повьппение помехозащищенности по отношению кузкополосным помехаи.На фиг. 1 представлена структурная электрическая схема устройства 10детектирования амплитудно"модулированных сигналов; на фиг. 2 - структурные электрические схемы блока выбора полосы и коммутатора,Устройство детектирования амплитудно-модулированных сигналов содержит блок 1 детектирования сигналаверхней боковой полосы, первый аиплитудный детектор 2, первый синхрон.ный детектор 3, второй синхронныйдетектор 4, блок 5 регенерации несущей, блок 6 детектирования сигналов нижней боковой полосы, блок 7выбора полосы, коммутатор 8, фазоый расщепитель 9, фазовращатель на 25О" 10, сумматор 11, вычитатель 12.Влок 7 выбора полосы содержитвторой, третий и четвертый амплитудные детекторы 13, 14 и 15, первьй,второй и третий элемечты И 16, 17, 18,30первый и второй элементы 19 и 20сравнения, первый и второй инверторы 21 и 22.Коммутатор 8 содержит первый, второй и третий ключи 23, 24 и 25 и второй сумиатор 26,Устройство работает следующим образом,При отсутствии помех напряжениесигнала на входе устройства 1 которое 40иокно представить в виде шЦ, = Ц, совь 1 г + - Ц, сов(ъ++а )С+ Е 2 л ц соц(Ф + )С (1) поступает на детектор 2, первый и второй синхронные детекторы 3 и 4 и на блок 5. В выражении (1) приняты следукицие обозначения: Ц - амплитуда несущей частоты на выходе устройства; ш, - несущая частота (круговая); ш и ш - коэффициенты модуляции соответственно верхней и нижней боковых полос (обычно ш = ш);55 вЛ. и а Л. - полосы низкочастотных модулирующих частот, соответственно верхней и нижней боковых полос (обычно ала аЛ 1, )Блок 5 из суммарного принятого колебания (1) выделяет первое слагае-;. мое и на основе его регенерирует напряжение видац = ц соц(ш,+М)с, (2) где Ч - некоторый фазовый сдвиг. Это колебание поступает на вход фазового расщепителя 9 и на его синфазном и квадратурном выходах получим напряженияЪЦ = Цсоыш,с 1(3)Ц. - Ц,вепш,с 3которые поступают на.первый и второй синхронные детекторы 3 и 4.На выходе первого синхронного детектора 3 получим Ц = - ЦЦсоввлг+ - ЦЦ х Ш шм 2ф 4х совал.с . (4) На выходе второго синхронного детектора 4 имеемЦ =Ц Ц апьат. +-я ЦЦ хшв ш4 1 2 е 4х вдпдл.с. (5)Далеенапряжение (5) подается на фазовращатель 10 на 90 , выходное напряжение которого можно записать в виде Ц= -а Ц,Цсоьва с - -Ч),Ц х ша шк совал.с (6) Напряжения (4) и (6) подаются навходы вычитателя 12 и сумматора 11.Напряжение на выходе сумиатора 11можно записать в виде ц , ц + ц = - ц ц соаам с (7) ш н Ъ 1 ф 2 4 1а нв выходе вычитвтеля 12 ф Ц Ц - Ц-в Ц Цсоа аЯс ш и 3 1 ф,2 1Как видно из выражения (7) и (8), на выходе сумматора 11 блока 1 иы получаем только верхнюю боковую полосу принимаемого сигнала, а на выходе вычитателя 12 блока р только нижнюю боковую полосу принимаемого сигнала.Таким образом, если помехой поражена верхняя боковая полоса принимаемого сигнала, блоком 7 на выход устройства через коимутвтор 8 коммутируется напряжение сигнала нижней боковой полосы, Если поражена нижняя боковая полоса, то коммутируется нап5 1ряжение сигнала верхней боковой полосы. В случае, если помеха отсутствует, то на выход устройства черезкоммутатор 8 подается суммарный сигнал обеих боковых полос, получаемыйна выходе детектора 2.Для выбора полосы напряжения свыхода детектора 2, сумматора 11 ивычитателя 12 подаются на детекторы13, 14 и 15, где выделяется огибающая двухполосного сигнала и огибающие сигналов верхней, нижней полос.Напряжения с выходов детекторов 13,14 и 15 подаются на входы элементов19 и 20, на выходе которых получаем "0" или "1" в зависимости от наличия или отсутствия помех,Если сосредоточенная помеха отсутствует, то напряжения на выходахвсех детекторов 13, 14 и 15 одинаковы и эти одинаковые по уровню напряжения подаются на инвертирующиеи неинвертирующие входы элементов19 и 20, В этом случае напряжениена выходах элементов 19 и 20 равнонапряжению на неинвертирующем входеза вычетом напряжения на инвертирующем входе, В рассматриваемом случае, при одинаковых входных напряжениях на выходах элементов 19 и 20получаем нули, которые инверторами2 1 и 22 инвертируются в единицы,подаются на входы элемента И 16 иобразуют единицу на его выходе, которая замыкает ключ 23 и напряжениесигнала с первого входа коммутатора8 подается через сумматор 26 на выход устройства,Если сосредоточенная помеха имеется на выходе сумматора 11, то онаобразует на выходе элемента 19 единицу, которая способствует образованию единицы на выходе элемента И17. Единичное напряжение с выходаэлемента И 17 подается на ключ 24,который коммутирует напряжение свыхода вычитателя 12, через ключ24, сумматор 26 на выход устройства..Если сосредоточенная помеха имеется на выходе вычитателя 12, то она образует единицу на выходе элемента сравнения 20 и соответственно единицу на выходе элемента И 18, которая с помощью ключа 25 коммутирует напряжение с выхода сумматора 11 через сумматор 26 на выход устройства,525862 6 формула изобретения 1, Устройство детектирования амплитудно-модулированных сигналовсодержащее блок детектирования сигнала верхней боковой полосы блокУ,детектирования сигнала нижней боковой полосы и блок регенерации несущей, входы которых являются входомустройства, блок выбора полосы, первый и второй входы которого соединены с выходами блоков детектированиясигналов верхней и нижней боковыхполос соответственно, коммутатор,управлякзций вход которого соединенс выходом блока выбора полосы, выходявляется выходом устройства, а первый и второй входы соединены с вы ходами блоков детектирования сигналов верхней и нижней боковых полоссоответственно, блоки детектирования сигналов нижней и верхней боковых полос содержат первый и второй 25 синхронные детекторы соответственно,о т л и ч а ю щ е е с я тем, что,с целью повьппения помехоэащищенности по отношению к узкополосньпч помехам, в него введены первый амплитудный детектор, вход которого соединенс входом устройства, а выход - стретьими входами коммутатора и блокавыбора полосы, фазовый расщепитель,первый и второй выходы которого соединены с опорными входами первого ивторого синхронных детекторов соответственно, а вход соединен с выходом блока регенерации несущей, блокдетектирования сигнала верхней боковой полосы содержит сумматор, первыйвход которого соединен с выходом первого синхронного детектора, а выходявляется выходом блока детектирования сигнала верхней боковой полосы,блок детектирования сигнала нижнейбоковой полосы содержит соединенныепоследовательно фаэовращатель нао90 , вход которого соединен с выходомвторого синхронного детектора, а вы ход - с вторым входом сумматора, ивычитатель, другой вход которого соединен с выходом первого синхронногодетектора, а выход является выходомблока детектирования сигнала нижнейбоковой полосы, сигнальные входы первого и второго синхронных детекторовявляются входами блоков детектирования сигналов верхней и нижней боковых полос соответственно,.1525862 Фиг,Составитель Н,Мельниковедактор В.Ковтун Техред М,Ходанич . Корректор С.Шекма Заказ 7241/53 Тираж 884 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС113035, Москва, Ж, Раушская наб., д, 4/5 Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,2, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок выбора полосы содержит второй, третий и четвертый амплитудные детекторы, входы. которых являются первым, вторым и третьим входами блока выбора полосы соответственно, первьй, второй и третий элементы И, выходы которых являются первым, вторым и тре тьим выходами блока выбора полосы соответственно, соединенные последовательно первый элемент сравнения, первый и второй входы которого соединены с выходами второго и третьего 15 амплитудных детекторов соответственно, а выход - с первым входом второго элементаИ, и первый инвертор,выход которого соединен с первымивходами первого и третьего элементов И, соединенные последовательновторой элемент сравнения, первый ивторой входы которого соединены свыходами второго и четвертого ам 36 щ-тудных детекторов, а выход - с вторым входом третьего элемента И, ивторой инвертор, выход которого соединен с вторыми входами первого ивторого элементов И.

СмотретьЗаявка

4362097, 11.01.1988

ПРЕДПРИЯТИЕ ПЯ Г-4488

ВЕНСКАУСКАС КОСТАС КОСТОВИЧ, НИКОЛАЕВ ЕВГЕНИЙ МИХАЙЛОВИЧ, ОСОКИН ИГОРЬ АНАТОЛЬЕВИЧ, ШУЛЬЦ ТАТЬЯНА ИВАНОВНА

МПК / Метки

Метки: амплитудно-модулированных, детектирования, сигналов

Опубликовано: 30.11.1989

Код ссылки

<a href="https://patents.su/4-1525862-ustrojjstvo-detektirovaniya-amplitudno-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство детектирования амплитудно-модулированных сигналов</a>

Предыдущий патент: Цифровой синтезатор изменяющейся частоты

Следующий патент: Усилитель мощности

Случайный патент: Устройство для автоматической регистрации аварий в электрических системах