Программируемый генератор импульсных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

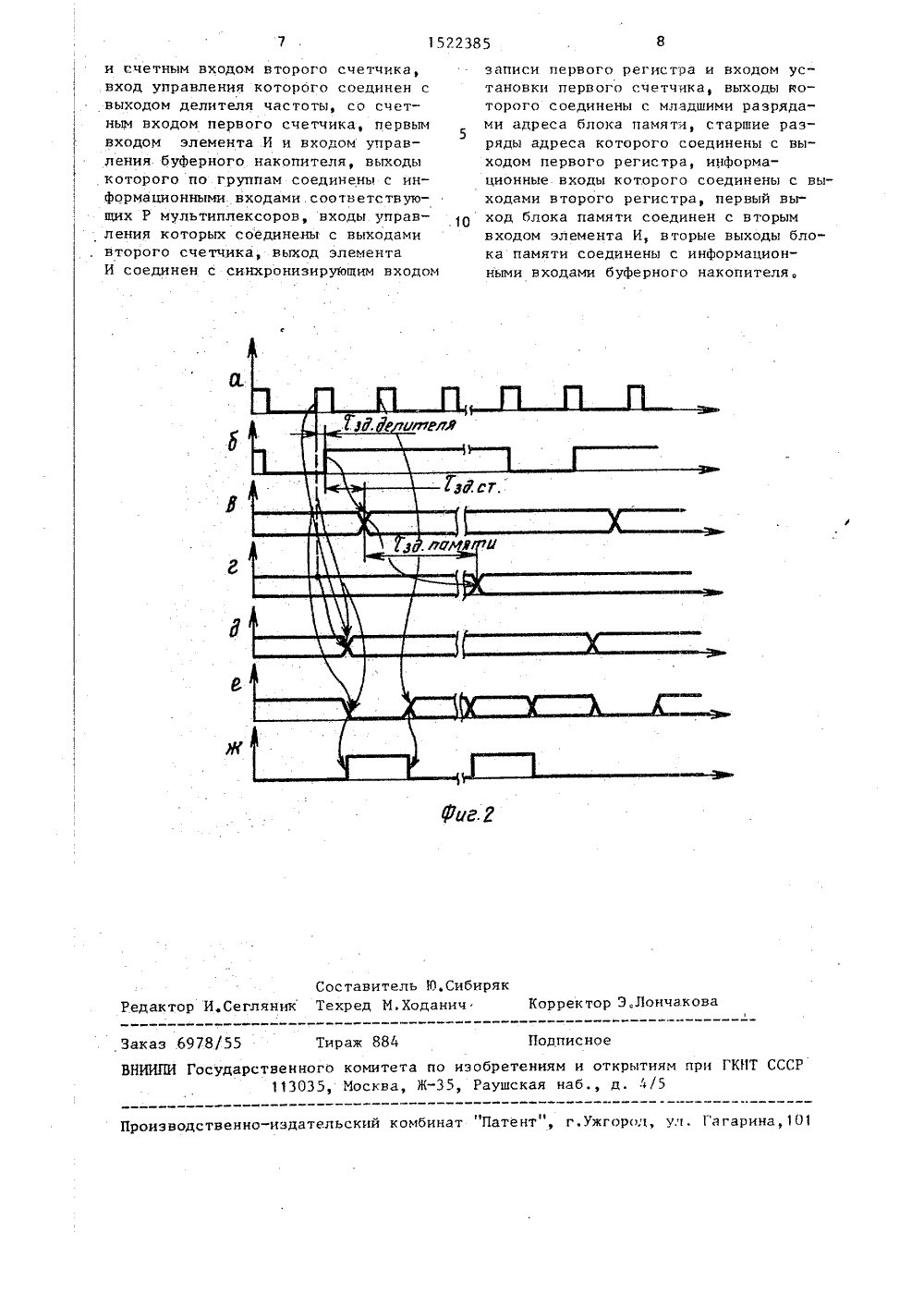

)4 НОЗК ЮИВ 311,;1 1 Ы 1.: ". ь, Б.;Е Г -1 ЕН ГОСУДАРСТВЕННЫИ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗО ВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1(56) Авторское свидетельство СССР Ф 1054894, кл. Н 03 К 3/64, 1981(54) ПРОГРАЮ 1 ИРУЕМЫЙ ГЕНЕРАТОР ИМПУЛЪСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение относится к импульсной технике и может быть использовано в вычислительной технике, системах управления и контроля, Цель изобретения - расширение диапазона регулирования параметров (периода, фазы, длительности импульса) формируемых 2импульсных последовательностей за счет уменьшения минимальных значений этих параметров - достигается введением мультиплексоров 8, время пере" ключения которых меньше, чем время выборки информации из блока 6 памяти, Формирование импульсных последовательностей осуществляется за счет преобразования параллельного кода, хранящегося в буферном накопителе 7 и переписанного из блока 6 памяти, в последовательный код с помощью мультиплексоров 8, адреса управления для которых формируются счетчиком 5, Период смены информации в блоке 6 памяти задается делителем 2 частоты, Генератор так же содержит задающий генератор 1, элемент И 3, счетчик 4, регистры 9, 10. 2 ил.25 55 Изобретение относится к импульсной технике и может быть использовано в различных областях вычислительной техники, системах управления иконтроля, где требуется генерирование5импульсных сигналов (кодовых посылокили периодических сигналов) с программируемой длительностью имп льсов, периодом и фазой.10Цель изобретения - расширение диапазона регулирования параметров г,периода, фазы, длительности импульса)Формируемой импульсной последовательности за счет уменьшения минимальныхзначений этих параметров.На фиг,1 представлена функциональная схема программируемого генератора импульсных последовательностейна Фиг,2 - временная диаграмма, поясняющая работу устройства,Праграммируемый генератор импульсных последовательностей содержит задающий генератор 1, делитель 2 частоты, элемент И 3, счетчики 4 и 5,блок 6 памяти, буферный накопитель7, мультиплексоры 8-1,..,8-Р, регистры 9 и 10,Выход задающего генератора 1 соединен с входом делителя 2 частоты,счетным входом счетчика 5 и с синхронизирующим входом буферного накопителя 7, Выход делителя 2 частоты. соединен с входом управления буферногонакопителя 7, счетным входом счетчика 4, входом управления .счетчика 5 ипервым входом элемента И 3, второй входкоторого соединен с первым выходом блока 6 памяти. Выход элемента И 3 сое, ,динен с синхронизирующим входом записирегистра 9 и входом обнуления счетчика4, выходы которого соединены с млад-.,шими разрядами адреса блока 6 памяти,старшие разряды адреса которого соединены с выходами регистра 9, информационные входы которого соединены свыходами регистра 10. Вторые выходыблока 6 памяти соединены с информационными входами буферного накопителя7, выходы которого соединены с информационными входами мультиплексоров8-18-Р. Входы управления мульти"плексоров 81,8.Р соединены с выходами счетчика 5Выходы мультиплексоров являются выхадами устройства.Делитель 2 частоты предназначендля формирования импульсов длительностью, равной периоду тактовой час"таты (Тгакг) задающего генератора 1,и частотой Г /ш, кратной тактовой частоте Г (ш - коэффициент деления),Счетчик 5 предназначен для управления мультиплексорами 8-18-Р,Счетчик 5 осуществляет последовательный счет импульсов задающего генератора 1, а по сигналу с выхода делителя 2 частоты устанавливается в исходкое нулевое состояние,Для того, чтобы на выходах мультиплексоров 8-1;.,8-Р не происходило "просечек" сигнала, необходимо,чтобы запись информации в буферныйнакопитель 7 происходила синхроннос установкой в нулевое состояние счетчика 5, причем задержка. появленияинформации на выходах буферного накопителя 7 и счетчика 5 должна бытьодинаковой,: Чтобы выполнить это треба.ванне целесообразно использовать дляобоих блоков одну элементную базу.Программируемый генератор импульсных последовательностей работает следующим образом,Перед началом работы производится программирование блока 6 памяти,регистра 10, устанавливаются. в нулевое состояние счетчик 4 и буферныйнакопитель 7, производится запись информации выбранной области блока 6 па.мяти в регистр 9 из регистра 1 О.Таким образом, в исходном состоянии на выходах счетчика 4 установленнулевой код, на выходах регистра 9находится код области памяти блока 6памяти, из которой будет производится считывание информации, На адресныхвходах блока 6 памяти установлен адрес нулевой ячейки выбранной областипамяти, в результате чего на выходахблока 6 памяти имеется код, хранящийся в этой ячейке памяти, На выходахбуферного накопителя 7 " логический"О". Счетчик.5 находится в произвольном состоянии, его выходной код, воздействуя на входы управления мультиплексоров 8-18-Р, вызывает коммутацию выходов буферного накопителя 7на выходы устройства, Но посколькубуферный .накопитель 7 обнулен, то навыходах устройства также сигнал логического нуля.После запуска задающего генератора1, вырабатывающего тактовые импульсы (фиг,2,а), счетчик 5 начинает счетимпульсов, В результате на его выходах, а следовательно, и на входах управления мультиплексоров 8-18-Р5 6выходах мультиплексоров 8-18-Р,т,е, шаг регулирования параметров выходного сигнала стал равным Т /шта Кт(Ттакт период частоты сигнала навыходе делителя 2 частоты) .С приходом очередного импульса свыхода делителя 2 частоты произойдетпереключение в следующее состояние,счетчика 4, а фронтом ближайшего импульса тактовой частоты - запись очередной информации в буферный накопитель 7 и установка в ноль счетчика 5.Далее процедура, описанная выше, повторится,Сигналом об окончании одного периода кодовых посылок служит появлениелогической "1" на первом выходе блока6 памяти, который открывает по первому входу элемента И 3 и первым жеимпульсом с выхода делителя 2 частотыпроисходит обнуление счетчика 4 и запись в регистр 9 информации из регистра 1 О. Этот же импульс разрешаетзапись в буферный накопитель 7 инфор"мации с последней ячейки выбраннойобласти памяти блока 6 памяти и об.нуление счетчика 5, т,е, осуществляется последний цикл вывода информации из выбранной области памяти,К моменту прихода следующего импульса с выхода делителя 2 частоты навыходах блока б,памяти устанавливается информация, соответствующая адресу новой области памяти, если информация в регистре 10 изменилась, и повторяется вывод информации иэ старойобласти памяти, если информация в регистре 10 не изменялась, Соответственно в первом случае на выходах.генератора начнется формирование новых кодовых посылок и повторится вывод старых - во втором,Формула изобретенияПрограммируемый генератор импульсных последовательностей, содержащий задающий генератор, элемент И, первый счетчик, блок памяти, буферный накопитель, о т л и ч а ю щ и й с я тем, что, с целью расширения диапазона регулирования параметров формируемой импульсной последовательнос-. ти, в него введены делитель частоты, Р мультиплексоров, второй счетчик, первый, второй регистры, причем выход задающего генератора соединен с входом делителя частоты, синхронизирующим входом буферного накопителя 5152238 последовательно меняется код, Это приводит к тому, что на выходы мультиплексоров 8-18-Р последовательно поступает инфоомация с входов этих мультиплексоров, Однако, на выходах5 мультиплексоров 8-18-Р по-прежнему сохраняется сигнал логического "О", поскольку буферный накопитель 7, соединенный своими выходами с информационными входами мультиплексоров 8-18-Р, обнулен. Это будет продолжаться до тех пор, пока на выходе делителя 2 частоты не появится импульс, равный периоду частоты задающе"15 го генератора 1 и задержанный относительно фронта тактового импульса на время задержки делителя 2 частоты (ЗА, Девитец) (Фиг2 в 6) . Этот импульс пеРеключит с задеРжкойзд . ,счетчик 20 4 в следующее состояние (фиг,2,в) (тем самым подготовит адрес следующей ячейки памяти из которой будет считываться информация, через время сэта информация появится 25 на выходах блока 6 памяти (Фиг,2,г и, воздействуя на входы управления буФерного накопителя 7 .н счетчика 5, разрешит фронтом ближайшего тактового импульса одновременно записать в буферный накопитель 7 информацию, на-. ходящуюся на его информационных входах (фиг,2, е) В результате одновременно с выходов буферного накопителя 7 иа информационные входы мультиплексоров 8-1. ,8-Р поступит код, хранящийся в нулевой ячейке выбранной области, памяти, а на входы управления мультиплексоров 8-1 .,8-Р - код нулевого состояния счетчика 5. После 40 этого счетчик 5 начнет счет импульсов тактовой частоты.Поскольку делитель 2 частоты осуществляет деление частоты. задающего генератора 1 на ш, то за период 45 между двумя импульсами на выходе делителя 2 частотына счетный вход счетчика 5 поступает ш импульсов тактовой частоты, В результате за этот период счетчик 5 будет принимать последовательно состояние с 0 до ш, что, в свою очередь, приведет .к тому, что на выходы мультиплексоров 8 т 18-Р будут последовательно коммутироваться сигналы с 1-го по ш-й его информа"55 ционных входов (фиг,2, диагр.ж), Значит за один период смены информации на выходах буферного накопителя 7 происходит ш раз смена информации на1522385 2 Составитель Н).Сибирякктор И.Сегляник Техред М.ХоданичКорректор Э,Лончако Заказ .6978/55 ПодписноеВНИИПИ Государствен и м при ГКНТ С Тираж 884 ного комитета по 035, Москва, Жзобретениям и открытия Раушская каб., д. 4/5 изводственно-издательский комбинат "Патент", г,ужгород, ул, Гагарина,10 и счетным входом второго счетчика, вход управления которого соединен с выходом делителя частоты, со счетным входом первого счетчика, первым входом элемента И и входом управ 5 ления буферного накопителя, выходы которого по группам соединены с информационными входами. соответствуюших Р мультиплексоров, входы управления которых соединены с выходами второго счетчика, выход элемента И соединен с синхронизирующим входом записи первого регистра и входом установки первого счетчика, выходы которого соединены с младшими разрядами адреса блока памяти, старшие разряды адреса которого соединены с выходом первого регистра, информационные входы которого соединены с выходами второго регистра, первый выход блока памяти соединен с вторымвходом элемента И, вторые выходы блока памяти соединены с информационными входами буферного накопителя,

СмотретьЗаявка

4261232, 12.06.1987

МОСКОВСКИЙ ИНСТИТУТ ЭЛЕКТРОННОЙ ТЕХНИКИ

НИКИТИН ВЛАДИМИР ИЛЬИЧ, ДОКУЧАЕВ НИКОЛАЙ ИВАНОВИЧ, ЧАЩЕГОРОВ МИХАИЛ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03K 3/64

Метки: генератор, импульсных, последовательностей, программируемый

Опубликовано: 15.11.1989

Код ссылки

<a href="https://patents.su/4-1522385-programmiruemyjj-generator-impulsnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый генератор импульсных последовательностей</a>

Предыдущий патент: Система заряда накопительного конденсатора

Следующий патент: Генератор магнитной развертки

Случайный патент: Устройство для механической обработки кромок труб