Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

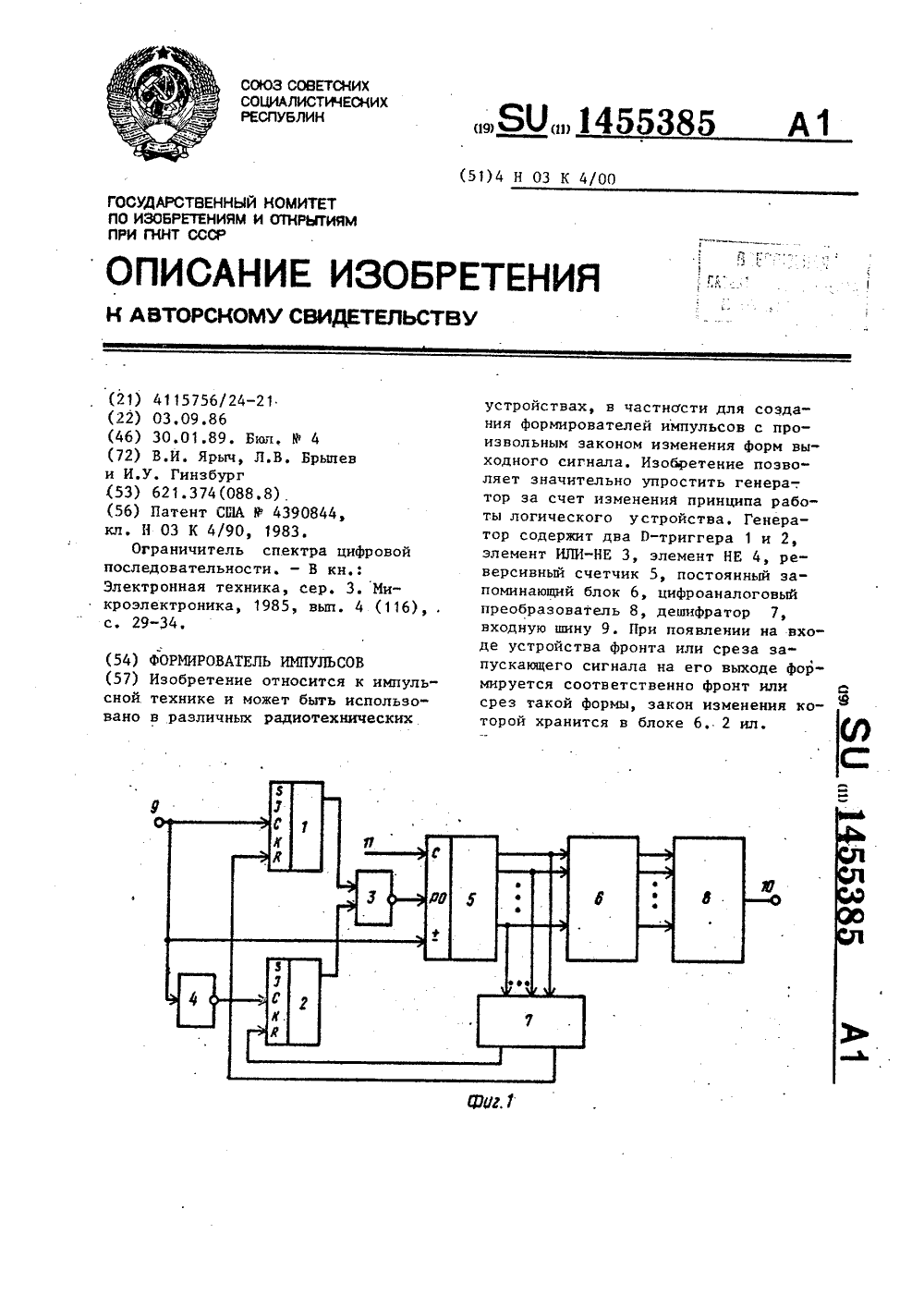

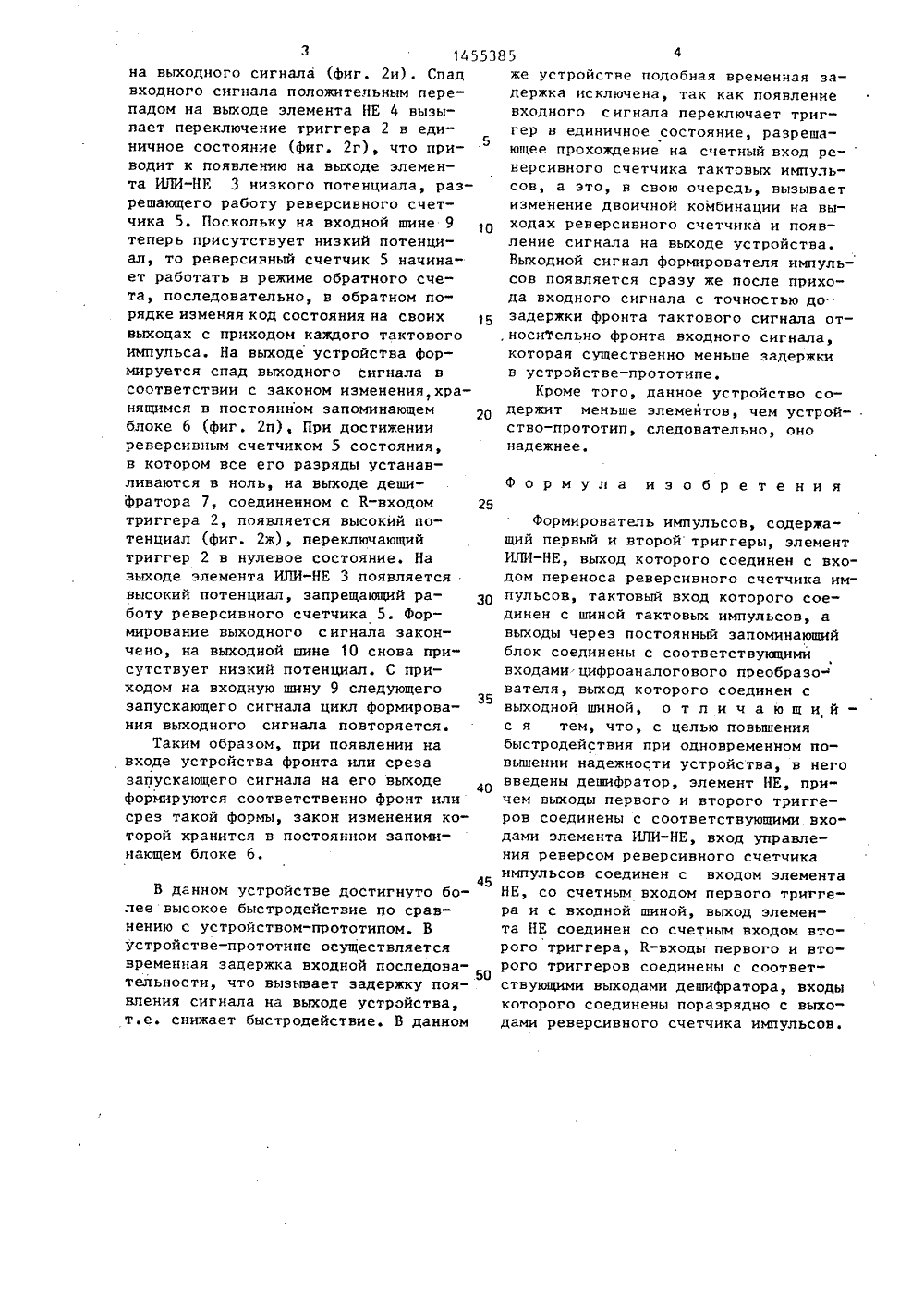

(19) (И) 8 51) 4 Н 03 К 4/00 КОМИТЕТ ОТКРЫТИ ГОСУДАРСТ 8 ЕНН ПО ИЗОБРЕТЕНИ ПРИ ГКНТ СССР ПИСА РЕТЕНИТВУ ЕЛЬС АВТОРСКОМУ С 8 И(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ (57) Изобретение относится к импул ской. технике и может быть использо вано в различных радиотехнических устроиствах, в частности для создания формирователей импульсов с произвольным законом изменения форм выходного сигнала. Изобретение позволяет значительно упростить генера-.тор эа счет изменений принципа работы логического устройства. Генератор содержит два 0-триггера 1 и 2,элемент ИЛИ-НЕ 3, элемент НЕ 4, реверсивный счетчик 5, постоянный запоминающий блок 6, цифроаналоговыйпреобразователь 8, дешифратор 7,входную шину 9. При появлении на входе устройства фронта или среза запускающего сигнала на его выходе формируется соответственно фронт илисрез такой формы, закон изменения которой хранится в блоке 6. 2 ил.Изобретение относится к импульсной технике и может быть использовано в различных радиотехнических устройствах для формирования импульсов с произвольным законом изменения фронтов.Цель изобретения - повышение бы, стродействия устройства при одновременном повышении надежности за счет уменьшения числа элементов.На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу уст- ройства, 15Устройство содержит первый и второй триггеры 1, 2, элемент ИЛИ-НЕ 3, элемент НЕ 4, реверсивный счетчик 5 импульсов, постоянный запоминающийблок 6, дешифратор 7, цифроаналоговый 20 преобразователь 8, входную шину 9, выходную шину 10, шину 11 тактовых импульсов.Входная шина 9 соединена со счетным входом первого триггера 1, через 25 элемент НЕ 4 - со счетным входом второго триггера 2 и с входом управления реверсом реверсивного счетчика5, выходы которого поразрядно соединены с входами дешифратора 7 и постоянно запоминающего блока 6, выходы которого соединены поразрядно с входами цифроаналогового преобразователя 8, выход которого соединен с выходной шиной 10. Первый и второй выходы дешифратора 7 соединены с К-входами первого и второго триггеров 1, 2, выходы которых соединены с входамиэлемента ИЛИ-НЕ 3, выход которого сое", динен с входом переноса реверсивного 1 О счетчика 5, тактовый вход которогосоединен с шиной 11.В исходном состоянии триггеры 1 и 2 находятся в нулевом состоянии,на входе запрета реверсивного счетчика 5 присутствует высокий потенциалзапрещающий его работу, на всех выходах реверсивного счетчика 5 - низкий потенциал, на входе цифроаналогового преобразователя 8 - нулевая комбинация, соответствующая комбинации на выходе постоянного запоминающего блока 6 при считывании информации из нулевого адреса. Дешифратор 7 имеет два выхода, на первом из ко" торых выходной сигнал появляется при переходе всех разрядов реверсивного счетчика 5 в нулевое состояние, В исходном состоянии на первом выходе . дешифратора 7 присутствует высокийпотенциал, запрещающий работу триггера 2На втором выходе дешифратора7 выходной сигнал появляется при переходе всех разрядов реверсивногосчетчика 5 в единичное состояние, Висходном состоянии на втором выходедешифратора 7 присутствует низкийпотенциал разрешающий работу триггера 1, На тактовый вход реверсивного .счетчика 5 поступают тактовыеимпульсы с шины 11. В постоянном запоминающем блоке 6 хранится закон изменения выходного сигнала,Устройство работает следующим образомВ зависимости от требуемого режима работы к нему на вход поступаетлибо одиночный импульс прямоугольнойформы, либо пачка таких импульсов,либо периодическая последовательностьтаких импульсоЮ (фиг. 2 б). Фронтвыходного импульса вызывает переключение триггера 1 в единичное состояние (фиг, 2 в). На выходе элементаИЛИ-НЕ 3 появляется низкий потенциал, разрешающий работу реверсивногосчетчика 5 в режиме счета. Поскольку на входной шине 9 присутствуетвысокий потенциал, то реверсивныйсчетчик 5 начинает работать в режиме прямого счета, изменяя кодсостояния на своих выходах с при.ходом каждого тактового импульса(фиг. 2 а, д). При этом на выходепостоянного запоминающего блока 6последовательно во времени появляются коды, соответствующие записаннымв ячейки памяти дискретным значениямкода выходного сигнала, который,в свою очередь, преобразуется цифроаналоговым преобразователем 8 в выходной сигнал аналоговой формы с за -данным законом изменения(фиг, 2 п).На обоих выходах дешифратора 7 - низ"кий потенциал, разрешающий работуобоих триггеров 1 и 2. При достиженииреверсивным счетчиком 5 состояния, вкотором все его разряды устанавлива-ются в единицу, на выходе дешифратора 7, соединенном с К-входом триггера 5, появляется высокий потенциал(фиг. 2 е), переключающий триггер 1в нулевое состояние (фиг. 2 е) . Навыходе элемента ИЛИ-НЕ 3 появляетсявысокий потенциал, запрещающий рабо"ту реверсивного счетчика 5. В этотмомент начинает формироваться верши.5 10 20 25 30 35 40 45 50 з 145 на выходного сигнала (фиг, 2 и). Спад входного сигнала положительным перепадом на выходе элемента НЕ 4 вызывает переключение триггера 2 в единичное состояние (фиг. 2 г), что приводит к появлению на выходе элемента ИЛИ-НЕ 3 низкого потенциала, разрешающего работу реверсивного счетчика 5, Поскольку на входной шине 9 теперь присутствует низкий потенциал, то реверсивный счетчик 5 начина" ет работать в режиме обратного счета, последовательно, в обратном порядке изменяя код состояния на своих вьмодах с приходом каждого тактового импульса. На выходе устройства формируется спад выходного сигнала в соответствии с законом изменения,хранящимся в постоянном запоминающем блоке 6 (фиг. 2 п), При достижении реверсивным счетчиком 5 состояния, в котором все его разряды устанавливаются в ноль, на выходе дешифратора 7, соединенном с К-входом триггера 2, появляется высокий потенциал (фиг. 2 ж), переключающий триггер 2 в нулевое состояние, На выходе элемента ИЛИ-НЕ 3 появляется высокий потенциал, запрещающий работу реверсивного счетчика 5. Формирование выходного сигнала закончено, на выходной шине 10 снова присутствует низкий потенциал, С приходом на входную шину 9 следующего запускающего сигнала цикл формирования выходного сигнала повторяется.Таким образом, при появлении на входе устройства фронта или среза запускающего сигнала на его выходе формируются соответственно фронт или срез такой формы, закон изменения которой хранится в постоянном запоминающем блоке 6. В данном устройстве достигнуто более высокое быстродействие по сравнению с устройством-прототипом. В устройстве-прототипе осуществляется временная задержка входной последовательности, что вызывает задержку появления сигнала на выходе устройства, т.е. снижает быстродействие. В данном 53854 же устройстве подобная временная задержка исключена, так как появление входного сигнала переключает триггер в единичное состояние, разрешающее прохождение на счетный вход реверсивного счетчика тактовых импульсов, а это, в свою очередь, вызывает изменение двоичной комбинации на выходах реверсивного счетчика и появление сигнала на вьмоде устройства. Выходной сигнал формирователя импульсов появляется сразу же после прихода входного сигнала с точностью до задержки фронта тактового сигнала от, носительно фронта входного сигнала,которая существенно меньше задержки в устройстве-прототипе. Кроме того, данное устройство содержит меньше элементов, чем устройство-прототип, следовательно, ононадежнееФормула изобретения Формирователь импульсов, содержащий первый и второи триггеры, элемент ИЛИ-НЕ, выход которого соединен с входом переноса реверсивного счетчика импульсов, тактовый вход которого соединен с шиной тактовых импульсов, а выходы через постоянный запоминающий блок соединены с соответствующими входами: цифроаналогового преобразо" вателя, вьмод которого соединен с выходной шиной, о т л и ч а ю щ и й - с я тем, что, с целью повышения быстродействия при одновременном повышении надежности устройства, в него введены дешифратор, элемент НЕ, причем выходы первого и второго триггеров соединены с соответствующими входами элемента ИЛИ-НЕ, вход управления реверсом реверсивного счетчика импульсов соединен с входом элемента НЕ, со счетным входом первого триггера и с входной шиной, выход элемента НЕ соединен со счетным входом второго триггера, К-входы первого и второго триггеров соединены с соответствующими выходами дешифратора, входы которого соединены поразрядно с выходами реверсивного счетчика импульсов.1455385 ректор Л, Пилипенн каз 7459/57 Тираж . 879ИКПИ Государственного комитета по изобретениям 113035, Москва, Ж, Раушская на ь ная, 4 роизводственно-полиграфическое предприятие, г. Ужгород П СоставителРедактор М. Циткина Техред М. А. Смирнданич Подписноеткрытиям при ГКНТ СССР д. 4/5

СмотретьЗаявка

4115756, 03.09.1986

ПРЕДПРИЯТИЕ ПЯ Г-4149

ЯРЫЧ ВИКТОР ИВАНОВИЧ, БРЫЛЕВ ЛЕОНИД ВАСИЛЬЕВИЧ, ГИНЗБУРГ ИОСИФ УШЕРОВИЧ

МПК / Метки

МПК: H03K 4/00

Метки: импульсов, формирователь

Опубликовано: 30.01.1989

Код ссылки

<a href="https://patents.su/4-1455385-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Способ формирования высоковольтных импульсов

Следующий патент: Способ фиксации момента прохождения входным сигналом нулевого уровня и устройство для его осуществления

Случайный патент: Разгонный вал