Преобразователь временных интервалов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1282073

Авторы: Витковский, Полуянов, Почтер

Текст

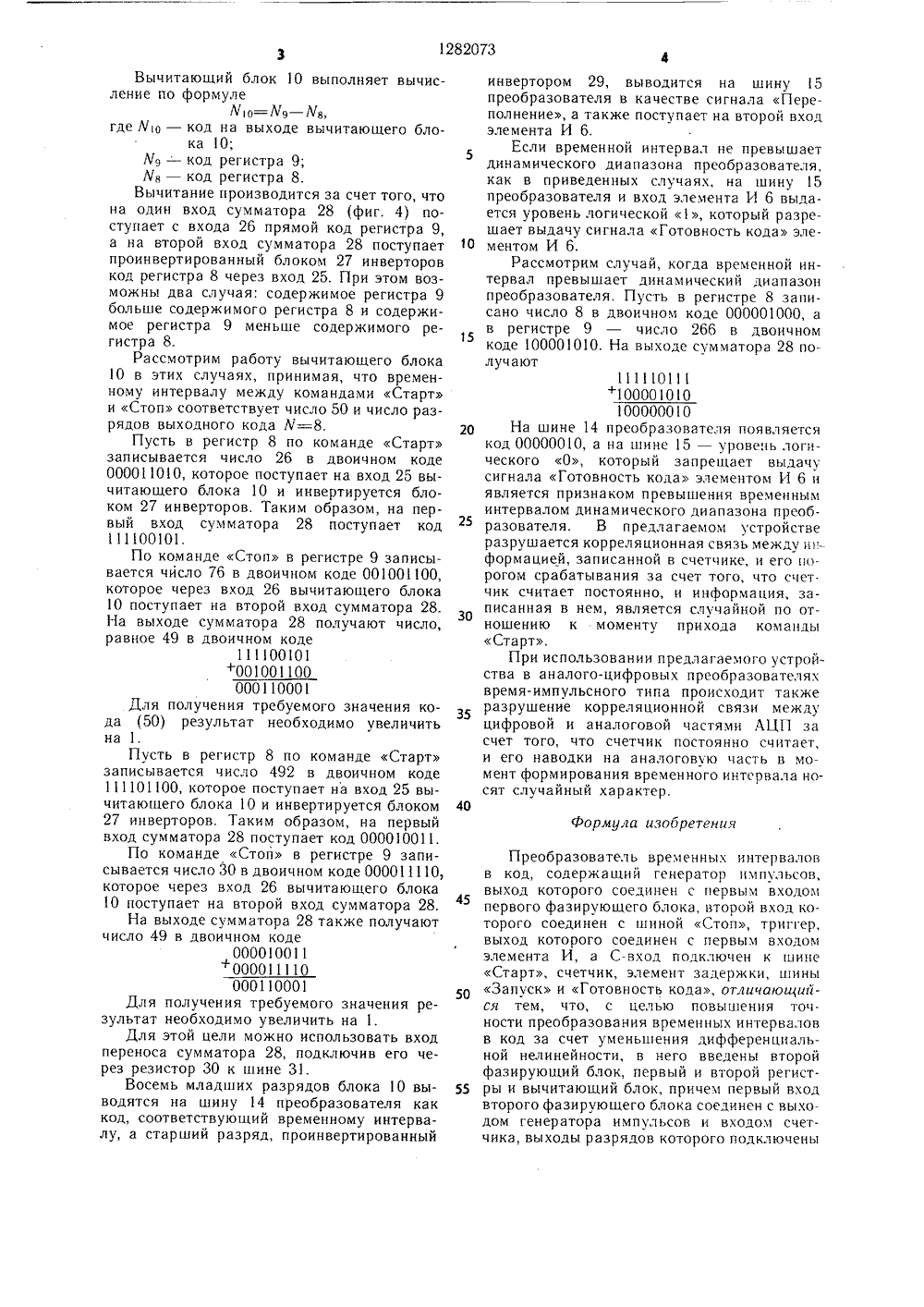

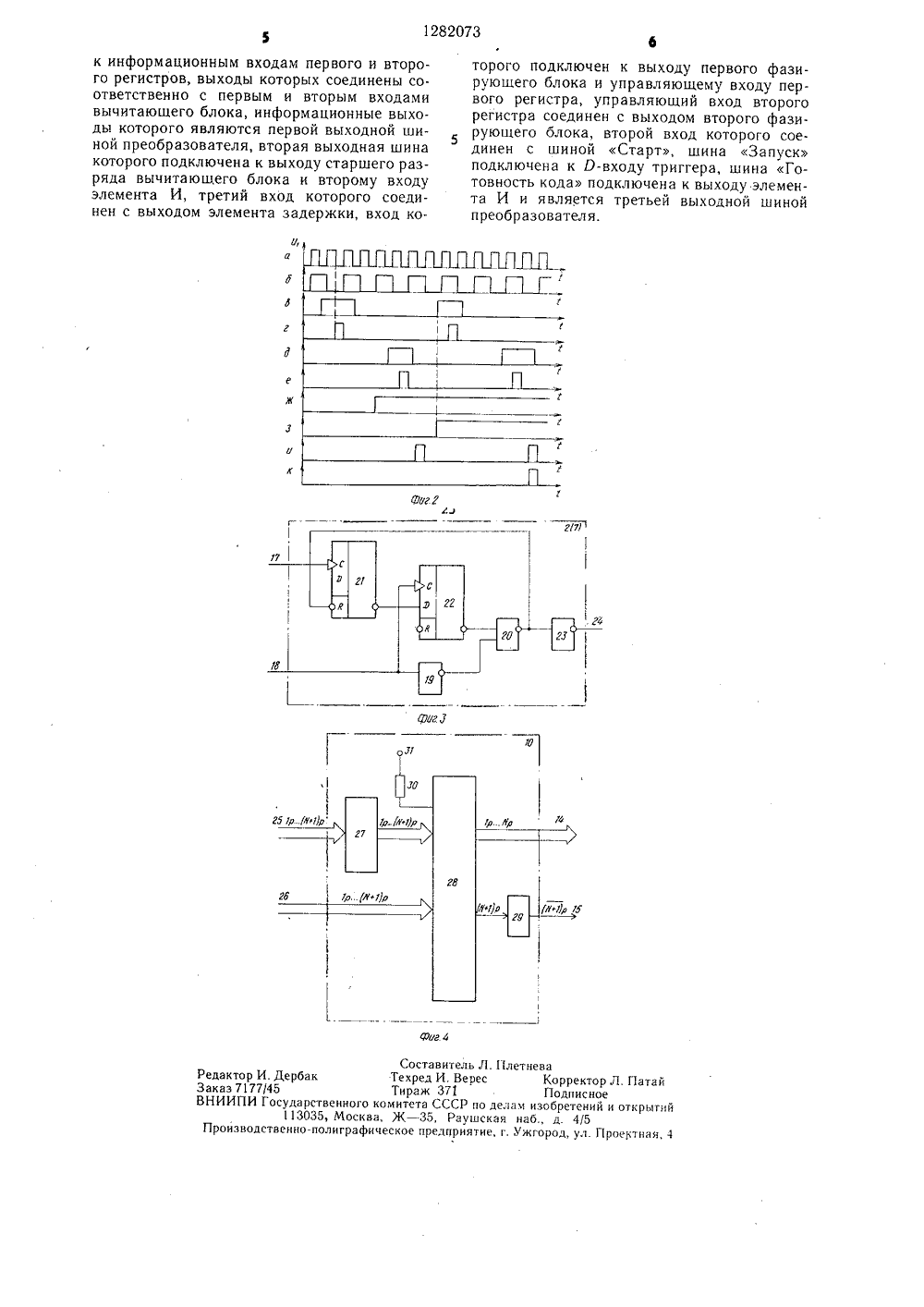

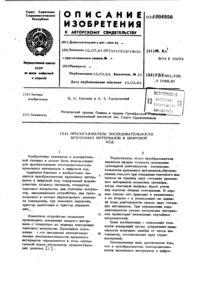

(54) ПРЕОБРАЗ ИНТЕРВАЛОВ В (57) Изобретение ной технике, Мож временных анализ нии длительности и а также в аналого ОВАТЕЛЬ КОД относится ет быть ис аторах при мпульсов в цифровых пВРЕМЕННЫХ к измерительользовано во преобразоваифровой код, еобразовате 00 РыгЕННЫЙ НОМИТЕТ СССРЗОБРЕТЕНИЙ И ОТНРЫТИЙ Н А ВТОРСКОМУ СВИДЕТЕЛЬСТ(71) Производственное объединениеКраснодарский ЗИП(56) Авторское свидетельство СССР949624, кл. б 04 Г 10/04, 1979.Мелешко Е, А. Интегральные схемы внаносекундной ядерной электронике. - М.Атомиздат, 1979, с. 137.,ЯО 1282073 лях время-импульсного типа, применяемых в амплитудных анализаторах. Цель изобретения - повышение точности преобразования временных интервалов в код за счет уменьшения дифференциальной нелинейности. Для достижения поставленной цели в устройство, содержащее генератор 1 импульсов, фазируюший блок 2, счетчик 3, триггер 4, элементов 5 задержки, элемент И 6, шину 11 Старт, шину 12 Стоп, шину 13 Запуск, выходную шину 15, шину 16 Готовность кода, введены фазируюший блок 7, регистры 8 и 9 и вычитаюший блок 1 О. При использовании предлагаемого устройства в аналого-цифровых преобразователях происходит разрушение корреляционной связи между цифровой и аналоговой частями АЦП за счет того, что счетчик постоянно считает, и его наводки на аналоговую часть в момент формирования временного интервала носят случайный характер. 4 ил.Изобретение относится к измерительнойтехнике и может быть использовано во временных анализаторах при преобразованиидлительности импульсов в цифровой код, атакже в аналого-цифровых преобразовате 5лях время-импульсного типа, применяемых вамплитудных анализаторах,Цель изобретения - повышение точности преобразования временных интервалов вкод за счет уменьшения дифференциальной нелинейности. 10На фиг. 1 изображена функциональнаясхема преобразователя; на фиг, 2 - временная диаграмма работы преобразователя;на фиг. 3 - функциональная схема фазирующих блоков; на фиг. 4 - функциональная схема вычитаюшего блока.15Преобразователь содержит генератор 1импульсов, фазируюший блок 2, счетчик 3,триггер 4, элемент 5 задержки, элемент И 6,фазирующий блок 7, регистры 8 и 9, вычитающий блок 10, шины Старт 11, 20Стоп 12, Запуск 13, выходные шины 4и 15,шину 16 Готовность кода.Фазируюший блок 2 (7) включает первый17 и второй 18 входы блока 2(7), первыйэлемент НЕ 19, элемент И-НЕ 20; первый21 и второй 22 триггеры, второй элементНЕ 23 и выход 24 блока 2(7).Вычитающий блок 10 включает первый 25и второй 26 входы, блок 27 инверторов,сумматор 28, инвертор 29, резистор 30 и шину31 питания.30Преобразователь временных интервалов в код содержит генератор 1 импульсов, выход которого соединен с входом счетчика 3 и первыми входами фазируюших блоков 2 и 7. Второй вход фазируюшего блока 2 соединен с шиной 12 Стоп, а второй вход фазирующего блока 7 соединен с шиной 11 Старт и первым входом триггера 4, второй вход которого соединен с шиной 13 Запуск, а выход - с первым входом элемента И 6, Выход фазируюшего блока 7 40 соединен с управляющим входом регистра 8, а выход фазирующего блока 2 - с управляющим входом регистра 9 и входом элемента 5 задержки. Информационные входы регистров 8 и 9 объединены и соединены с выходами разрядов счетчика 3, а выходы регистров 8 и 9 соединены с входами вычитающего блока 1 О. Первые выходы вычитающего блока 10 являются первой выходной шиной 14 преобразователя, а второй выход вычитающего блока 10 является второй выходной шиной. 15 преобразователя и соединен с вторым входом элемента И 6, третий вход элемента И 6 соединен с выходом элемента 5 задержки, а выход соединен с шиной 16 Готовность кода и является третьей выходной шиной 55 преобразователя,Устройство работает следующим образом. Импульсы с выхода генератора 1 (фиг, 2 а) поступают на вход счетчика 3 и на первые входы фазируюших блоков 2 и 7. Счетчик 3 непрерывно ведет счет импульсов, поступающих с генератора 1 (фиг. 2 б, сигнал на выходе первого разряда счетчика 3). По команде Старт (фиг. 2 в), сфазированной на фазирующем блоке 7 (фиг. 2 г), код из счетчика 3 переписывается в регистр 8. По команде Стоп (фиг. 2 д), сфазированной на фазируюшем блоке 2 (фиг. 2 е), в регистр 9 переписывается код из счетчика 3. С выходов регистров 8 и 9 коды поступают на входы вычитаюшего блока 10, который из кода, записанного в регистре 9, вычитает код, записанный в регистре 8. На выходе вычитаюшего блока 10 получается код, равный количеству импульсов, поступивших на вход счетчика 3 между командами Старт и Стоп, т. е. на шине 14 преобразователя появляется код, пропорциональный временному интервалу между командами Старт и Стоп.Прием кода для дальнейшей обработки производится по сигналу Готовность кода (фиг. 2 е), который выдается в случае прихода через шину 13 Запуск на второй вход (О-вход) триггера 4 уровня логической 1 (фиг. 2 ж). В этом случае по первой же команде Старт (фиг. 2 в), поступающей на первый вход (С-вход) триггера 4, триггер 4 устанавливается в 1 (фиг. 2 з), разрешая прохождение через элемент И 6 сфазирова иной фазирующим блоком 2 (фиг. 2 е) и задержанной элементом 5 задержки (фиг. 2 и) команды Стоп. На выходе элемента И 6 формируется сигнал Готовность кода (фиг, 2 к). Элемент 5 задержки необходим для того, чтобы задержать выдачу сигнала Готовность кола на время, необходимое для проведения операции вычитания кодов вычитаюшим блоком 10,Если временной интервал между командами Старт и Стоп превышает макси. мально возможный интервал, то на втором выходе вычитаюшего блока 10 появляется уровень логического О, который поступает на третий вход элемента И 6 и запрещает выдачу сигнала Готовность кола, а также выдается на шину 15 преобразователя в качестве сигнала Переполнение.Фазирующие блоки 2 и 7, могут быть выполнены, например, на микросхемах (фиг. Зж), причем длительность команд Старт и Стоп должна быть больше периода следования импульсов генератора 1.Особенностью преобразователя временных интервалов в код является то, что при числе разрядов выходного кода преобразователя, равном У число разрядов счетчика 3, регистров 8 и 9 и вычитаюшего блока 10 должно быть равно %+1.5105 20 25 30 35 40 Формула изобретения 45 50 55 Вычитающий блок 10 выполняет вычисление по формулефО=Л 9 фВгде %1 О - код на выходе вычитающего блока 10;У 9 - код регистра 9;М 8 - код регистра 8.Вычитание производится за счет того, что на один вход сумматора 28 (фиг. 4) поступает с входа 26 прямой код регистра 9, а на второй вход сумматора 28 поступает проинвертированный блоком 27 инверторов код регистра 8 через вход 25. При этом возможны два случая; содержимое регистра 9 больше содержимого регистра 8 и содержимое регистра 9 меньше содержимого регистра 8.Рассмотрим работу вычитающего блока 10 в этих случаях, принимая, что временному интервалу между командами Старт и Стоп соответствует число 50 и число разрядов выходного кода %=8.Пусть в регистр 8 по команде Старт записывается число 26 в двоичном коде 000011010, которое поступает на вход 25 вычитающего блока 10 и инвертируется блоком 27 инверторов. Таким образом, на первый вход сумматора 28 поступает код 111100101.По команде Стоп в регистре 9 записывается число 76 в двоичном коде 001001100, которое через вход 26 вычитающего блока 10 поступает на второй вход сумматора 28. На выходе сумматора 28 получают число, равное 49 в двоичном коде111100101+00100100000110001Для получения требуемого значения кода (50) результат необходимо увеличить на 1.Пусть в регистр 8 по команде Старт записывается число 492 в двоичном коде 111101100, которое поступает на вход 25 вычитающего блока 10 и инвертируется блоком 27 инверторов. Таким образом, на первый вход сумматора 28 поступает код 000010011,По команде Стоп в регистре 9 записывается число 30 в двоичном коде 000011110, которое через вход 26 вычитающего блока 1 О поступает на второй вход сумматора 28.На выходе сумматора 28 также получают число 49 в двоичном коде000010011000011110000110001Для получения требуемого значения результат необходимо увеличить на 1.Для этой цели можно использовать вход переноса сумматора 28, подключив его через резистор 30 к шине 31.Восемь младших разрядов блока 10 выводятся на шину 14 преобразователя как код, соответствующий временному интервалу, а старший разряд, проинвертированный инвертором 29, выводится на шину 15 преобразователя в качестве сигнала Переполнение, а также поступает на второй вход элемента И 6.Если временной интервал не превышает динамического диапазона преобразователя, как в приведенных случаях, на шину 15 преобразователя и вход элемента И 6 выдается уровень логической 1, который разрешает выдачу сигнала Готовность кода элементом И 6.Рассмотрим случай, когда временной интервал превышает динамический диапазон преобразователя. Пусть в регистре 8 записано число 8 в двоичном коде 000001000, а в регистре 9 - число 266 в двоичном коде 100001010. На выходе сумматора 28 по- лучают 111110111+10000100100000010На шине 14 преобразователя появляется код 00000010, а на шине 15 - уровень логического 0, который запрещает выдачу сигнала Готовность кода элементом И 6 и является признаком превышения временным интервалом динамического диапазона преобразователя. В предлагаемом устройстве разрушается корреляционная связь между информацией, записанной в счетчике, и его порогом срабатывания за счет того, что счетчик считает постоянно, и информация, записанная в нем, является случайной по отношению к моменту прихода команды Старт.При использовании предлагаемого устройства в аналого-цифровых преобразователях время-импульсного типа происходит также разрушение корреляционной связи между цифровой и аналоговой частями АЦП за счет того, что счетчик постоянно считает, и его наводки на аналоговую часть в момент формирования временного интервала носят случайный характер. Преобразователь временны; интервалов в код, содержащий генератор импульсов, выход которого соединен с первь 1 м входом первого фазирующего блока, второй вход которого соединен с шиной Стоп, триггер, выход которого соединен с первым входом элемента И, а С-вход подключен к шине Старт, счетчик, элемент задержки, шины Запуск и Готовность кода, отлицающийся тем, что, с целью повышения точности преобразования временных интервалов в код за счет уменьшения дифференциальной нелинейности, в него введены второй фазирующий блок, первый и второй регистры и вычитающий блок, причем первый вход второго фазирующего блока соединен с выходом генератора импульсов и входом счетчика. выходы разрядов которого подключены/,а г Я ( аЬ 4 тавитель Л ед И. Верес ж 371 а СССР по 35, Раушс предприяти ПлетневаКорректорПодписноделам изобретенийая наб., д. 4/5, г. Ужгород, ул. П Со Техр Тира нного комите Москва, Ж -и графическоеРедактор И. ДербакЗаказ 7177/45ВНИИПИ Государств113035Г 1 роизводственно-по Патай открытии ктн к информационным входам первого и второго регистров, выходы которых соединены соответственно с первым и вторым входами вычитаюшего блока, информационные выходы которого являются первой выходной шиной преобразователя, вторая выходная шина которого подключена к выходу старшего разряда вычитаюшего блока и второму входу элемента И, третий вход которого соединен с выходом элемента задержки, вход которого подключен к выходу первого фазирующего блока и управляющему входу первого регистра, управляющий вход второго регистра соединен с выходом второго фазирующего блока, второй вход которого соединен с шиной Старт, шина Запуск подключена к 0-входу триггера, шина Готовность кода подключена к выходу элемента И и является третьей выходной шиной преобразователя.

СмотретьЗаявка

3899895, 23.05.1985

ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "КРАСНОДАРСКИЙ ЗИП"

ВИТКОВСКИЙ ПАВЕЛ АРТЕМОВИЧ, ПОЛУЯНОВ ВИКТОР ФЕДОРОВИЧ, ПОЧТЕР ВАДИМ МИХАЙЛОВИЧ

МПК / Метки

МПК: G04F 10/04

Метки: временных, интервалов, код

Опубликовано: 07.01.1987

Код ссылки

<a href="https://patents.su/4-1282073-preobrazovatel-vremennykh-intervalov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь временных интервалов в код</a>

Предыдущий патент: Устройство для определения середины импульсов периодической монотонной импульсной последовательности

Следующий патент: Электронные часы

Случайный патент: Динамическая струговая установка