Дискриминатор логических сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

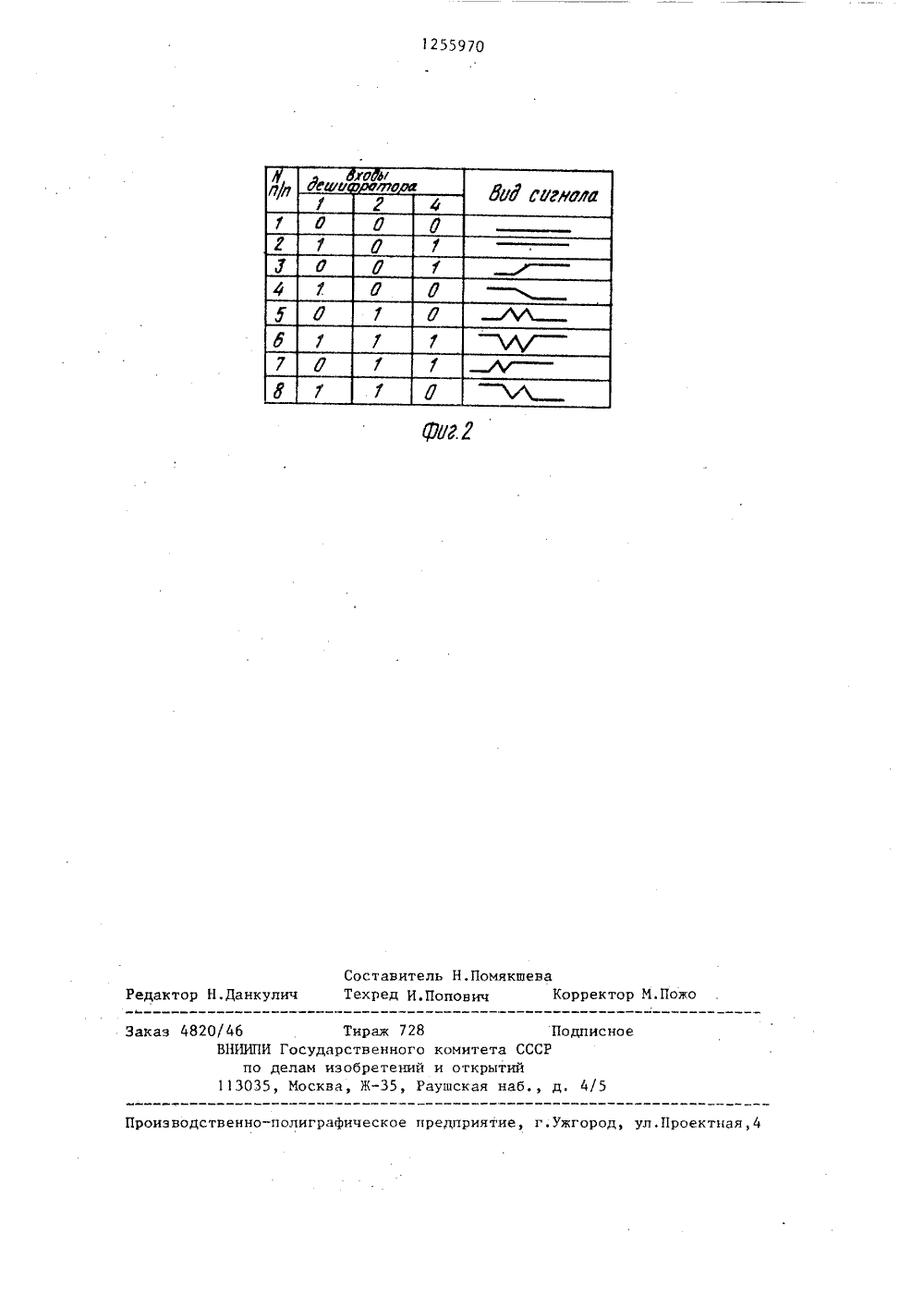

(21) 38 (22) 26 46) 07 72 Л,В 33А.И.ДерябАляев детельство СССРК 31/28, 27.02. тельство СССРК 31/28, 1975,ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРпо делАм изОБРетений и ОткРытий ПИСАНИЕ ИЗОБР АВТОРСКОМУ СВИДЕТЕЛЬСТВ(54) ДИСКРИМИНАТОР ЛОГИЧЕСКИХ СИГНАЛОВ(57) Изобретение относится к вычислительной технике, в частности к средствам контроля и диагностики неисправностей логических схем, Цельизобретения - повышение достоверности. Устройство содержит буферный усилитель 3, инвертор 4, дифференцирующие элементы 5 и б, триггеры 7 и 11,элемент 12 задержки, дешифратор 13 иблок 14 индикации. Введение элементов И 8 и 9 и элемента ИЛИ 10 исключает ложные комбинации сигналов навходах дешифратора 13 при распознавании многократных переходов из 0в "1" и наоборот. 2 ил.1 1Изобретение относится к вычислительной технике, в частности к средствам контроля и диагностики неисправностей логических схем.Цель изобретения - повьшение достоверности за счет исключения ложных комбинаций сигналов на входахдешифратора при распознавании мнои е ф игократных переходов из 0 в 1 инаоборот .На фиг . 1 изображен дискриминаторлогических сигналов ; на фиг, 2виды распознаваемых переходных проце ссов и соответствующие им комбинации сигналов на входах дешифра тора,Устройство содержит входы 1 и,буферный усилитель 3 , инв е р то р 4 ,дифференцирующие элементы 5 и 6 ,триггер 7 , элементы И 8 и 9 , элементИЛИ 1 0 , триггер 1 1 , элемент2 з адержки , дешифратор 1 3 , блок 1 4 индикации, выход 1 5 прерывания , вход 1 6управления .Вход 1 устройства соединен с входом буферного усилителя 3 . Вход 2устройства соединен с синхронизирующим входом первого триггера 7 , свходом элемента 1 2 задержки и входом установки в состояниеОвторого триггера 1 1 . Выход буферногоусилителя 3 подключен к инфо рм ационному входу первого триггера 7 , к.входу инв ертора 4 , к входу диффер енцирующего элемента б и к четвертомувходу дешифратора 1 3 . Прямой выходпервого , триггера 7 соединен с входомэлемента И 8 и с входом дешифра тора1 3 , инверсный выход первого триггера7 соединен с входом второго элементаИ 9, Выход инв ер то ра 4 соединен свходом дифференцирующего элемента 5 .Выход дифференцирующе го элемента 5соединен, с входом элемента И 8 . Выход дифференцирующе г о элемента 6 соединен г входом элемента И 9 . Выходэлемента И 8 соединен спе рвым входом элемента ИЛИ 1 О , к второму входу которого подключен выход элементаИ, 9.Выход элемента ИЛИ 1 О соединен свходом установки в состояние "1" второго триггера 11, Выход элемента 12задержки и прямой выход второго триггера 11 соединен соответственно свходами дешифратора 13. Вход 16 управления соединен с третьим входомцешифратора. Первый выход дешифраторУстройство работает следующим образом,При распознавании многократногоперехода с "0" на "1" сигналы на первом, втором и четвертом входах дешифратора 13 должны устанавливаться соответственно "0", "1", "1" 1 фиг,2,25 строка 7) .Для распознавания переходного процесса вход 1 дискриминатора подключается к исследуемой точке схемы,После этого к входам контролируемогоустройства прикладывается тест, длилтельность такта которого , (т.е.интервала времени между соседними изменениями входных сигналов исследуемой схемы) выбирается из условия 35 П е л.с сигде- постоянная времени элемента12 задержки;7 - максимально возможная проидолжительность переходногопроцесса в исследуемой точке схемы,С началом приложения теста на вход 2 подается кратковременный импульс, длительность которого выбирается из условия 40 45 п фгде- длительность импульса;- время от начала приложения теста ко входам схемы до начала изменения уровня сигнала в исследуемой точке.Этот импульс устанавливает в "0" 55 второй триггер 11, способствует записи в первый триггертого уровня сигнала, который имел место в иссле.дуемой точке схемы до его первого 50 255970213 соединен с блоком 14 индикации,Второй выход дешифратора 13 соединенс выходом 15 прерывания дискриминато ра.5В качестве первого триггера 7 может быть использован обычный триггертипа О, а в качестве второго триггера 11 - триггер типа КЯ. В качестведешнфратора 13 можно использоватьлюбой дешифратор на четыре информационных входа, имеющий синхровход.В качестве элементов индикации могут применяться печатающие устройства, различные устройства отображения информации с запоминанием результатов измерений и т.п, изменения в очередном такте, в данном случае значение сигнала равно11О , и поступает на вход элемента 1 2 задержки . Изменения уровня сигнала в контролируемой точке усиливаются буферным усилителем 3 и поступают на вход диффер енцирующе г о элемента 6 , а через инв е р то р 4 на вход дифференцирующе го элемента 5 , Элементы 5 , 6 и инв е р то р 4 предназначены для 1 0 выявления перехода с "О " на " 1 " ( элемент 6 ) и с "" на "0 " ( элемент 5 и инв ертор 4 ) , В случае перехода сигнала с уровня "О " на уровень " 1 " на выходе диффер енцирующе го элемента 6 1 5 появляется импульс положительной полярности . Если сигнал изменяется с 1" на О, то такой импульс появля - ется на вьжоде элемента 5.Так как в исходном состоянии (в 20 начале теста) сигнал в контролируемой точке был равен "О", триггер 7 установится в состояние "О" и на его инверсном выходе установится сигнал, равный "1", который подготовит к сра 25 батыванию элемент И. 9, а нулевой сигнал на прямом выходе триггера 7 закроет элемент И 8. Сигнал с выхода дифференцирующего элемента 6 проходит через открытый элемент И 9, элемент ИЛИ 1 О на вход установки в состояние "1" второго триггера 11, пе. - реводя последний в единичное состояние. Таким образом, после окончания переходных процессов к контролируемой точке схемы на первом, .втором и четвертом входах дешифратора 13 уста новятся следующие значения: на первом входе, соединенном с выходом .- пеРвого триггера 7, - О , на вто ром, соединенном с выходом второго триггера 11-, - ; на четвертом, соединенном с выходом буферного усилителя 3, - "1". С приходом сигнала сс выхода элемента 2 задердки (сиг нал задержанного на время 1 ) на вход синхронизации дешифратора 13 происходит дешифрация комбинации сиг налов на его входах. Сигнал с дешифратора 13 поступает на вход блока 14индикации.При необходимости распознавания определенного вида .переходного про 970 4цесса в исследуемой схеме и выдачи сигнала останойки с выхода 15 устройства дешифратор 13 настраивается при помощи входа 16 управления.Формула изобретенияДискриминатор логических сигналов, соДержащий буферный усилитель, инвертор, два дифференцирующих элемента, элемент задержки, два триггера, дешифратор, блок индикации, вход которого соединен с первым выходом дешифратора, первый вход которого соединен с прямым выходом первого триггера, второй вход - с прямым выходом второго триггера, а третий вход - с,входом управления, информационный вход дискриминатОра соединен с входом буферного усилителя, выход которого соединен с входом первого дифференцирующего элемента, а через инвертор с входом второго дифференцирующего элемента, второй выход дешифратора соединен с выходом прерывания дискриминатора,о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности за счет исключения ложных комбинаций сигналов на входах дешифратора при распознавании сигналов, содержащих многократные переходы из,О в "11, в него введены два элемента И, элемент ИПИ и вход синхронизации, соединенный с синхровходом первого триггера, с входом сброса второго триггера и через элемент задержки с синх-, ровходом дешифратора, четвертый вход которого соединен с выходом буферного усилителя, выходы первого и второго дифференцирующих элементов соединены соответственно с первыми .входами первого и второго элементов И, вторые входы которых соединены со-, ответственно с инверсным и прямым выходами первого триггера, информационный вход которого соединен с выходом буферного усилителя, выходы элементов И соединены с входами элемента ИЛИ,.выход которого соединенс установочным входом второго триг"гера, второй триггер выполнен ЙЗтриггером.1255970 Составитель Н.ПомякшеваТехред И.Попович Корректор М.Пожо Редактор Н,Данкулич Заказ 4820/46 Тираж 728 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5Производственно-полиграФическое предприятие, г.ужгород, ул,Проектная,4

СмотретьЗаявка

3815595, 26.11.1984

ПЕРМСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА В. И. ЧУЙКОВА

ВИКЕНТЬЕВ ЛЕОНИД ФЕДОРОВИЧ, ДЕРЯБИН АЛЕКСАНДР ИВАНОВИЧ, РАЧИНСКИЙ АЛЕКСАНДР АЛЕКСЕЕВИЧ, АЛЯЕВ ЮРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G01R 31/3177

Метки: дискриминатор, логических, сигналов

Опубликовано: 07.09.1986

Код ссылки

<a href="https://patents.su/4-1255970-diskriminator-logicheskikh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Дискриминатор логических сигналов</a>

Предыдущий патент: Устройство для измерения тепловой постоянной времени переход-корпус полупроводниковых приборов

Следующий патент: Устройство для контроля параметров электрических схем

Случайный патент: Стенд для испытания на выносливость зубьев зубчатых колес