Способ когерентного приема сигналов амплитудно-фазовой модуляции и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

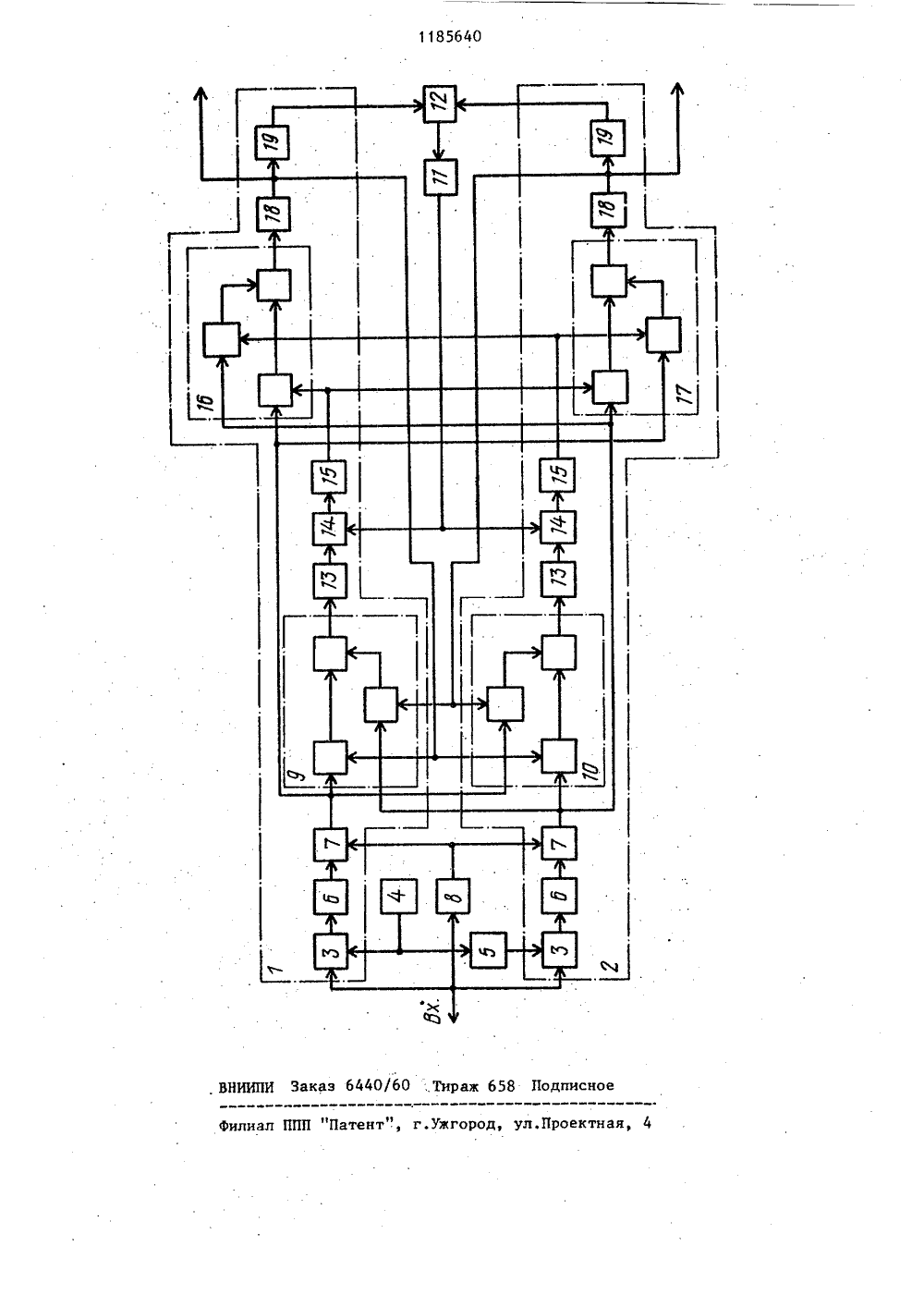

,85. Бюл, У 38Балашов, П,Я. Нудельман,еев и Ю.В, Шевченкокий электротехнический инзи им. А.С. Попова94,62(088.8)ское свидетельство СССРкл, Н 04 1. 27/18, 1978.ФРГ М 2101804,27/22, 1978.(54) СПОСОБ КОГЕРЕНТНОГО ПРИЕМА СИГНА ЛОВ АМПЛИТУДНО-ФАЗОВОЙ МОДУЛЯЦИИ И УСТРОИСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ, (57) 1. Способ когерентного приема сигналов амплитудно-фазовой модуляции, заключающийся в том, что входной аналоговый сигнал амплитуднофазовой модуляции с неизвестной фазой преобразуют в дискретный несинхронный сигнал амплитудно-фазовой модуляции, выделяют дискретный синхронный низкочастотный сигнал амплитудно-фазовой модуляции и преобразуют его в сигнал цифровой информации, отличающийся тем,о, с целью повышения помехоустойчивости при скачкообразном изменен фазы, перед выделением дискретногосинхронного низкочастотного сигнала амплитудно-фазовой модуляции дискрет ный несинхронный сигнал амплитуднофазовой модуляции преобразуют в дискретный несинхронный низкочастотный сигнал амплитудно-фазовой модуляции и выделяют сигнал неизвестной фазы.2. Устройство для когерентногоприема сигналов амплитудно-фазовоймодуляции, содержащее блок тактовой синхронизации, опорный генератор, вьгход которого подключен к входу фазовращателя, а в синфазном и квадратурном подканалах перемножитель, выходкоторого подключен к входу фильтра,выход которого соединен с первымвходом дискретизатора, второй входкоторого соединен с выходом блокатактовой синхронизации, вход которого подключен к первому входу перемножителя синфазного подканала и к первому входу леремножителя квадратурного подканала, второй вход которогосоединен с выходом фазовращателя,вход которого соединен с вторым входом перемножителя синфазного подканала, о т л и ч а ю щ е е с я тем,что в него введены основной накопитель и сумматор, а в синфаэный иквадратурный подканалы в . последовательно соединенные блок снятия манипуляции, дополнительный накопитель,делитель уровня сигнала, линия задержки,блок снятия фазового рассогласования, решающий блок и квадратор,выход которого подключен к соответствующему входу сумматора, выход которого подключен к входу. основного накопителя, выход коТорого подключен квторому входу делителя уровня сигналасинфазного подканала и к второму входу делителя уровня сигнала квадратурного подканала, выходы дискретиэаторов синфазного и квадратурного подканалов соединены с первыми входами блоков снятия манипуляции и с вторымивходами блоков снятия фазового рассогласования, выходы решающих блоковподключены к вторым входам блоковснятия манипуляции, при этом второйвход блока. снятия манипуляции син1185640 разного подканала соединен с третьимвходом блока снятия манипуляции квадратурного подканала, второй вход которого подключен к третьему входублока снятия манипуляции синфазногоподканала, первый вход блока снятияфазового рассогласования которогосоединен с третьим входом блока снятия фазового рассогласования квадратурного подканала первый вход которого подключен к третьему входублока снятия Фазового рассогласования синфазного подканала,второй вход Изобретение относится к техникесвязи и может быть использовано вустройствах преобразования сигналов.систем передачи данных,Целью изобретения является повышение помехоустойчивости при скачкообразном изменении Фазы.На чертеже изображена структурная электрическая схема устройствадля .осуществления предлагаемого способа.Устройство содержит синфазный 1и квадратурный 2 подканалы, перемножители 3, опорный генератор 4, Фазовращатель, 5, фильтры 6, дискретизаторы 7, блок 8 тактовой синхронизации, блок 9 снятия манипуляциисинфазного подканала, блок 10 снятия манипуляции квадратурного канала, основной накопитель 11, сумматор 12, дополнительные накопители 13,делители 14 уровня сигнала, линии15 задержки, блок 16 снятия фазового рассогласования синфазного канала, блок 17 снятия фазового рассогласования квадратурного канала,решающие блоки 18, квадраторы 19,Прием сигналов амплитудно-фазо-вой модуляции осуществляется следунщим образом,Принимаемый сигнал амплитудноФазовой модуляции поступает на первый вход перемножителей 3 синфазного 1 и квадратурного 2 подканалов,на вторые входы которых подано напряжение от (несинхронного) опорногогенератора 4, частота которого равкоторого соединен с четвертым входомблока снятия фазового рассогласования квадратурного подканала, второйвход которого соединен с четвертымвходом блока снятия Фазового рассогласования синфазного подканала, выход дискретизатора которого подключен к четвертому входу блока снягияманипуляции квадратурного подканала,выход дискретизатора которого подключен к четвертому входу блока снятияманипуляции синфаэного подканала,на частоте принимаемого сигнала, афаза случайна. Напряжение (несинхронного) опорного генератора 4, поданное на перемножитель 3 квадратурного подканала, сдвинуто по Фазе на90 посредством фаэовращателя 5. Выходы перемножителей 3 параллельночерез Фильтры 6 поступают на первыевходы дискретизаторов 7, на вторые 10 входы которых подано напряжение отблока 8 тактовой синхронизации, работающего по входному сигналу, поступающего на его вход. 5 Входы дискретиэаторов 7 соединены с входами блоков 9 и 1 О снятия манипуляции по синфаэному 1 и квадратурному 2 подканалам. 20 С другой стороны Выходы дискретизаторов 7 соединены с входами блоков 16 и 17 снятия Фазового рассогласования по синфазному 1 и квадратурному 2 подканалам. Вторые входы 25 блоков 16 и 17 снятия фазового ра.ссогласования соединены с выходамидискретизаторов 7 синфазного (квадратурного) подканала, а первые ихвходы через линии 15 задержки соединены с делителем 14 уровня сигнала.Четвертые входы блоков 16 и 17 снятия фазового рассогласования соединены с выходом дискретизатора 7квадратурного 2 подканала (синфазного 1 подканала), а третьи их входы через линию 15 задержки соединены с делителем 14 уровня сигнала3квадратурного 2 подканала 1 (синфазного 1 подканала). Постоянная времени линии 15 задержки равна длительности посылки входного сигнала. Выходы блоков 16 и 17 снятия фазового рассогласования подключены к входам решающих блоков 18. 11856404Решающие блоки 18 представляютсобой ряд пороговых устройств, выносящих решения о синфазной либо квадратурной составляющих входного сигнала в результате минимизации некоторого критерия качества (например, среднеквадратичной ошибки),

СмотретьЗаявка

3633968, 05.08.1983

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

БАЛАШОВ ВИТАЛИЙ АЛЕКСАНДРОВИЧ, НУДЕЛЬМАН ПАВЕЛ ЯКОВЛЕВИЧ, ПАНТЕЛЕЕВ ВИКТОР ВЛАДИМИРОВИЧ, ШЕВЧЕНКО ЮРИЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H04L 27/233

Метки: амплитудно-фазовой, когерентного, модуляции, приема, сигналов

Опубликовано: 15.10.1985

Код ссылки

<a href="https://patents.su/4-1185640-sposob-kogerentnogo-priema-signalov-amplitudno-fazovojj-modulyacii-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ когерентного приема сигналов амплитудно-фазовой модуляции и устройство для его осуществления</a>

Предыдущий патент: Устройство для приема частотно-манипулированных сигналов

Следующий патент: Детектор сигналов двукратной относительной фазовой телеграфии

Случайный патент: Устройство для поштучной выдачи листовых деталей из стопы и подачи их в рабочую зону