Устройство формирования эталонных цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

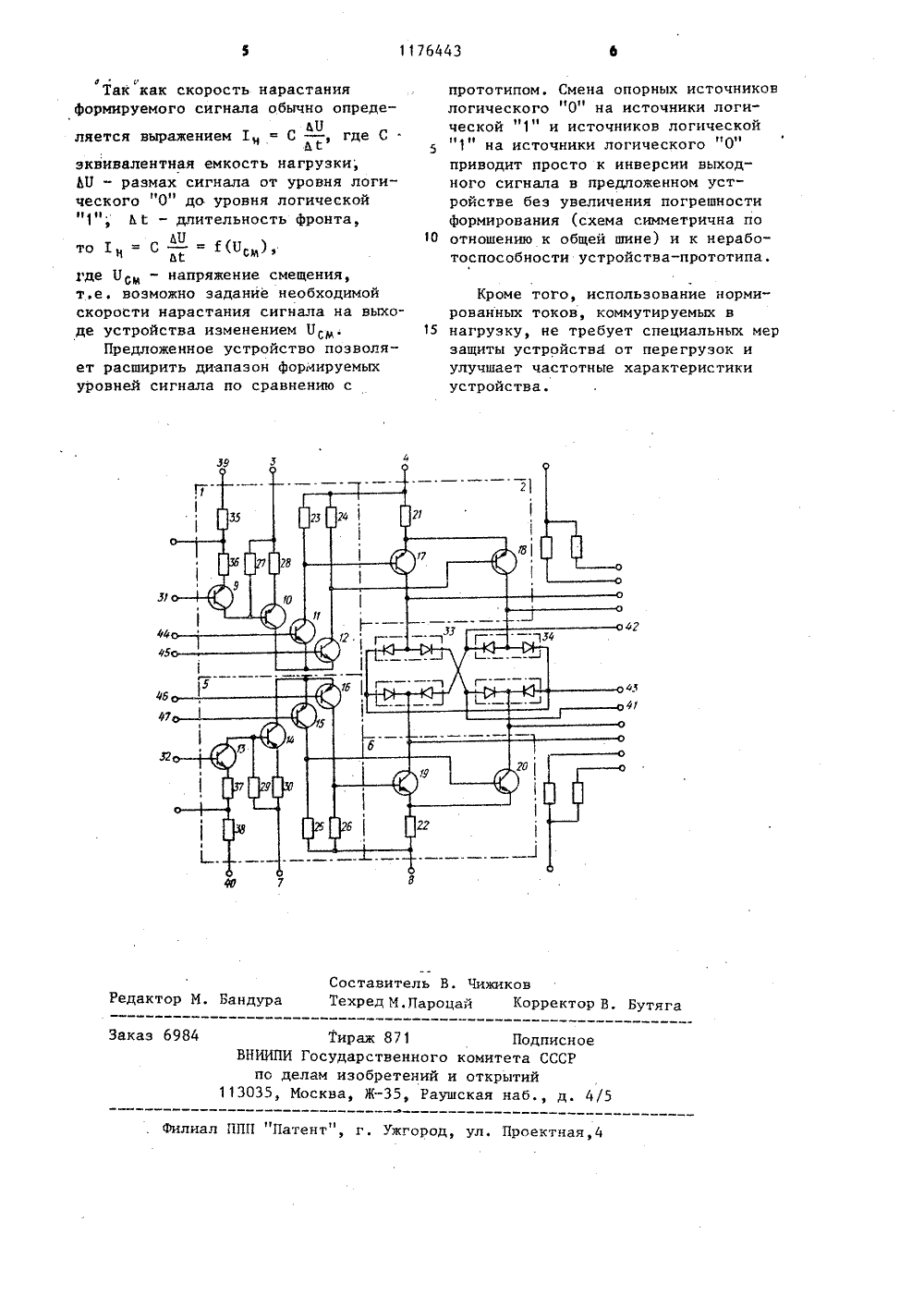

(5 БР 21 Бюл. Р 32 лев и Л Д, 8 (088.8)параметро икросхем. каса. М.:265-266, с. 267-272 осов цифровых дио и ис. 6.19. рис 6 20 вт ь- ый стомир ателеи уровня рвый резистор ди - тст одсо иены ереэ и к втор соо н никам напряж ния, третии иоответственнолючателей токо етв ыи тором транзивторо сторыо переыпос вторые сторов первого в вы перво ьывод лне нными екторов хеме с объедин в цепи их кол ссот и пямитте УДАРСТВЕННЫЙ НОМИТЕТ ССС ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ СПИ САНИ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(54)(57) УСТРОЙСТВО ФОРМИРОВАНИЯ ЭТАЛОННЫХ ЦИФРОВЫХ СИГНАЛОВ, содержащее последовательно соединенные первый переключатель тока и первый формирователь уровня, содержащие соответственно первь 1 й и второй источники напряжения, и последовательно соединенные и выполненные на транзисторах противоположной полярности второй переключатель тока и второй формирователь уровня, содержащие соответственно третий и четвертый источники напряжений,.пер вый и второй переключатели тока выполнены на первом, втором, тре ем и четвертом транзисторах, пер и второй формирователи уровней в полчены на пятом и шестом транзи рах соответственно в -итипа и Ий-типа, эмиттеры пятого тран тора соответственно первого и вт му и четвертому ист ЯО 1176 включены второй и третий резисторы,база и эмиттер второго транзистораП-р-и- и-птипа соответственнопервого и второго переключателей токов подключены к первым выводам соответственно четвертого и пятого резисторов, базы первых транзисторовпервого и второго переключателейтоков подключены к первым входнымшинам устройства формирования эталонных цифровых сигналов, о т л ич а ю щ е е с я тем, что, с цельюрасширения функциональных воэможностей путем обеспечения работы отисточников сигнала противоположныхполярностей, в него введены первыйи второй диодные мосты, последовательно соединенные шестои и седьмоирезисторы первого и второго переключателей тока, подключенные между эмиттером первого транзистора и орыми входными шинами устройстваформирования эталонных цифровыхсигналов, причем первый транзисторпервого переключателя тока выполненна транзисторе-птипа, а третийи четвертый транзисторы первогопереключателя тока выполнены П Отипа, формирователи уровня выполнены по схеме переключателей тока собъединенными эмиттерами, вторые выводы второго и третьего резисторови соответственно четвертого и пятогорезисторов первого переключателятока подключены соответственно к источнику напряжения источнику напряжения торого и третьего ре тственно четвертого резисторов второго переключа1176443 теля подключены соответственно кчетвертому источнику напряжения ик третьему источнику напряжения,коллекторы пятого и шестого транзисторов первого формирователяуровней подключены к точкам соединения анодов первого и второгодисдного мостов, точки соединениякатодов которых подключены соответственно к коллекторам пятого ишестого транзисторов второго форми 1Изобретение может быть использовано в радиоэлектронной аппаратуреразличного назначения, в частностив многоканальной аппаратуре контроля и измерения параметров цифровыхсхем для формирования эталонныхцифровых сигналов с заданными уровнями и длительностью Фронтов сигналов,Цель изобретения - расширениефункциональных возможностей устройства путем обеспечения работы отисточников сигнала противоположныхполярностей,.На чертеже нрецставлена принципи.альная электрическая схема устройства Формирования эталонных цифровых сигналов.устройство формирования эталонных цифровых сигналов содержитпоследовательно соединенные первыйпереключатель 1 тока и первый Формирователь 2 уровня, содержащие соответственно первый и второи источники 3, 4 напряжения, и последовательно соединенные и выполненныена транзисторах противоположнойполярности второй переключатель 5тока и второй Формирователь 6 уровня, содержащие соответственно третий и четвертый источники 78 напряжений, первый перекпючатель 1 тока выполнен на первом, втором,третьем и четвертом транзисторах9-12, второй переключатель 5 токавыполнен на транзисторах 13-16,первый и второй формирователи 2,6 уровней выполнены на пятом и шестом транзисторах 17,18 ссответствегн с 1 -1типа и соответственно рователя уровней, первые точкисоединения анод-катод первого ивторого диодного мостов подключенык уровню логического нуля и соответственно к урсэню логической единицы, вторые точки соединения анодкатод первого и второго диодногомостов соединены между собой и подключены к выходу устройстваФормирования эталонных цифровыхснгналов,219, 20 п П -типа, эмиттеры пятоготранзистора соответственно первогои второго формирователей 2, 6 уровня подсоединены через первый резистор 21 и соответственно резистор22 к соответствующьм второму и четвертому источникам 4, 8 напряжения, третий и четвертый транзисторы 11, 12 и 15, 16 соответственна 1 О первого и второго переключателей1 и 5 токоь выполнены по схеме собъединенными эмиттерами и в цепиих коллекторов включены второй итретий резисторы соответственно 23, 15 24 и 25, 26, база и эмиттер вторсгстранзистора и - Р-и- и- и- р-типасоответственно первого и второгопереключателей 1 и 5 токов подключены к первым выводам соответст венно четвертого и пятого резисторовсоответственно 27, 28,29, 30 базыпервых транзисторов соответственнопервого и второго переключателей1, 5 токов являются соответственно 25 гервым и вторым входами 31, 32,устройства формирования эталонныхцифровых сигналов, первый и второйдиодные мосты 33 и 34, последовательно соединенные шестой и седьмойрезисторы 35, 36 и 37, 38 соотьетственно первого и второго переключателей 1 и 5 тока, подключенные между эмиттером первого транзистора9 и 13 и вторыми входными шинами 3539 40 устройства формирования эталонных цифровых сигналов, причемпервый транзистор первого переключателя 1 тока выполнен на транзисторе- П- в ти, а третий и четвертьйтранзисторы первого пе 1 ектючатепя11 7644 1 35 40 45 50 55 тока цыполцець 1 П -1-ц -тиц, Формирователи 2 и 6 уровня выполнены посхеме переключателей тока с объединенными эмиттерами, вторые выводывторого и третьего резисторов 23,24и соответственно четвертого и пятого резисторов 27,28 переключателя 1тока подключены к второму источнику 4 положительного напряжения исоответственно к первому источнику3 отрицательного напряжения, вторыевыводы второго и третьего резисторов 25, 26 и соответственно четвертого и пятого резисторов 29, 30второго переключателя 5 тока подклю.чены к четвертому источнику 8 отрицательного напряжения и соответственно к третьему источнику 7 положительного напряжения, коллекторыпятого и шестого транзисторов 17,18 первого формирователя 2 уровней .подключены к точкам соединенияанодов первого и второго диодногомостов 33, 34, точки соединения катодов которых подключены соответственно к коллекторам пятого и шестого транзисторов 19, 20 второгоформирователя уровней, 6 первыеточки соединения анод-катод первогои второго диодного мостов подключены к шине логического нуля 41 исоответственно к .шине логическойединицы 42, вторые точки соединенияанод-катод первого и второго диодного мостов соединены между собойи подключены к выходу 43 устройства формирования эталонных цифровыхсигналов, входы 44, 45, 46, 47 являются дополнительными входами устройства.Устройство работает следующимобразом. При поданном питании сигнал высокого уровня (логическая "1" ТТЛ уровня) на базе транзистора 9 отключает генераторы токов ца транзисторах 9-10 и 13-19, так как переходы база-эмиттер транзисторов 9 и 13 находятся в обратносмещенном состоянии. Все транзисторы устройства закрыты независимо от уровней логических сигналов на информационных входах (базах транзисторов 11, 12, 15, 16) устройства, при этом переходы диодов в мостах 33, 34 сме. щецы в обратном цаправлении и устройство находится в третьем (отключенном от нагрузки) состоянии. На 1 О 15 20 25 30 лцчие сигнала низкого уровня (логический "0" ТТЛ уровня) на базе транзистора 9 включает генераторы токов на транзисторах 9, 10, 13, 14 и с коллекторов транзисторов 10, 14 задаются токи питания переключателей токов на транзисторах 11, 12 и 15,16, состояние устройства и полярность формируемого сигнала определяются в этом случае полярностью сигналов на базах транзисторов 1 1, 15, 12, 16.При высоком уровне, управляющего сигнала на базах транзисторов 11, 16 и низком уровне управляющего сигнала на базах транзисторов 12, 15 транзисторы 11, 15 включены, в цепи баз транзисторов 17, 20 заданы управляющие токи, практически равные токам питания первых переключателей 1,5 токов. Транзисторы 17, 20 работают при этом как генераторы тока питания диодного моста 33. Токи, снимаемые с коллекторов транзисторов 17, 20 смещают переходы диодов моста 33 в прямом направлении, подключая источник опорного напряжения логического "0" к нагрузке (выходу устройства).При низком уровне управляющего сигнала на базах транзисторов 11, 16 и высоком уровне управляющего сигнала на базах транзисторов 10, 12 транзисторы 11, 15 выключены, а транзисторы 12, 16 включены и в цепи баэ транзисторов 17, 20 в диод. ный мост 33 подаются токи, посред ством которых формируется на выходе устройства сигнал с заданным опорным уровнем логической "1" (аналогично формированию сигнала суровнем логического нО"). Особенностью работы устройства является то, что формирование эталонного цифрового сигнала осуществляется номированным током (током заданного значения), отдаваемым в нагрузку. При этом в момент переключения сигналов в нагрузку с диодного моста снимается весь ток 1, а при достижении заданного опорного уровня происходит перераспределение токов, протекающих через диоды моста, и уровень формируемого) сигнала определяется как сумма падений напряжений на диодах моста Б- = П +Бт" Ф Р - у -П - Поп.1176443 оставитель ехред М. Па Чижиков Редактор И. Бандур каэ 698 Тираж Государ лам изо осква,871 Подписноетвенного комитета СССРретений и открытийФилиал ППП "Патент, г. Ужгород, ул. Проектн ю иТак как скорость нарастания формируемого сигнала обычно опредеьН ляется выражением 1С - где Снэквивалентная емкость нагрузки, И " размах сигнала от уровня логического "О" до уровня логической "1", Е С - длительность фронта, то 1= С в= (Псе)4 Нгде Уц - напряжение смещения, т.е. возможно задание необходимой скорости нарастания сигнала на выходе устройства изменением Н,.Предложенное устройство позволяет расширить диапазон формируемых уровней сигнала по сравнению с прототипом. Смена опорных источниковлогического "О" на источники логической "1" и источников логической1 на источники логического "О"приводит просто к инверсии выходного сигнала в предложенном устройстве без увеличения погрешностиформирования (схема симметрична по 10 отношению к общей шине) и к неработоспособности устройства-прототипа. Кроме того, использование нормированных токов, коммутируемых в 15 нагрузку, не требует специальных мерзащиты устройства от перегрузок и улучшает частотные характеристики устройства. и Корректор В, Бутяг

СмотретьЗаявка

3579839, 15.04.1983

ПРЕДПРИЯТИЕ ПЯ А-7438

ЯКОВЛЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, НОСОВ ЛЕОНИД ДАНИЛОВИЧ

МПК / Метки

МПК: H03K 5/00

Метки: сигналов, формирования, цифровых, эталонных

Опубликовано: 30.08.1985

Код ссылки

<a href="https://patents.su/4-1176443-ustrojjstvo-formirovaniya-ehtalonnykh-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство формирования эталонных цифровых сигналов</a>

Предыдущий патент: Цифровой генератор сигналов

Следующий патент: Формирователь импульсов

Случайный патент: Приемник для сбора живицы