Устройство для распределения заданий между эвм в многомашинной вычислительной системе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

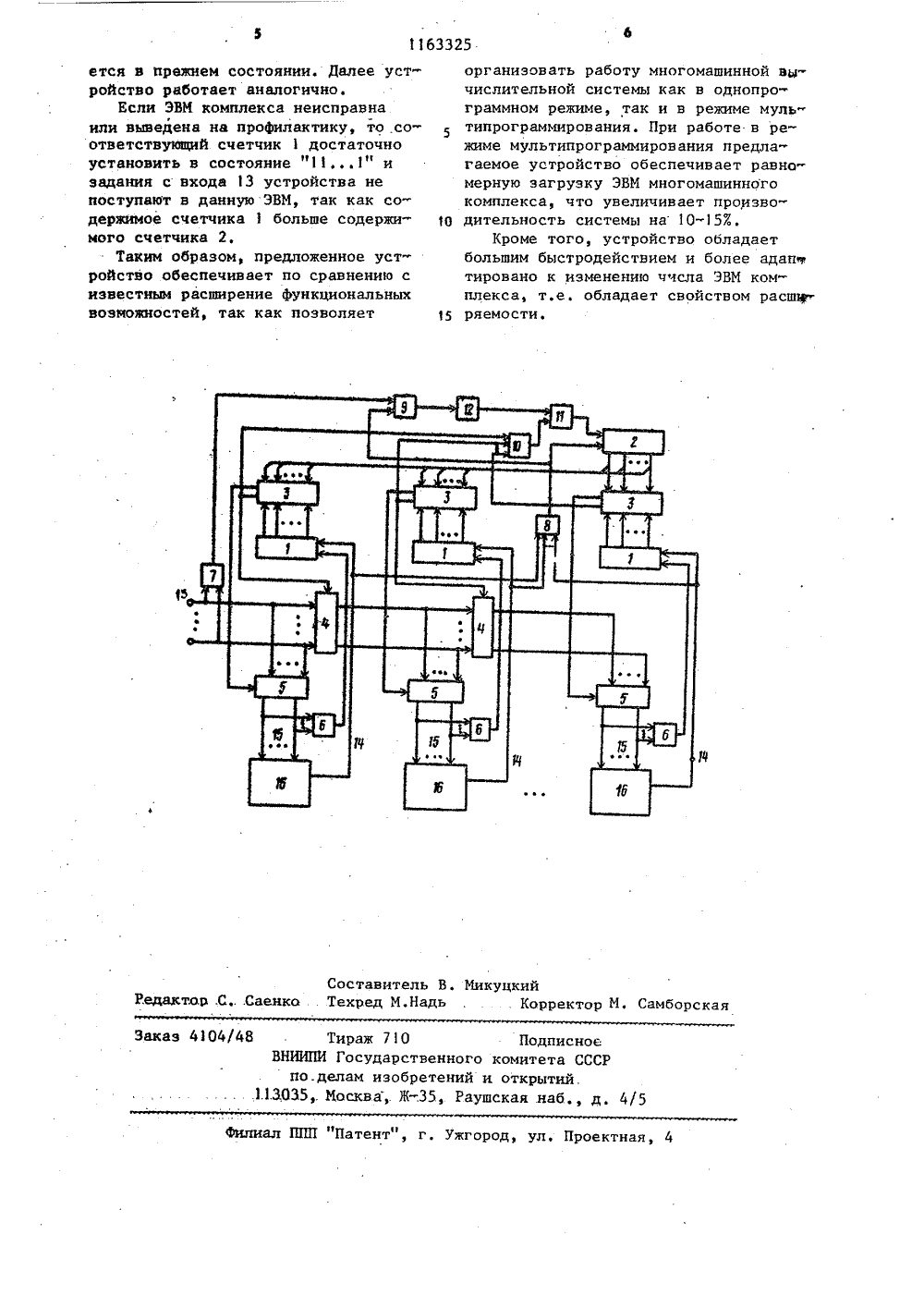

СОЮЗ СОВЕТСКИХСОЦИАЛИСТ ИЧЕСНИХРЕСПУБЛИК 9 00.р" ляГ,. ,:; , с:,ОПИСАНИЕ ИЗОБРЕТЕНИЯ ИДЕ ВТОРСНО И 23 Н.ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54 )(57 ) УСТРОЙСТВО ДЛЯ РАСПРЕДЕНИЯ ЗАДАНИЙ МЕЖДУ ЭВМ В МНОГОВБЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержгруппу элементов ИЛИ и элемент И,о т л и ч а ю щ е е с я тем, что,с целью расширения функциональныхвозможностей путем обеспечения распределения заданий между ЭВМ,работающими в мультипрограммном режиме, в него введены реверсивныйсчетчик минимального числа заданий,два элемента И, два элемента ИЛИ,элемент задержки, и схем сравнения(где и - количество ЭВМ в системе),и реверсивных счетчиков количествазаданий, первую группу из и блоковэлементов И, вторую группу из (и)блоков элементов И, причем группавходов первого блока элементов Ипервой группы соединена с группойвходов кодов заданий устройства и свходами первого эл".мента ИЛИ, выходкоторого соединен с первым входомвторого элемента ИЛИ, второй входкоторого соединен с выходом третьего элемента ИЛИ и с вычитающим входом реверсивного счетчика минималь-ного числа заданий, суммирующийвход которого соединен с выходом 801163325 А первого элемента И, первый вход которого через элемент задержки соединен с выходом второго элемента ИЛИ, а второй вход первого элемента И соединен с выходом второго элемента И, входы которого соединены с первыми входами соответствующих схем сравнения, второй выход каждой яз-которых соединен с входом соот ветствующего блока элементов И первой группы, группа вьмодов, блоков элементов И второй группы соединена с соответствующей группой выходов устройства и с группой входов соответствующего элемента ИЛИ группы, выход которого соединен с суммирук- щим входом соответствующего реверсивного счетчика количества заданий, вычитающий вход которого соединен с соответствующим ответным входом устройства и с соответствующим входом третьего элемента ИЛИ устройства, а группа выходов каждого реверсивного счегчика количества заф даний соединена с первой группой входов соответствующей схемы сравнения, вторая группа входов которой соединена с выходом реверсивного счетчика минимального числа заданий, при этом группа входов каждого д-го (где - 1 и) блока элементов И второй группы соединена с группой входов 1-го блока элементов И первой группы, а вход -го блока элементов И второй группы соединен с вторым выходом д-й схемы сравнения, причем группа выходов каждого д-го (1 = 1 и) блока элементов И первой группы соединена с группой входов ( + 1)-го блока элементов И первой группы.Изобретение относится к вычислительной технике, в частности к устройствам распределения заданий между ЭВМ, и может быть использовано в многомашинных вычислительных системах, работающих в режиме мультипрограммирования.Известно устройство обмена, содержащее линейный блок, блок управления поиском и обменом, счетчик номера або 10 нента, дешифратор поиска готовности абонентов, сборку сигналов требований обмена 13.Недостатками данного устройства являются низкое быстродействие и слож 15 ность.Наиболее близким по технической сущности к изобретению является устройство для распределения заданий процессорам содержащее блок управления, к первому входу которого подключен выход элемента ИЛИ, ко вторым входам блока управления подключены выходы регистра готовности процессов,25 а к третьи.: входам - шины необходимого числа процессоров, первый и второй выходы блока управления соединены с входами регистра сдвига, третин выход блока управления подключен к шине отказа от распределения заданий, выходы регистра сдвига подключены к входам элемента ИЛИ и к первым входам .каждой из и (и - число заданий) групп, ко вторым входам которых подключены выходы регистра готовности процессо- З 5 ров к третьим входам элементов И под,лключеиы шины номера задания, выходы каждой группы элементов И соединены с соответствующими входами группы элементов ИЛИ, выходы которых соеди40 иены с нулевьяи входами регистра сдви" га и регистра готовности процессоров, к входам процессоров подключены выхо,ды соответствуецих групп элементов И, а выводы процессоров соединены с45 единичнйми входами регистра готовности процессоров 23Недостатками известного устроис- ва являются ограниченные функциональ" 50 ные возможности, связанные с тем, что устройство не может быть использовано при распределении заданий между ЭВМ, рйботаиерЬИ 3 мультипрограммном режиме, а также низкое быстро 55 действие, обусловленное использованием последовательно работающего регистра сдвига". Цель изобретения - расширение функциональных возможностей путем обеспечения распределения заданий между ЭВМ, работающими в мультипрограммном режиме.Поставленная цель достигается тем, что в устройство для распределения заданий между ЭВМ в многомашинной вычислительной системе содержащее группу элементов ИЛИ и элемент И, введены реверсивный счетчик минимального числа заданий, два элемента И, два элемента ИЛИ, элемент задержки, и схем сравнения (где и - количество ЭВМ в системе) и реверсивных счетчиков количества заданий, первую группу из и блоков элементов И, вторую группу иэ (п) блоков элементов И, причем группа .ходов первого блока элементов И первой группы соединена с группой входов кодов заданий устройства и с входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом - третьего элемента ИЛИ и с вычитающим входом реверсивного счетчика минимального числа заданий, суммирующий вход которого соединен с выходом первого элемента И, первый вход которого через элемент задержки соединен с выходом второго элемента ИЛИ, а второй вход первого элемента И соединен с выходом второго элемента И, входы которого соединены с первыми входами соответствующих схем сравнения, второй выход каждой из которых соединен с входом соответствующего блока элементов И первой группы, группа выходов блоков элементов И второй группы соединена с соответствующей группой выходов устройства и с группой входов соответствующего элемента ИЛИ группы, выход которого соединен с суммирующим входом соответствующего реверсивного счетчика количества заданий, вычитающий вход которого соединен с соответствующим ответным входом устройства и с соответствующим входом третьего элемента ИЛИ устройства, а группа выходов каждого реверсивного счетчика количества заданий соединена с первой группой входов соответствующей схемы сравнения, вторая группа входов которой соединена с выходом реверсивного счетчика минимального числа заданий, при этом группа входов каждого д-го (где= 1 и) блока элементовИ второй группы соединена с группой входов 1."го блока элементов И первой группы, а вход -го блока элементов И второй группы соединен с вторым выходом -й схемы сравнения, причем группа выходов каждого д-го ( = 1, иблока элементов И первой группы соединена с группой входов (1. + 1)- го блока элементов И первой группы.На чертеже представлена структурная схема предлагаемого устройства,Устройство содержит и реверсивных счетчиков 1 количества заданий, реверсивный счетчик 2 минимального числа заданий, и схем 3 сравнения, группы блоков элементов И 4 и 5, группу элементов ИЛИ 6, элементы ИЛИ 7-9, элементы И 10 и 11, элемент 12 задержки, группу входов 13 кодов заданий устройства, ответные входы 14, группы выходов 15. Кроме того, показаны и ЭВМ 16. Устройство работает следующим образом.В исходном состоянии счетчики и 2 находятся в нулевом состоянии,. т.е, число заданий в ЭВМ равно нулю. На соответствующих первых выходах схем 3 сравнения действует единичный сигнал, который разрешает работу группы элементов И 5, На вторыхвыходах схем 3 - нулевой сигнал, поюэтому группы элементов И 4,и элементов И 10 и 11 закрыты,На входы устройства подается в- разрядный код задания, который через первую группу элементов И 5 поступает в первую ЗВМ. Одновременно с выхода первой группы элементов ИЛИ 6 посту". пает сигнал на вход суммирования первого реверсивного счетчика 1. С выхода элемента ИЛИ 7 сигнал в ревер сивный счетчик 2 не поступает, так как элемент И 11 закрыт. После поступления первого задания в ЭВМ соответствующий реверсивный счетчик 1 уста навливается в состояние "1". Зто приводит к тому-что единичный сигнал на первом выходе первой схемы 3 снимается, закрывая соответствующую группу элементов И 5. Одновременно единичный сигнал возникает на втором выходе первой схемы 3, разрешая работу первой группы элементов И 4.Код очередного задания, поступающий на вход 13 устройства, пройдя.первую группу элементов И 4, поступа"ет во вторую ЭВМ через вторую груп"; пу элементов И 5. Одновременно вовторой реверсивный счетчик 1 записывается "1".При выполнении задания в ЭВМ на 5 вычитающий вход соответствующегосчетчика 1 поступает сигнал, по которому содержимое счетчика уменьшается на единицу. При поступленииочередного задания на входы 3 уст-ройства оно вводится в первую из свободных ЗВМ. При поступлении заданияв последнюю из свободных ЭВМ всесчетчики 1 устанавливаются в состояние "1", а на всех вторых выходах 5 схем 3 сравнения - единичные сигналы,сигнал с выхода элемента И 10 открьгвает элемент И 11. Импульс с выходаэлемента ИЛИ 7, пройдя элементы ИЛИ9, элемент 12 задержки и элемент 2 О И 11, поступает на суммирующий входреверсивного счетчика 2 содержимоекоторого увеличится на единицу и становится равным содержимому реверсивных счетчиков 1, Очередное задание 25 через первую группу элементов И 5 .поступает в первую ЭВМ, первый реверсивный счетчик 1 устанавливаетсяв состояние "2", в результате чегоиа втором выходе схемы 3 сравнения ЗО появляется сигнал, который подготавливает поступление очередногозадания во вторую ЗВМ. Если в каждойЗВМ обрабатываются два задания, то.реверсивный счетчик 2 устанавливает ся в состояние "2" укаэанным способом. Хаким образом, устройство равномерно распределяет задания междуЭВМ в вычислительной системе.После выполнения в ЭВМ очередного 4 О задания содержимое соответствующегореверсивного счетчика 1 уменьшаетсяна единицу. Одновременно уменьшаетсяна единицу и содержимое реверсивного счетчика 2, так как с выхода 45 элемента ИЛИ 8 поступает сигнал навычитающий вход ревеосивного счетчика 2 и одновременно через элемент. ИЛИ 9 на вход элемента 12 задержки.Если содержимое реверсивного счет О чика 2 меньше содержимого всех счеччиков 1, то элемент" И 10 открыт исигнал с выхода элемента 12 задержки устанавливает реверсивный счетчик , 2 в первоначальное состояние, Еслипосле выполнения задания любой ЭВМсодержимое реверсивного счетчика ф 2равно содержимому одного из реверсивных счетчиков 1, то элемент И 11закрыт и реверсивный счетчик 2 оста1163325 куцкий . Корректор оставител ехред М.Н мборска р .С, Саек каз 4104/48 Тираж 7 О Подп ВНИИПИ Государственного комитетпо.делам изобретений и открыт .И 035,. Москва, Ж-.35, Раушская .на носСССР тент", г, Ужгород, ул. Проектн ППП фил ется в прежнем состоянии. Далее устройство работает аналогично.Если ЭВИ комплекса неисправна или выведена на профилактику, то .соответствуниций счетчик 1 достаточноц м установить в состояние 11 и задания с входа 13 устройства не поступают в данную ЭВМ, так как содержимое счетчика 1 больше содержимого счетчика 2.Таким образом, предложенное устройство обеспечивает по сравнению с известным расширение Функциональных возможностей, так как позволяет организовать работу многомашинной вычислительной системы как в однопрограммном режиме, так и в режиме мультипрограммирования. При работе в режиме мультипрограммирования предлагаемое устройство обеспечивает равномерную загрузку ЭВМ многомашинногокомплекса, что увеличивает произво- О дительность системы на 1 О.Кроме того, устройство обладаетбольшим быстродействием и более адапфетировано к изменению ччсла ЭВМ комплекса, т.е. обладает свойством расшу ряемости.

СмотретьЗаявка

3637381, 23.08.1983

ВОЙСКОВАЯ ЧАСТЬ 25840

КАТИЛОВ ВЛАДИМИР ПАВЛОВИЧ, КРЫЛОВ НИКОЛАЙ ИВАНОВИЧ, РАССОХИН ГЕННАДИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/00

Метки: вычислительной, заданий, между, многомашинной, распределения, системе, эвм

Опубликовано: 23.06.1985

Код ссылки

<a href="https://patents.su/4-1163325-ustrojjstvo-dlya-raspredeleniya-zadanijj-mezhdu-ehvm-v-mnogomashinnojj-vychislitelnojj-sisteme.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для распределения заданий между эвм в многомашинной вычислительной системе</a>

Предыдущий патент: Генератор случайных чисел

Следующий патент: Устройство для формирования диагностической информации работы программ

Случайный патент: Механическая лестница