Цифровой демодулятор многофазных фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1109939

Автор: Надточий

Текст

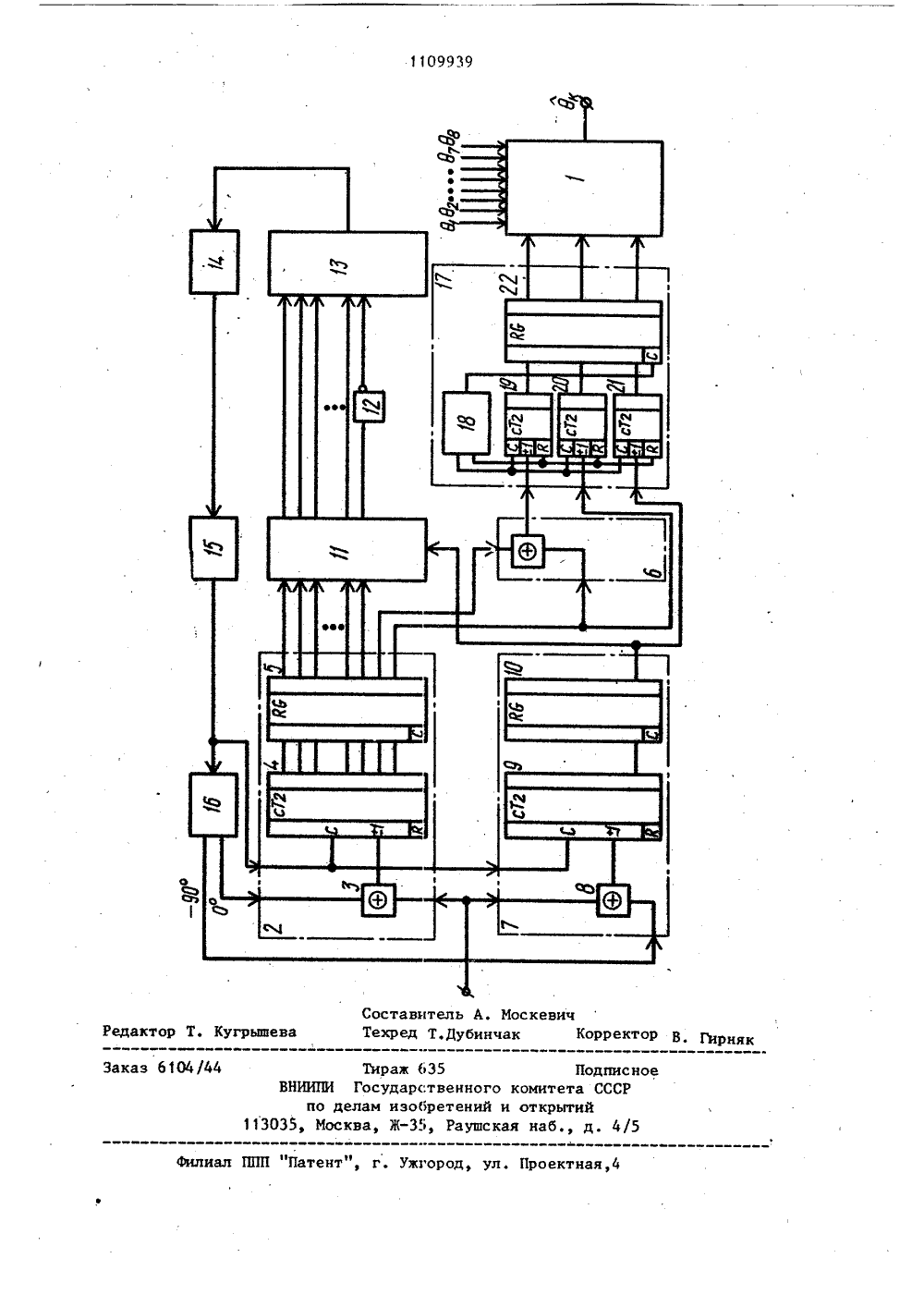

1 11 О 9Изобретение относится к техникесвязи и может использоваться всистемах передачи цифровой информации для приема Фазоманипулированныхсигналов с нестабильной частотой не 5сущей,Известен демодулятор фазоманипулированных сигналов, содержащий устройство формирования опорного колебания,состоящее из умножителя, схемы фазовой автоподстройки частоты и делителя, и схему демодуляции фазы,состоящую иэ М фазовых детекторов,Фазовращателей и решающей схемы 11,Однако данный демодулятор имеетсложную схему.Наиболее близким техническим решением к изобретению является цифровой демодулятор многофазных Фазоманипулированных сигналов, содержащий первый фазовый детектор, выходыкоторого подключены к одним входамперемножителя, другой вход и выходыкоторого соединены соответственно свыходом второго Фазового детектораи с входами цифроаналогового преобразователя, выход которого черезфильтр нижних частот подключен квходу управляемого генератора, приэтом сигнальные входы первого и второго фазовых детекторов объединены 2 .Однако известный демодуляторимеет низкую помехоустойчивость.Цель изобретения - повышение помехоустойчивости. 35Цель достигается тем, что в цифровой демодулятор многофазных фазоманипулированных сигналов, содержащий первый фазовый детектор, выходыкоторого подключены к одним входамперемножителя, другой вход и выходыкоторого соединены соответственнос выходом второго фазового детектораи с входами цифроаналогового преобразователя, выход которого черезфильтр нижних частот подключен квходу управляемого генератора, приэтом сигнальные входы первого и второго фазовых детекторов объединены,введены инвертор, блок сумматоров Я 1по модулю два, блок поразрядного накопления, дешифратор и делитель частоты, выходы которого подключены копорным входам перврго и второгоФазовых детекторов, счетные входы Бкоторых соединены с выходом управляемого генератора и с входом делителячастоты, причем соответствующие .вы 9392ходы первого фазового детектора подключены к входам блока сумматоров по модулю два, выход которого соединен с одним входом блока поразрядного накопления, к другим входам которого подключены соответствующий выход первого фазового детектора и выход второго Фазового детектора, выходы блока поразрядного накопления соединены с входами дешнфратора, а дополнительный выход перемножителя через инвертор подключен к дополнительному входу цифроаналогового преобразователя,На чертеже представлена структурная электрическая схема предложенного демодулятора.Цифровой демодулятор многофазныхфазоманипулированных сигналов содержит дешифратор. 1, первый фазовый детектор 2, состоящий из сумматора 3 по модулю два, реверсивного счетчика 4 и регистра 5, блок 6 сумматоров по модулю два, второй фазовый детектор 7, состоящий иэ сумматора 8 по модулю два, реверсивного счетчика 9 и регистра 10, перемножитель 11, инвертор 12, цифроаналоговый преобразователь 13, фильтр 14 нижних частот, управляемый генератор 15, делитель 16 частоты, блок 17 поразрядного накопления, состоящий иэ блока18 символьной синхронизации, трехреверсивных счетчиков 19-21 и регистра 22.Устройство работает следующимобразом,Во время действия импульса записичисло, соответствующее значению характеристики первого фазового детектора 2,переписывается из реверсивного счетчика 4. в регистр 5, Послеэтого реверсивный счетчик 4 устанавливается в нулевое состояние поддействием обнуляющего импульса. Затем осуществляется новьй цикл счета,в конце которого информция о фазовомрассогласовании, поступающая черезсумматор 3, снова переписывается врегистр 5.В результате перемножения в перемножителе 11 всех (ш+1) разрядовпервого фазового детектора 2 с однимзнаковым разрядом второго фазовогодетектора 7 на выходе цифроаналогового преобразователя 13 формируетсяпилообразная характеристика с периодом л (инвертор 12 при этом исключен), Отбрасывание старшего (в+1)-го30 3 11099 разряда первого фазового детектора 2 и использование в качестве знакового ш-го разряда вызывает уменьшение в два раза максимально возможного числа на выходе первого фазового де 5 тектора 2. Это приводит к формирова. нию на выходе цифроаналогового преобразователя 13 пилообразной характеристики с периодом 4 /2. Подключе ние инвертора 12 смещает характерис тику по фазе на половину ее периода. Этот процесс формирования может быть продолжен и дальше. Исключение ш-го разряда и использование (ш)-го в качестве старшего сформирует на выходе цифроаналогового преобразователя 13 характеристику с периодом М/4. Второй фазовый детектор 7, состоящий из сумматора 8 по модулю два, реверсивного счетчика 9 и регистра 10, работает аналогично первому фазовому детектору 2. Аналогично может быть получена результирующая пилообразная характеристика с произвольным периодом 2 Т(/2";где и = 2, 3При этом осуществляется разбиение оси разности фаз на области монотонности результирующей характеристики, причем каждой области поставлено в соответствие двоичное число, сформированное на выходе блока 6 сумматоров по модулю два.Причем в качестве двух старших разрядов числа используются .выходные сигналы знаковых разрядов первого и второго35 фазовых детекторов 2 и 7. Особенность такого кодирования заключается в том, что числа, соответствующие соседним фазовым областям, имеют отличия только в одном двоичном разряде. Области, расположенные через одну, имеют отличия в двух разрядах демодулированного числа. Указанные свойства позволяют вместо вычисления среднего значения передаваемой фазы (изменяющейся под действием шума на входе) усреднять значения отдельных двоичных разрядов трехзначного числа на выходе блока 6.После установки в "0" импульсом с выхода блока 18 символьной синхронизации блока 17 поразрядного накопления реверсивные счетчики 19-21 начинают подсчет тактовых импульсов. При этом выходные сигналы блока 6 сумматоров по модулю два и знаковых разрядов обоих фазовых детекторов 2 и 7 управляют направлением счета этих реверсивных счетчиков. В конце интервала накопления значения знаковых разрядов реверсивных счетчиков 19-21 переписываются в регистр 22 при помощи импульса, также вырабатываемого блоком 18. Вслед за этим все реверсивные счетчики 19-21 устанавливаются в "0", и процесс накопления начинается сначала. Дешифратор 1 при помощи ключей реализует однол значное соответствие оценки О передаваемой фазы демодулированному числу на выходе блока 17. Так, на- примерпри действии на входе комбинации 101 на выходе дешифратора 1 формируется напряжение соответствующее значению оценки О к - У /8, 000 соответствует оценке Ь = 13 Л /8 и т.д.При этом сигнал с пилообразной характеристикой с выхода цифроаналогового преобразователя 13 поступает на вход фильтра 14 нижних частот и далее управляет работой управляемого генератора 15. Сигнал с выхода управляемого генератора ,15 через делитель 16 частоты поступает на опорные входы первого и второго фазовых детекторов 2 й 7. Таким образом, использование предложенного цифрового демодулятора позволяет улучшить по сравнению с известным помехоустойчивость системы связи с фазомодулированным сигналом.1109939 Составитель А. МоскевичТехред Т,Дубинчак Корректор В няк ктор Т, Кугрышева Заказ 6104 Тираж 635ИИПИ Государственного делам изобретенийМосква, Ж, Раушс одписное СССР В о комите открытий я наб., д.

СмотретьЗаявка

3434574, 07.05.1982

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

НАДТОЧИЙ АНАТОЛИЙ АРХИПОВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, многофазных, сигналов, фазоманипулированных, цифровой

Опубликовано: 23.08.1984

Код ссылки

<a href="https://patents.su/4-1109939-cifrovojj-demodulyator-mnogofaznykh-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор многофазных фазоманипулированных сигналов</a>

Предыдущий патент: Устройство восстановления опорного когерентного сигнала

Следующий патент: Устройство для адаптивного приема дискретных сигналов

Случайный патент: Композиция для гидроизоляции строительных конструкций