Преобразователь синусно-косинусных сигналов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

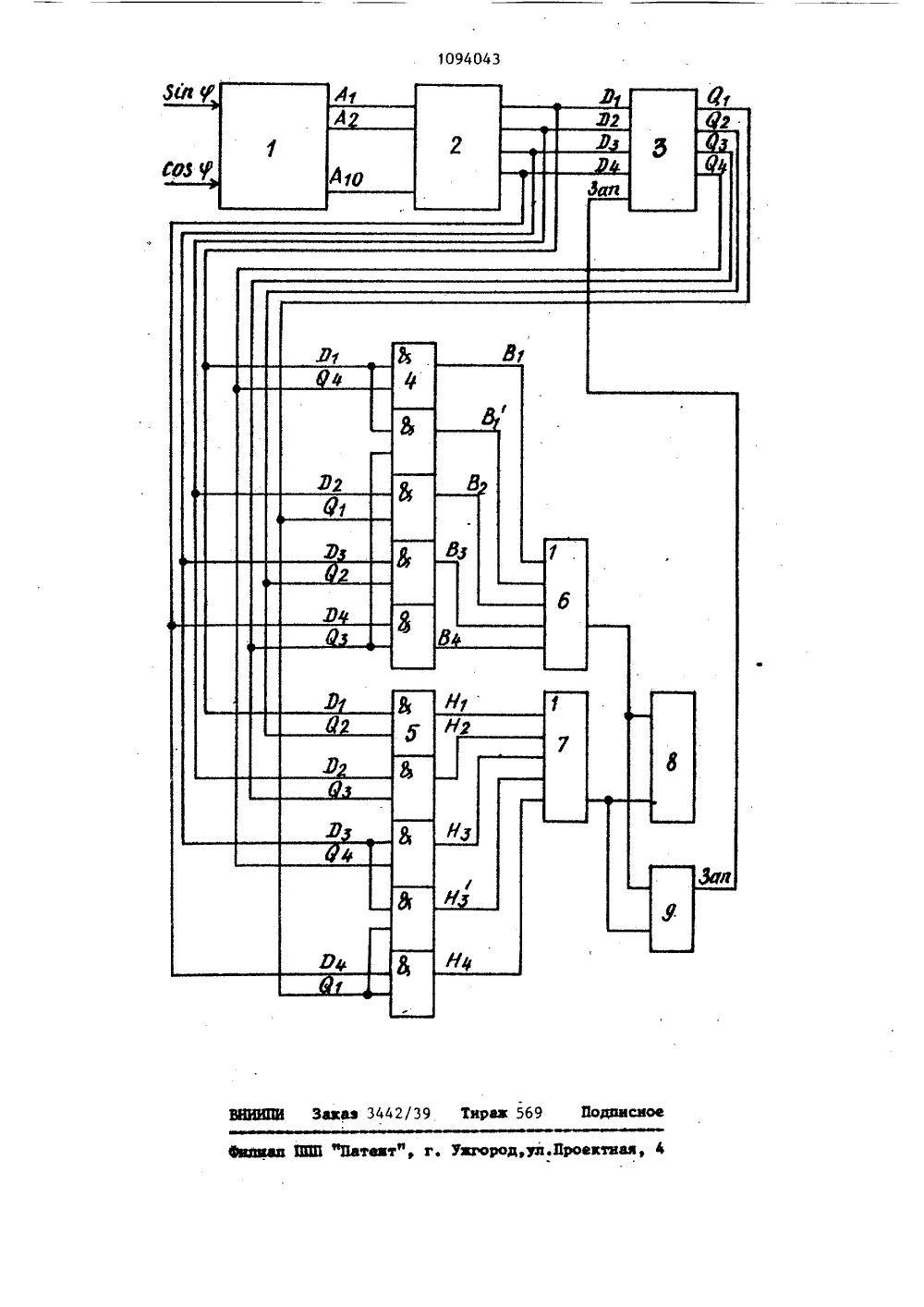

,Н. и др, Иу ки положения "Машинострое ние", СССР77.9.идетельс С 9/00.СИНУСНОД, содержа- синусно-ко- офазные ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) 1. Преснухинвые растровые датчих применение. И.1969, с. 71, рис.2, Авторское свВ 674069, кл. С 08(54)(57) ПРЕОБРАЗОВАТЕЛКОСИНУСНЫХ СИГНАЛОВ В щий блок преобразовани синусных сигналов в мн сигналы, выходы которого через дешиф-"ратор подключены к одним входампервого и второго блока элементов И,выходы которых соответственно черезпервый и второй элементы ИЛИ подключены к входам сложения и вычитанияреверсивного счетчика, о т л и ч аю щ и й с я тем, что, с целью упрощения преобразователя, в него введеныформирователь импульсов и регистр,информационные входы регистра соединены с выходами дешифратора, а выходыподключены к другим входам первогои второго блока элементов И, выходыпервого и второго элементов ИЛИ подключены к формирователю импульсов,выход которого подключен к управляющему входу регистра.. ключен к управляющему входу регистИзобретение относится к автоматике и вычислительной технике и можетбыть использовано для связи аналого.,вых источников информации с цифровымвычислительным устройством 5Известны преобразователи синусно"косинусных сигналов в код, содержащиеблок формирователей двухфазных прямоугольных сигналов, выходы которого подключены непосредственно к одним входам первого и второго блокаэлементов И, а через блок дифференцирующих элементов - к другим входампервого и второго блока элементов И,)выходы которых соответственно через 15первый и второй лементы ИЛИ подключены к входам сложения и вычитанияреверсивного счетчика .13 .Недостатком преобразователей является разрешающая способность и слож /ность выполнения преобразователегна интегральных элементах, вызваннаяналичием дифференцирующих элементов.Наиболее близким к изобретениюявляется преобразователь синуснокосинусных сигналов в код, содержащий блок преобразования синусио-косинусных сигналов в многофазные сигналы,выходы которого через дешифратор, подключены к одним входам первогои второго блока .элементов И, выходыкоторых соответственно через первыйи второй элементы ИЛИ подключены квходам сложения и вычитания реверсивного счетчика, а выходы дешифратора 35через блок двфференцирующих элементов - к другим входам первого и второго блока элементов И Г 23,Недостатком известного преобразователя является сложность его выполне 40ния на интегральных элементах, вызванная наличием дифференцирующихэлементов.Цель изобретения - упрощение преобразователя. . 45 Поставленная цель достигается тем, что в преобразователь синуснокосинусных сигналов в код, содержащий блок преобразования синусно-косинус 50 ных сигналов в многофазные сигналы, выходы которого через дешифратор подключены к одним входам первого и второго блока элементов И, выходы которых соответственно через первый55 и второй элементы ИЛИ подключены к входам сложения и вычитания реверсивного счетчика, введены формирова-тель импульсов,и регистр, информационные входы регистра соединены с выходами дешифратора, а выходы подключе-ны к другим входам первого и. второго блока элементов И, выходы первого и второго элементов ИЛИ подключены к формирователю импульсов, выход которого. подключен к управляющему входу регистра.На чертеже представлена структурная схема преобразователя.Преобразователь содержит последовательно соединеннйе блок 1 преобразования синусно-косинусных сигналов в многофазные сигналы, дешифратор 2 и регистр 3, выходы дешифратора 2 и регистра 3 подключены соответственно к одним и другим входам первого 4 ивторого 5 блоков элементов И, выходыкоторых соответственно через первый 6и второй 7 элементы ИЛИ подключены к входам сложения и вычитания реверсивного счетчика 8, выходы элементовб и 7 подключены к входам формирователя 9 импульсов, выход которого подра ЗеПреобразователь работает следующим образом.В блоке 1 входные синусно-косинусные сигналы преобразуются в прямоугольные миогофазные сигналы, числокоторых определяется принятой дискретностью преобразователя. В дешифраторе2 многофазные сигналы преобразуютсяв последовательности неперекрывающихся импульсов, которые поступают на. вхрды блоков 4 и 5 элементов И и на информационные входы регистра 3,В любой момент времени сигнал на выходе дешифратора представляет собой "1" иа одном из выходов и "0" на всех остальных выходах. По сигналу с формирователя 9 состояние дешифратора 2 запоминается в регистре 3. Коды дешифратвра 2 и регистра 3 сравниваютея в блоках 4 и 5. При равенстве выходных кодов дешифратора 2 и регистра 3 все выходы блоков 4 и 5 находятся в нулевом состоянии. При изменении входной величины в одну сторону выходной код дешифратора 2 последовательно принимает значения, например, 1000, 0100, 0010 и т.д . При каждом изменении выходного кода дешифратора 2 происходит совпадение на одном из элементов И блока 4 еди-о ницы кода предыдущего значения с регистра 3 с единицей кода текущегозначения с дешифратора 2. Единичный сигнал с выхода блока 4 через элемент ИЛИ 6 проходит на вход сложения) реверсивного счетчика 7 и через формирователь 9, представляющий собой элемент ИЛИ и элемент задержки, поступает на управляющий вход регистра 3. По сигналу с формирователя 9. в регистре 3 происходит перезапись выходного кода дешифратора 2, после чего выходные коды дешифратора 2 и регистра 3 становятся равными. Выходы, блока 4 возвращаются в нулевое состояние до следующего изменения входной величины в ту же сторону,.При изменении входной величины в другую сторону выходной код дешифратора принимает значения, например, 1000, 0001, 0010, 0100 и т.д. При каждом изменении выходного кода дешифратора 2 происходит совпадение на одном из элементов И блока 5 единицы кода предыдущего значения с регистра 3 с единицей кода текущего значения с дешифратора 2, Единичныйсигнап с выхода блока 5 через элемент ИЛИ 7 проходит на вход вычитания реверсивного счетчика 8 и через Формирователь 9 на управляющий вход регистра 3 для перезаписи выходного кода дешифратора 2. Выходы блока 5 возвращаются в нулевое состояние до следующего изменения входной величины. Выходной код преобразователя Формируется в реверсивном счетчике 8.В предлагаемом преобразователе отсутствуют дифференцирующие элементы, что позволяет упростить преобразователь при выполнении его на ин.;тегральных элементах.

СмотретьЗаявка

3520150, 07.12.1982

ПРЕДПРИЯТИЕ ПЯ Р-6495

БАБЕР АЛЕКСАНДР ИОСИФОВИЧ, МИХАЛЕВ АЛЕКСАНДР ИВАНОВИЧ, СПАСОЕВИЧ ЛЕОНИД БОРИСОВИЧ

МПК / Метки

МПК: G08C 9/00

Метки: код, сигналов, синусно-косинусных

Опубликовано: 23.05.1984

Код ссылки

<a href="https://patents.su/4-1094043-preobrazovatel-sinusno-kosinusnykh-signalov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь синусно-косинусных сигналов в код</a>

Предыдущий патент: Устройство для контроля изменения положения объекта

Следующий патент: Устройство для измерения перемещений

Случайный патент: Устройство для стопорения болтового соединения