Цифровой демодулятор частотно-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

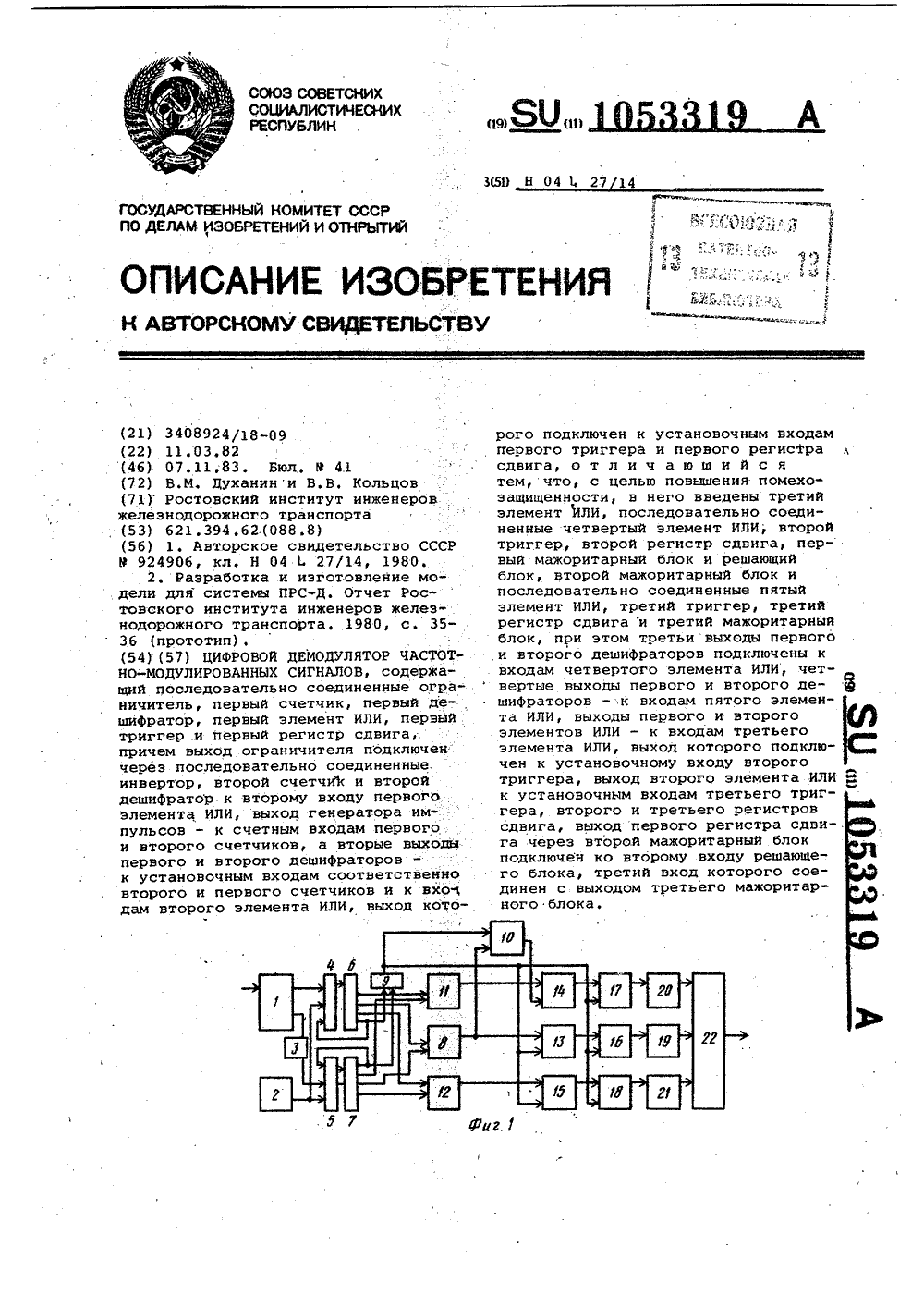

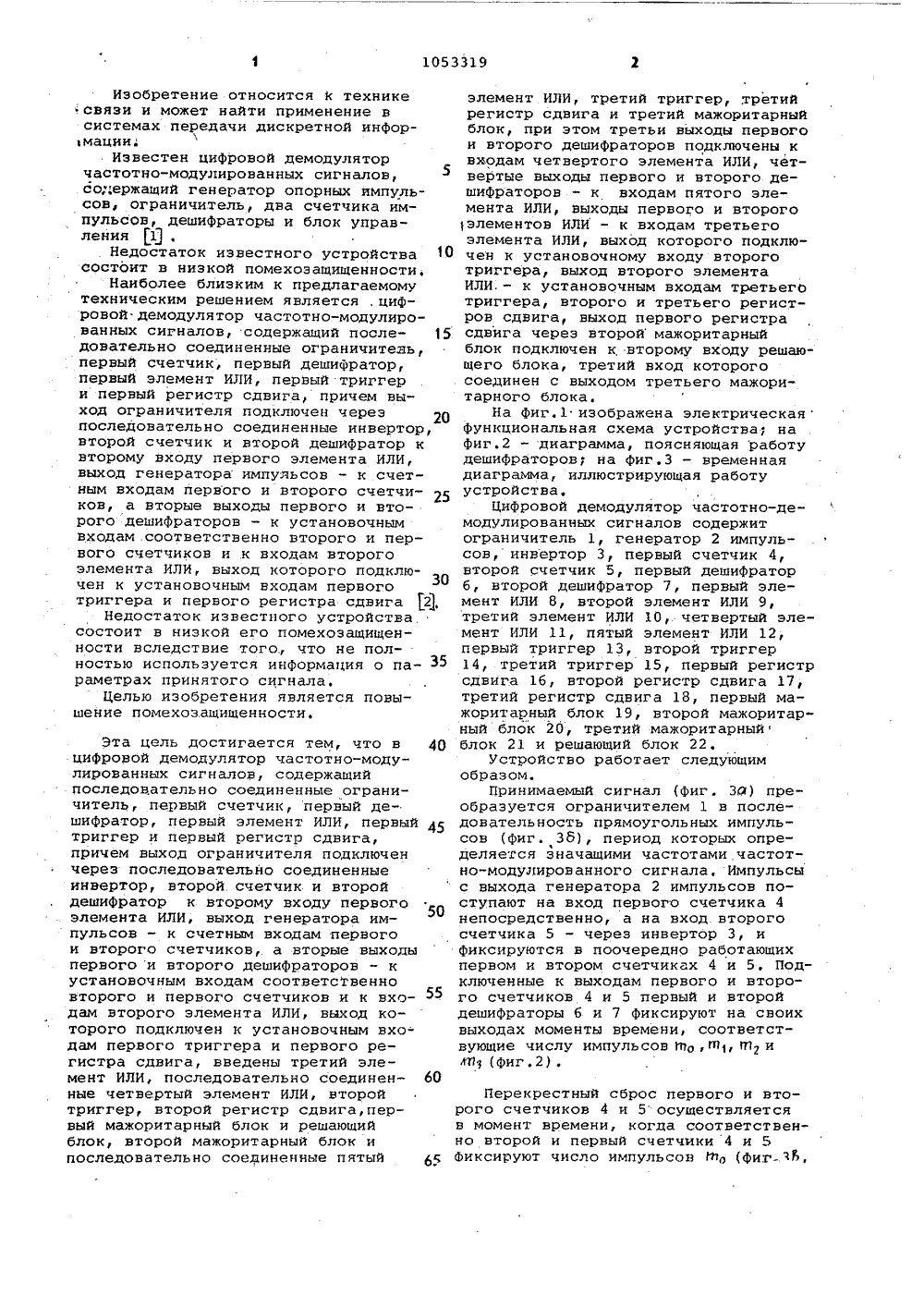

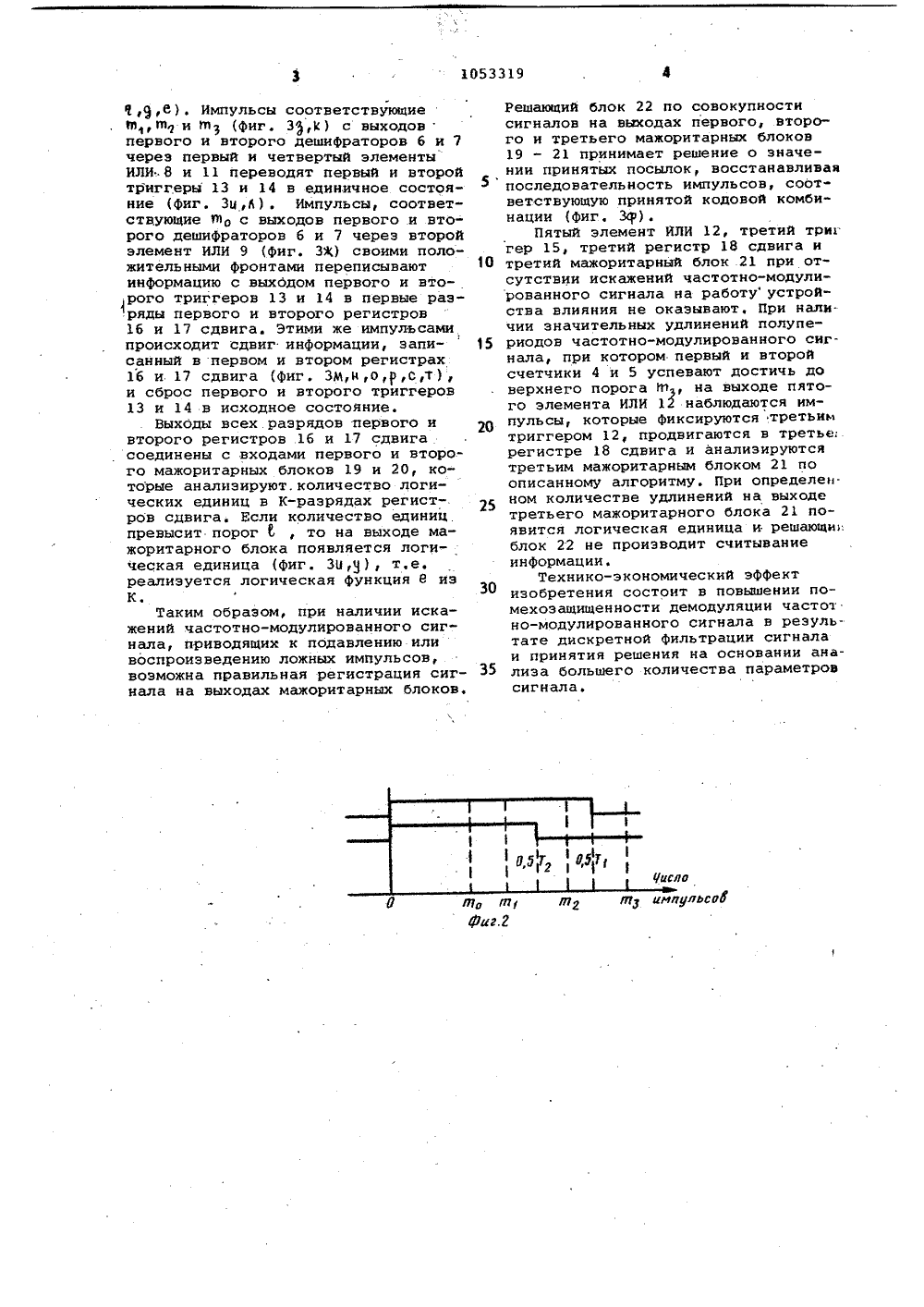

(191 (11 3(50 Н 04 1, 27 14 ОПИСАНИЕ ИЗОБРЕТЕНИК АВТОРСКОМУ СВИДЕГЕЛЬСТВУ ГосудАРстэенный Комитет сссРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(46) 07.11,83. Бюл. В 4.1 (72) В,М, Духанини В.В. Кольцов (71) Ростовский институт инженеров железнодорожного транспорта (53) 621.394.62(088,8)(56) 1. Авторское свидетельство СССР В 924906 кл, Н 04 Ь 27/14, 1980.2. Разработка и изготовление модели для системы ПРС-Д. Отчет Ростовского института инженеров желез- . нодорожного транспорта. 1980, с. 35- 36 (прототип).(54)(57) ЦИФРОВОЙ ДЕМОДУЛЯТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ, содержащий последовательно соединенные ограничитель, первый счетчик, первый дешифратор, первый элемент ИЛИ, первый триггер и первый регистр сдвига, причем выход ограничителя подключен. через последовательно соединенные. инвертор, второй счетчи 1 и второй дешифратор к второму входу первого элемента ИЛИ, выход генератора импульсов - к счетным входам первого и второго. счетчиков, а вторые выходы первого и второго дешифраторов к установочным входам соответственно второго и первого счетчиков и к вхо- дам второго элемента ИЛИ, выход которого подключен к установочным входам первого триггера и первого регистра сдвига, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоэащищенности, в него введены третий элемент ИЛИ, последовательно соединенные четвертый элемент ИЛИ; второй триггер, второй регистр сдвига, пер" вый мажоритарный блок и решающий блок, второй мажоритарный блок и последовательно соединенные пятый элемент ИЛИ, третий триггер, третий регистр сдвига и третий мажоритарный блок, при этом третьи выходы первого и второго дешифраторов подключены к входам четвертого элемента ИЛИ, четвертые выходы первого и второго де- Я шифраторов - к входам пятого элемента ИЛИ, выходы первого и второго элементов ИЛИ - к входам третьего элемента ИЛИ, выход которого подключен к установочному входу второгоФф триггера, выход второго элемента ИЛИ к установочным входам третьего триггера, второго и третьего регистров сдвига, выход первого регистра сдви-. га через второй мажоритарный блок подключен ко второму входу решающего блока, третий вход которого соединен с выходом третьего мажоритарного блока,Изобретение относится К техникесвязи и может найти применение всистемах передачи дискретной информации;Известен цифровой демодуляторчастотно-модулированных сигналов,соержащий генератор опорных импульсов, ограничитель, два счетчика импульсов, дешифраторы и блок управления (1) .Недостаток известного устройствасостоит в низкой помехозащищенности,Наиболее близким к предлагаемомутехническим решением является . цифровой демодулятор частотно-модулированных сигналов, содержащий последовательно соединенные ограничитель,первый счетчик, первый дешифратор,первый элемент ИЛИ, первый триггери первый регистр сдвига, причем выход ограничителя подключен черезпоследовательно соединенные инвертор,второй счетчик и второй дешифратор квторому входу первого элемента ИЛИ,выход генератора импульсов - к счетным входам первого и второго счетчиков, а вторые выходы первого и второго дешифраторов - к установочнымвходам соответственно второго и первого счетчиков и к входам второгоэлемента ИЛИ, выход которого подключен к установочным входам первоготриггера и первого регистра сдвига (2,Недостаток известного устройствасостоит в низкой его помехозащищенности вследствие того, что не полностью используется информация о па- З 5раметрах принятого сигнала,Целью изобретения является повышение помехозащищенности. Эта цель достигается тем, что в 49 цифровой демодулятор частотно-модулированных сигналов, содержащий последовательно соединенные ограничитель, первый счетчик, первый дешифратор, первый элемент ИЛИ, первый 45 триггер и первый регистр сдвига, причем выход ограничителя подключен через последовательно соединенные инвертор, второй счетчик и второй дешифратор к второму входу первого элемента ИЛИ, выход генератора им пульсов - к счетным входам первого и второго счетчиков,. а вторые выходы первого и второго дешифраторов - к установочным входам соответственно второго и первого счетчиков и к входам второго элемента ИЛИ, выход которого подключен к установочным входам первого триггера и первого регистра сдвига, введены третий элемент ИЛИ, последовательно соединен ные четвертый элемент ИЛИ, второй триггер, второй регистр сдвига,первый мажоритарный блок и решающий блок, второй мажоритарный блок и последовательно соединенные пятый у элемент ИЛИ, третий триггер, третийрегистр сдвига и третий мажоритарныйблок, при этом третьи выходы первогои второго дешифраторов подключены квходам четвертого элемента ИЛИ, четвертые выходы первого и второго дешифраторов - к входам пятого элемента ИЛИ, выходы первого и второго(элементов ИЛИ - к входам третьегоэлемента ИЛИ, выход которого подключен к установочному входу второготриггера, выход второго элементаИЛИ. - к установочным входам третьеготриггера, второго и третьего регистров сдвига, выход первого регистрасдвига через второймажоритарныйблок подключен к, второму входу решающего блока, третий вход которогосоединен с выходом третьего мажоритарного блока.На фиг.1 изображена электрическаяфункциональная схема устройства, нафиг.2 - диаграмма, поясняющая работудешифраторов; на фиг.З - временнаядиаграмма, иллюстрирующая работуустройства,Цифровой демодулятор частотно-демодулированных сигналов содержитограничитель 1, генератор 2 импульсов, инвертор 3, первый счетчик 4,второй счетчик Б, первый дешифратор6, второй дешифратор 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9,третий элемент ИЛИ 10,.четвертый элемент ИЛИ 11, пятый элемент ИЛИ 12,первый триггер 13, второй триггер14, третий триггер 15, первый регистрсдвига 16, второй регистр сдвига 17,третий регистр сдвига 18, первый мажоритарный блок 19, второй мажоритарный блок 20, третий мажоритарныйблок 21 и решающий блок 22.Устройство работает следующимобразом,Принимаемый сигнал (фиг. ЗР) преобразуется ограничителем 1 в последовательность прямоугольных импульсов (фиг. 35), период которых определяется значащими частотами частотно-модулированного сигнала, Импульсыс выхода генератора 2 импульсов поступают на вход первого счетчика 4непосредственно, а на вход второгосчетчика 5 - через инвертор 3, ификсируются в поочередно работающихпервом и втором счетчиках 4 и 5, Подключенные к выходам первого и второго счетчиков 4 и 5 первый и второйдешифраторы 6 и 7 фиксируют на своихвыходах моменты времени, соответствующие числу импульсов ВоГоббс п 7 икп (фиг,2),Перекрестный сброс первого и второго счетчиков 4 и 5 осуществляется в момент времени, когда соответственно второй и первый счетчики 4 и 5 Фиксируют число импульсов (по (фиг1053319 ооимпульс оФ щ тФиг.Г 96). Импульсы соответствующие п е и п 3 (Фиг. 3),М) с выходов первого и второго дешифраторов б и 7 через первый и четвертый элементы ИЛИ" 8 и 11 переводят первый и второй триггеры 13 и 14 в единичное состояние (Фиг, Зи,Ь) . Импульсы, соответствующие Во с выходов первого и вто" рого дешифраторов 6 и 7 через второй элемент ИЛИ 9 (Фиг. 3 своими положительными фронтами переписывают информацию с выходом первого и второго триггеров 13 и 14 в первые разряды первого и второго регистров 16 и 17 сдвига. Этими же импульсами происходит сдвиг информации, записанный в нервом и втором регистрах 16 и 17 сдвига (фиг . ЗМ,н,ОС,Т )и сброс первого и второго триггеров 13 и 14 в исходное состояние.Выходы всех разрядов первого и второго регистров 16 и 17 сдвига соединены с входами первого и второго мажоритарных блоков 19 и 20, которые анализируют.количество логических единиц в К-разрядах регистров сдвига, Если количество единиц превысит порог 1 , то на выходе мажоритарного блока появляется логическая единица (фиг, ЗО,), т,е. реализуется логическая функция 6 из К.Таким образом, при наличии искажений частотно-модулированного сигнала, приводящим к подавлению или воспроизведению ложных импульсов, возможна правильная регистрация сигнала на выходах мажоритарных блоков,Решающий блок 22 по совокупностисигналов на выходах первого, второго и третьего мажоритарных блоков19 - 21 принимает решение о значении принятых посылок, восстанавливаяпоследовательность импульсов, соответствующую принятой кодовой комбинации (фиг. Зф).Пятый элемент ИЛИ 12, третий трмггер 15, третий регистр 18 сдвига и 10 третий мажоритарный блок 21 при отсутствии искажений частотно-модулированного сигнала на работу устройства влияния не оказывают, При наличии значительных удлинений полупе риодов частотно-модулированного сигнала, при котором первый и второйсчетчики 4 и 5 успевают достичь доверхнего порога Ф, на выходе пятого элемента ИЛИ 12 наблюдаются импульсы, которые фиксируются третьимтриггером 12, продвигаются в третье:регистре 18 сдвига и анализируютсятретьим мажоритарным блоком 21 поописанному алгоритму. При определен.ном количестве удлинений на выходетретьего мажоритарного блока 21 появится логическая единица и решающи,.блок 22 не производит считываниеинформации,Технико-экономический эффектизобретения состоит в повышении помехозащищенности демодуляции частот.но-модулированного сигнала в результате дискретной фильтрации сигналаи принятия решения на основании ана лиза большего количества параметровсигнала.1053319 Составитель О, АндрушкоРогулич Техред Т.Маточка Корректор А, Тяс акт Заказ 8903/5 7 н ам и 1303 илиал ППППатентфг. Ужгород, ул. Проектная, 4 Тираж НИИПИ Госуда по дел 5, МоскваПодпио комитета СССРй и,открытийская наб., д, 4 твеннобретен5, Рауш

СмотретьЗаявка

3408924, 11.03.1982

РОСТОВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

ДУХАНИН ВИКТОР МИХАЙЛОВИЧ, КОЛЬЦОВ ВАСИЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/14

Метки: демодулятор, сигналов, цифровой, частотно-модулированных

Опубликовано: 07.11.1983

Код ссылки

<a href="https://patents.su/4-1053319-cifrovojj-demodulyator-chastotno-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор частотно-модулированных сигналов</a>

Предыдущий патент: Устройство приема частотно-манипулированных сигналов

Следующий патент: Фазовый манипулятор

Случайный патент: Установочное приспособление к прибору для свинчивания и развинчивания рельсовых стыковых скреплений