Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

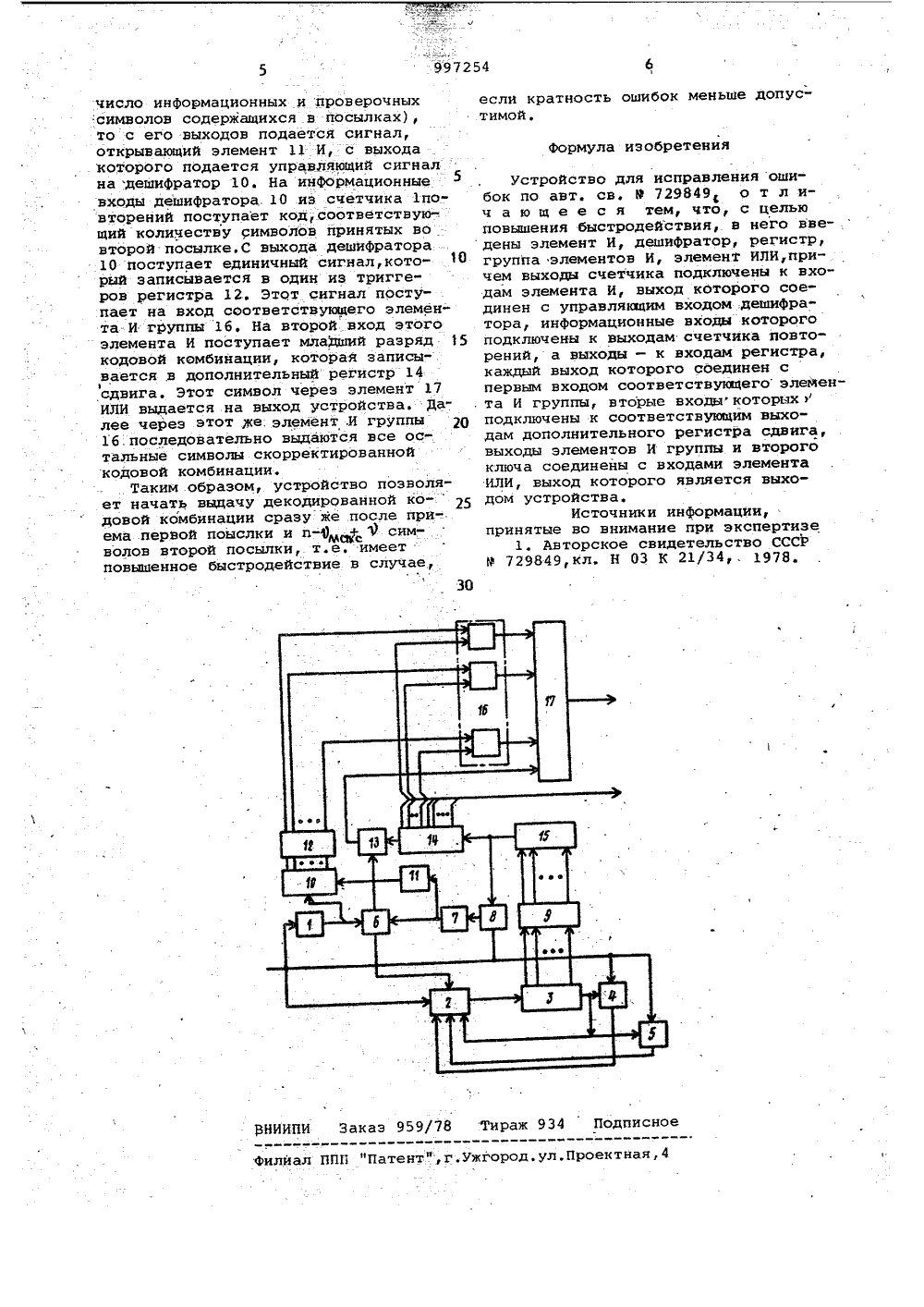

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз СсеетскихСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 150781 (21) 3317285/18-21 Р 1 М Кз Н 03 К 21/34 с присоединением заявки М 9 Государственный комитет СССР по делам изобретений н открытий(088,8) Дата опубликования описания 150283(72) Авторыизобретения А.М.Заяц и В.Н.Горшков 1 Заявитель 4) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК 2 Изобретение относится к технике .связи и вычислительной технике и может использоваться в системах передачи и хранения информации, подверженных воздействию помех.По основному авт. св. Р 729849 известно устройство для исправления ошибок, содержащее счетчик повторений, .выход которого соединен с входом коммутатора,. а вход.с входами первого и второго сумматоров и управляющего ключа, другие входы которого соединены с. выходами первого и второго ФуМИторов регистра сдвига и коммутатора, а выход - с входом регистра сдвига, сумматора декодера, входы которого соединены с выходами регистра сдвига, а выходы - с входами мажоритарного элемента, выход которого соединен с входом ключа, другой вход которого соединен с выходом коммутатора, дополнительного регистра сдвига, включенного меяду входом второго ключа и выходом мажо,ритарногоэлемента, очетчик ошибок .и элемент сравнения, первый вход которого подключен к входной шине,второй вход. - к выходу мажоритарного элемента, а выход через счетчик ошибок - к одному из входов,коммуматора Декодирование кодовой комбинации в устройстве происходит следующим образом: если кратность ошибок в принимаемых посылках более чем 1) ( максимальная кратность ошибок, Исп. равляемой корректирующим кодом), то для .декодирования кодовой комбинации необходимо три посылкиеслиФ 1)межс то для декодирования и исправления ошибок необходимо не менее двух посылок информации 11).Недостатком известного устройства является его низкое быстродействие.Цель изобретения - повьвение быстродействия устройства.Цель достигается тем, что в устройство для исправления ошибок, со" держащее счетчик повторений., коммутатор, ключ, регистр сдвига, счетчик и элемент сравнения, введены элементы И, дешифратор регистр, вруппа элементов И и элемент ИЛИ причем выходы счетчика подключены ко входам элемента И, выход которого соединен с управляющим входом дешифратора, информационные входы которого подключены к выходам счетчика повторений, а выходы ко входам регистра, каждый выход которого соединен с первымвходом. соответствующего элемента И группы, вторые входы кс)торых подключены к соответствующим выходам допол нительного регистра сдвига, выходы элементон И группы и второго ключа соединены со нходами элемента ИЛИ, выход которого является выходом устройства для исправления ошибок.На чертеже представлена структурная схема устройства для исправлений ошибок, 10Устройство содержит счетчик 1 повторений,. вход которого соединен со входом удтройстна, первый ключ 2, регистр 3 сдвига, сумматоры 4 и 5, коммутатор б, счетчик 7, элемент 8 сравнения, сумматоры 9 декодера, дешиФратор 10, элемент 11 И, регистр 12, второй ключ 13, дополнительный регистр 14 сдвига, мажоритарный эле" мент 15, группа элементов 16 И, элемент 17 ИЛИ.Выходы счетчика 1 повторений соединень. с входами коммутатора б и с инФормационными входами дешифратора 10. Входы первого ключа 2 соединены с входами устройства, выходами суммато рон 4 и 5 и выходами коммутатора б. Выход первого ключа соединен с входом регистра 3 сдвига, выходы которого подключены ко входам сумматора 9 декодера и сумматоров 4 и 5,.входы которых соединены с входом устройства. Другой вход коммутатора б соединен с выходом счетчика 7, который подключен ко входу элемента 11 И. Другой выход коммутатора б соединен .со входом вто рого ключа 13. Вход счетчика 7 соединен с элементом 8 сравнения,один вход которого соединен с входом устройства а другой.с выходом мажоритарного элемента 15, нходы которого подключены 40 к выходам сумматора-декодера 9. Выход мажоритарного элемента 15 соединен со входом дополнительного регистра 14 сдвига.Управляющий вход дешиФратора 10 соединен с выходом элемента 11 И, вы-, ходы дешифратора соединены с входами регистра 12, ныходы которого соедине-. ны с первыми входами соответствующих элементов И группы 16. Выход второго ключа 13 соединен с входом элемента 17 ИЛИ, а вход второго ключа 13 подключен к выходу дополнительного регистра 14 сдвига, младшие 1) разрядных выходов которого соединены со вторыми входами Элементов И грущу 16.Выходы элементов И группы 16 под. /ключены ко входам элемента 17 ИЛИ, выходы которого являются выходами устройства для исправления ошибок,Устройство работает следующим об разом,При приеме первой посылки сигнал с коммутатора б ставит первый ключ 2 н положение, при котором на вход регистра 3 сдвига проходят принимаемые символы.По окончании приема первой посылки (кодовой комбинации)сигнал со счетчика 1 повторений поступает на коммутатор, б,выходной сигналс которого ставит первый ключ 2 в положение, при котором на вход регистра 3 сдвига проходят сигналы с первого сумматора;4, работающего поправилу 1+1:1 у О+ОаОр 1+0,2 а 2,0+1-2,Счетчик 7 устанавливается в нулевоесостояние, При приеме. второй посылкиодновременно производится исправлениеошибок н. первой посылке с помощью сумматоров 9 декодера и мажоритарного элемента 15.,Каждый символ второй посылкисравнивается в элементе 8 сравненияс соответствующим символом скорректированной первой посылки, которая:записывается в дополнительный регистр 14 сдвига, При совпадении символов первый и второй посылок элемент 8 сравнения выдает единичныйсигнал, по которому счетчик 7 увеличивает свое состояние на единицу приэтом целесообразно рассмотреть двахарактерных случая: в первой иливторой посылках кратность ошибок19, о, нпервой или второй посылкахкратность ошибок 4)маКсВ первом случае вторая и скорректированная первая посылки отличаютсябольше, чем на 9 М символов О наличии ошибок, кратность больше снимсжсдетельстнует состояние счетчика 7.По окончании приема второй посылкисигналы со счетчика 1 повторений исчетчика 7 поступают на коммутаторб, сигнал с которого ставит первыйключ 2 в положение, при котором навход регистра 3 сдвига проходятсигналы с выхода второго сумматора,5, работающего по правилу: 1+11",О+О Оу 1+Ов 1 у О+1:Ор 2+1 в 1 р 2+О:О,где первыми записаны символы поступающие из регистра 3 сдвига. Одновременно с приемом третьей посылкипроизводится исправление ошибок спомощью сумматоров 9 декодера и мажоритарного, элемента 15 и записьисправленной кодовой комбинации вдополнительный регистр 14.По окончании приема третьей посылки сйгнал со счетчика 1 повторений поступает на коммутатор б, который открывает второй ключ 13 иисправленная кодовая комбинация пос.ледовательным кодом выдается черезэлемент 17 ИЛИ на выход устройствадля исправления ошибок. Кроме того,возможна выдача исправленной кодовойкомбинации параллельным кодом. В другом случае вторая и скорректированнаяпервая посылки отличаются не больше,чем на 0 символов, либо сонпадают.Когда в счетчике 7 будет записано:символов содержащихся .в йосылках),то с его выходов подается сигнал,открывающий элемент 11- И, с выходакоторого подается управляющий сигнална дешифратор 10. На информационныевходы дешифратора 10 из счетчика 1 повторений поступает код,соответствую-.щий количеству символов принятых вовторой посылке.С выхода дешифратора10 поступает единичный сигнал, который записывается в один из триггеров регистра 12. Этот сигнал поступает на вход соответствукщего элемента И группы 1 б. На второй вход этогоэлемента И поступает младший разряд 15кодовой комбинации, которая записывается в дополнительный регистр 14сдвига. Этот символ через элемент 17ИЛИ выдается на выход устройства, Далее через этот же: элемент .И группы1 б.последовательно выдаются все остальные символы скорректированнойкодовой комбинации,Таким образом, устройство позволяет начать выдачу декодированной ко-довой комбинации сразу же после при-,ема первой поыслки и и- + М симМОКСволов второй посылки, т.е, имеетповышенное быстродействие в случае,если кратность ошибок меньше допустимой. Устройство для исправления ошибок по авт. св, В 729849 о т л ич а ю щ е е с я тем, что, с цельюповышения быстродействия, в него введены элемент И, дешифратор, регистр,группа элементов И, элемент ИЛИ,причем выходы счетчика подключены к входам элемента И, выход которого соединен с управляющим входом .дешифра"тора, информационные входы которогоподключены к выходам счетчика повто"рений, а выходы - к входам регистра,каждый выход которого соединен спервым входом соответствующего элемента И группы, вторые входи которыхподключены к соответствующим выходам дополнительного регистра сдвига,выходы элементов И группы и второгоключа соединены с входами элементаИЛИ, выход которого является выходом устройства,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР9 729849,кл. Н 03 К 21/34. 1978,

СмотретьЗаявка

3317285, 15.07.1981

ПУШКИНСКОЕ ВЫСШЕЕ ОРДЕНА КРАСНОЙ ЗВЕЗДЫ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ЗАЯЦ АНАТОЛИЙ МОЙСЕЕВИЧ, ГОРШКОВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 21/34

Метки: исправления, ошибок

Опубликовано: 15.02.1983

Код ссылки

<a href="https://patents.su/3-997254-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: @ -триггер с автономной проверкой работоспособности

Следующий патент: Управляемый делитель частоты

Случайный патент: Инвертор