Цифровой демодулятор частотно-манипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 987842

Автор: Родькин

Текст

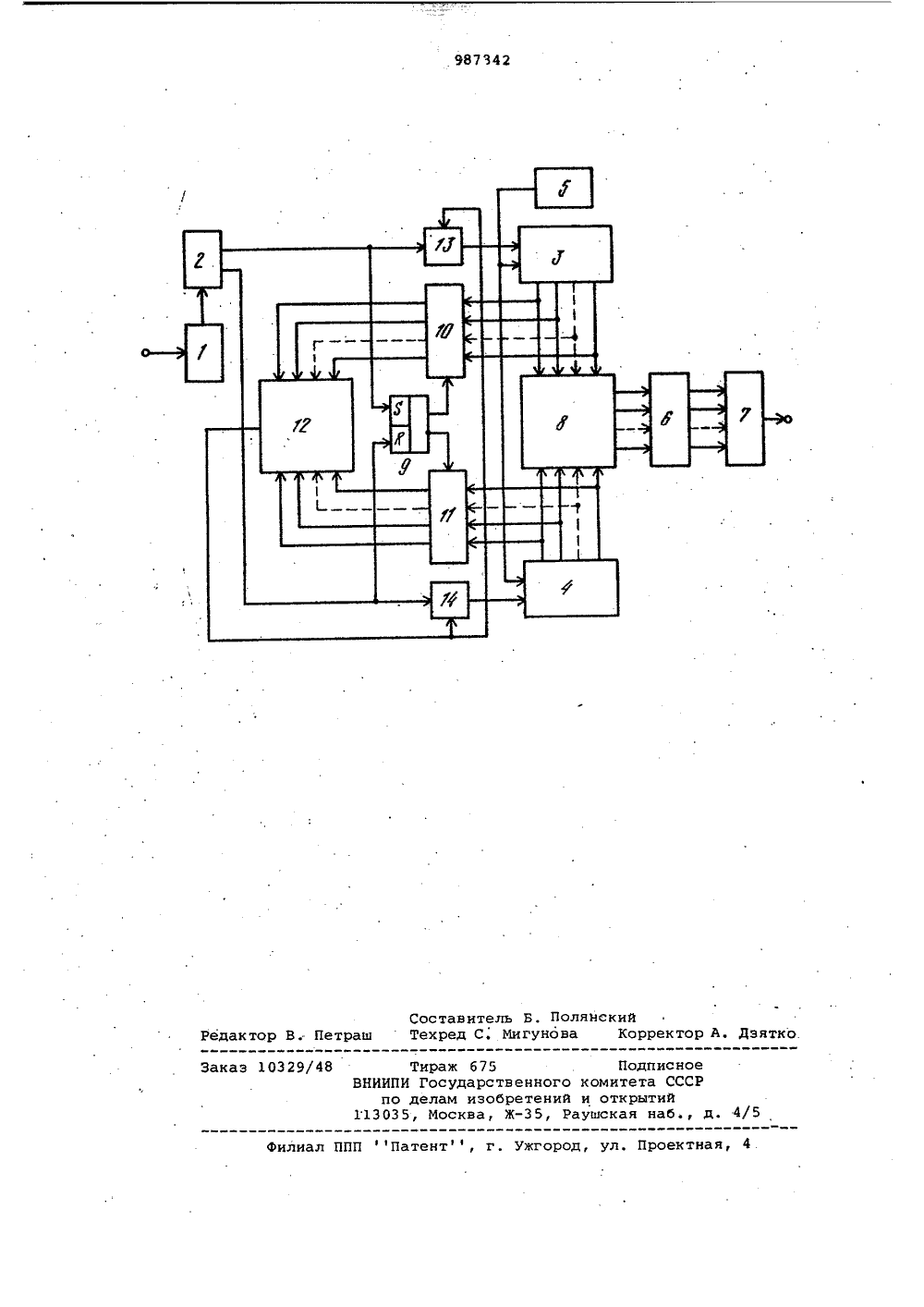

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(22) Заявлено 130781 (21) 3316518/18-09 . Я 1 М. Кд,з с присоединением заявки Ко(23) Приоритет Н 04 1. 27/14 Государственный комитет СССР по дедам иэобретеннй н открытийДата опубликования описания 07.01.83.ГИзобретение относится к радиотехнике и может использоваться в устройствах передачи данных дискретной информации. 5По основному авт. св. Р 815960 известен цифровой демодулятор частотноманипулированных сигналов, содержащий последовательно соединенные Формирователь импульсов и коммутатор, 1 Овыходы которого подключены к установочным входам делительной частоты,выходы которых соединены с выходомгенератора опорной частоты, дешифратор, решающий блок и блок сравнения,выходы которого через дешифратор подключены к входам решающего блока, приэтом входы блока сравнения соединеныс выходами делителей частоты 1).Однако известный цифровой демодулятор имеет низкую помехоустойчивость.Цель изобретения - повышение помехоустойчивости путем исключения временных искажений,Для достижения поставленной цели визвестный цифровой демодулятор введены два элемента ИЛИ, дополнительныйдешифратор, два блока ключей и ВЯ-триггер, выходы которого подключены куправляющим входам блоков ключей, выходы которых соединены с входами до- ЗО полнитель ного дешифратора, выход ко" торого подключен к первым входам элементов ИЛИ, вторые входы которых соединены с выходами коммутатора и соответствующими входами РЯ-триггера, при этом выходы элементов ИЛИ подключены к установочным входам делителей частоты, выходы которых соединены с сигнальными входами соответствующих блоков ключей.На чертеже представлена структурная электрическая схема предлагаемого циФрового дешифратора.Цифровой демодулятор частотно-манипулированных сигналов содержит формирователь 1 импульсов, коммутатор 2, первый и второй делители частоты 3 и 4 соответственно, генератор 5 опорной частоты, дешифратор 6, решающий блок 7, блок 8 сравнения, КЯ-триггер 9, первый 10 и второй 11 блоки ключей, дополнительный дешифратор 12, первый 13 и второй 14 элементы ИЛИ.Демодулятор работает следующим образом.Частотно-манипулированный сигнал поступает на Формирователь 1 импульсов, в котором формируются импульсы сброса по переходам входного сигнала через нуль. Коммутатор 2 осуществляетпоочередно подачу импульсов сброса иа установочные входы идентичных делителей 3 и 4 частоты через элементы ИЛИ 13 и 14 и входы ВЯ-триггера 9, Делители 3 и 4 частоты осуществляют деление частоты сигнала генератора 5 опорной частоты, При отсутствии имйульсов сброса делители 3 и 4 частоты синхронноделят частоту сигнала генератора 5 опорной частоты и на выхо, дах разрядов делителей 3 и 4 частоты происходит синхронная смена разрядов числа, Блок 8 сравнения, например арифметическое устройство, осуществляет вычисление разности между числами. Нулевой результат сравнения посту пает в дешифратор б.При поступлении импульсов сброса с коммутатора 2 между числами на выходе счетчиковых делителей 3 и 4 частоты за счет воздействия импульсов сброса устанавливается определенная разность, которая вычисляется в блоке 8 сравнения и дешифрируется в програм мируемом дешифраторе б,а с помощью решающего блока 7 представляется в виде значений разрядов принимаемой комбинации.При постоянстве частоты на входе, демодулятора сохраняется постоянная разница между числами на выходах разрядов счетчиковых делителей 3 и 4 30 частоты, а сами числа изменяются только до определенного числа И, так как существует постоянная установка делителей 3 и 4 частоты в нулевое состояние. 35За счет поочередной подачи импульсов сброса от коммутатора 2 на Я- и В- входы ВЯ- тригге ра 9 дополните ль ный дешифратор 12 поочередно подключается через соответствующий блок 10 или 40 11 ключей (в зависимости от состояния ВЯ-триггера 9) к делителю частоты, установленному в нулевое), состояние. Дешйфруется дополнительным дешифрато-. ром число, на единицу большее предель 45 ного числа для разрядов делителей 3 и 4 частоты, т.е. состояние И+1 соответствующего делителя частоты, За счет этого и описанных выше переключений дополнительного дешифратора 12 5) при наличии сигнала на входе демодулятора установка в нуль делителей 3и 4 частоты производится только поимпульсам от коммутатора 2.При окончании сигнала на входеодемодулятора числа на выходах разрядов делителей) 3 и 4 частоты могут становиться больше М, но уже при числе0+1 на выходе. разрядов одного из делителей частоты дополнительным дешифратором 12 формируется импульс наего выходе, который через оба элемента ИЛИ 13 и 14 устанавливает оба делителя частоты в нулевое состояние,тем самым обеспечивая своевременноеокончание формирования последнего раз.ряда комбинации, завершающий процесспередачи информации, и дальнейшуюсинхронную работу делителей 3 и 4 частоты,Таким образом, использование изобретения позволяет исключить временныеискажения посылок последних разрядовкомбинаций, завершающих процесс передачи информации. Введенная принудительная установка цифрового демодулято-ра в исходное состояние увеличиваети помехоустойчивость, так как в этомслучае искажения края посылки (отсутствие формирования импульса сбросана краю посылки) будут исправленыза сЧет формирования его введеннымиузлами.Кроме того, расширяются функциональные воэможности цифрового демоду-.Лятора, так как он обеспечивает безыс.каженную работу в стартстопном и синхронном режимах передачи информации ине требует специальных устройств илиоперативного вмешательства в процессприема информации на этапе окончанияприема. Формула изобретенияЦифровой демодулятор частотно-манипулированных сигналов по авт, св.Р 815960, о т л и ч а ю щ и й с ятем, что, с целью повышения его помехоустойчивостипутем исключения временных искажений, в него введены дваэлемента ИЛИ, дополнительный дешифратор, два блока ключей и ВЯ-триггер,выходы которого подключены к управляющим входам блоков ключей, выходы которых соединены с входами дополнительного дешифратора, выход которого подключен к первым входам элементов ИЛИ,вторые входы которых соединены с выходами коммутатора и соответствующими входами ИЯ-триггера,.при этом выходы элементов ИЛИподключены к установочным входам делителей частоты, выходы которых соединены с сигнальнымивходами соответствующих блоков ключей.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 815960, кл. Н 04 Ь 27/14, 1979 (прототип) .; Петра Заказ 10329 4 5 Филиал ППППатент , г. Ужгород, ул. Проектная, 4 Т ВНИИПИ по д 113 03 5, аж б 75 Подписное сударственного комитета СССР ам изобретений и открытий осква, Ж5, Раушская наб.,

СмотретьЗаявка

3316518, 13.07.1981

ПРЕДПРИЯТИЕ ПЯ Р-6120

РОДЬКИН ИВАН ИВАНОВИЧ

МПК / Метки

МПК: H04L 27/14

Метки: демодулятор, сигналов, цифровой, частотно-манипулированных

Опубликовано: 07.01.1983

Код ссылки

<a href="https://patents.su/3-987842-cifrovojj-demodulyator-chastotno-manipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор частотно-манипулированных сигналов</a>

Предыдущий патент: Устройство для детектирования сигналов двойной частотной телеграфии

Следующий патент: Устройство для формирования фазоманипулированного сигнала

Случайный патент: Устройство преобразования кодов