Цифровой коррелятор для обнаружения эхо-сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

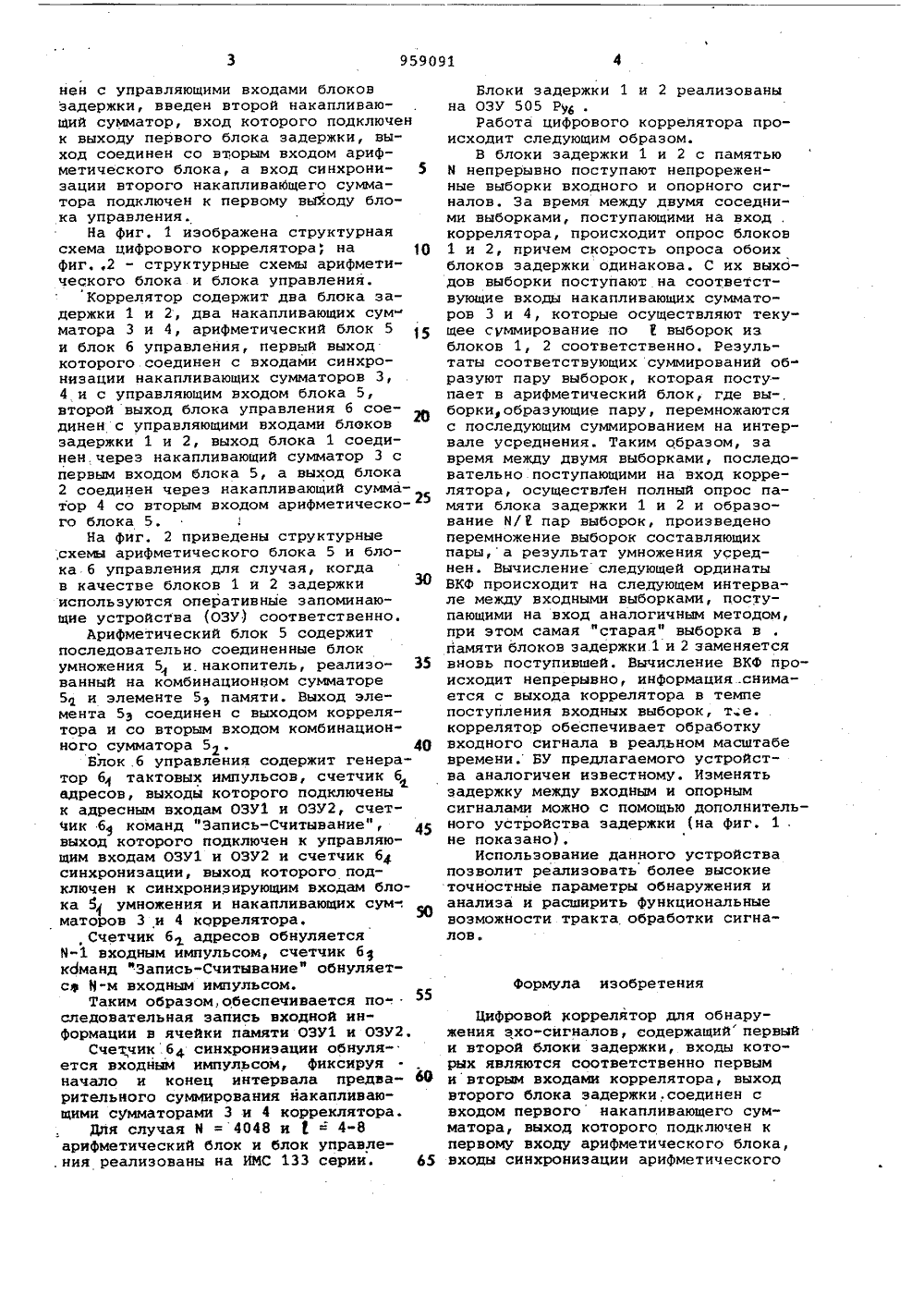

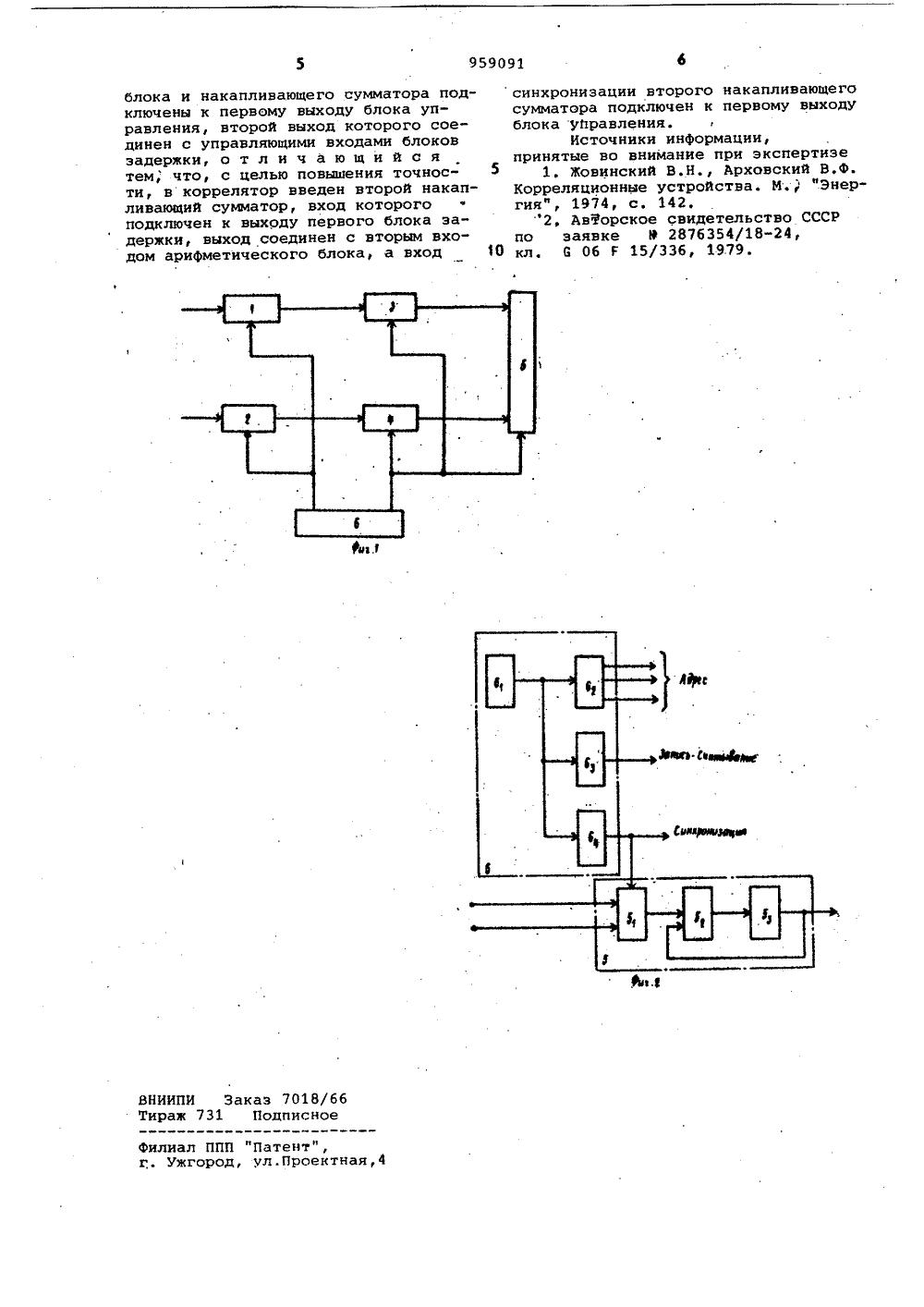

(и)959091 Союз СоветскикСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 11,1280 (21) 3215910/18-24 511 М. Иа.з с присоединением заявки Мо С 06 Г 15/336 Государствеииый комитет СССР по делам изобретений и открытий(23) Приоритет Опубликовано 150982. Бюллетень Йо 34 Дата опубликования описания 150982(54) ЦИФРОВОЙ КОРРЕЛЯТОР ДЛЯ ОБНАРУЖЕНИЯ ЭХО-СИГНАЛОВ Изобретение:относится .к области. специализированных средств вычислительной техники, предназначенной для взаимнокорреляционной обработкиэхо-сигналов.Известей цифровой коррелятор содержащий, частотно-импульсный преоб" раэователь, логические блоки, блок . . задержки, реверсивные счетчики.1.Однако данный коррелятор характЕ" рнзуется недостаточно высоким отно- . шением сигнал - шум на выходе.Известен также коррелятор, содер" жащий два блока задержки арифмети:ческий блок, накапливающий сумматор и блок управления 2(,Недостатком этого коррелятора яв-. ляеЖся.неидентичность .обработки сиг-. налов (опорного и Входного), так как в первый блок задержки записываются прореженныевыборки опорного сигнала, а непрореженные выборки входного сигнала со второго блока задержки подвергаются перед подачей в арифметический блок предварительному суммированию. Это приводит к уменьшению точности вычисленияординат взаимо- корреляционной функции (ВКФ),. при. чем величины ошибок различны при формировании различных зондирующих сиг наловКроме того, при обработкенепрерывных сигналов или сигналовзначительной длительности требуетсянепрерывное обновление памяти нетолько второго, но и первого блоказадержки.Цель изобретенияповьввЕние точности вычисления ординат ВКФ и расширение функциональных воэможностейкоррелятора.Сущность изобретения заключаетсяв том, что обеспечивается идентичность обработки входного и опорногосигналов, включая непрерывное обнов ление информации в памяти корреклятора.Поставленная цель достигаетс тем,что в цифровой коррелятор для обнаружения эхо-сигналов содержащий первыйи второй блоки задержки, входы которых являются соответственно первыми вторым входами коррелятора, в выход второго блока задержки соединенсо входом первого накапливающего сум матора, выход"которого подключен кпервому входу арифметического блока,входы синхронизации арифметическогоблока и накапливающего сумматора подключены к первому выходу блока уп равлениявторой выход которого соеди-65 нен с управляющими входами блоковзадержки, введен второй накапливающий сумматор, вход которого подключенк выходу первого блока задержки, выход соединен со вторым входом арифметического блока, а вход синхрониэации второго накапливающего сумматора подключен к первому выходу блока управления.На фиг. 1 изображена структурнаясхема цифрового коррелятора, на 10Фиг.,2 - структурные схемы арифметического блока и блока управления.Коррелятор содержит два блока задержки 1 и 2, два накапливающих сумматора 3 и 4, арифметический блок 5и блок 6 управления, первый выходкоторого соединен с входами синхронизации накапливающих сумматоров 3,4 и с управляющим нходом блока 5,второй выход блока управления б соединен с управляющими входами блоковзадержки 1 и 2, выход блока 1 соединен.через накапливающий сумматор 3 спервым входом блока 5, а выход блока2 соединен через накапливающий сумматор 4 со вторым входом арифметического блока 5.На фиг. 2 приведены структурные;схемы арифметического блока 5 и блока б управления для случая, когдан качестве блоков 1 и 2 задержки ЗОиспользуются оперативные запоминающие устройства (ОЗУ) соответственно.Арифметический блок 5 содержитпоследовательно соединенные блокумножения 5 и. накопитель, реалиэованный на комбинационном сумматоре5 и элементе 5 э памяти. Выход элемента 5 э соединен с выходом коррелятора и со вторым входом комбинационного сумматора 52. 40Блок б управления содержит генератор 64 тактовых импульсов, счетчик 6адресов, выходы которого подключенык адресным входам ОЗУ 1 и ОЗУ 2, счетчик б команд ПЗапись-Считывание",выход которого подключен к управляющим входам ОЗУ 1 и ОЗУ 2 и счетчик 64синхронизации, выход которого подключен к синхронизирующим входам блока 8 умножения и накапливающих сум-,маторов 3 и 4 коррелятора,, Счетчик б адресов обнуляетсяМвходным импульсом, счетчик бкоманд фЗапись-Считыванием обнуляется М-м входным импульсом.Таким образом, обеспечивается по"следовательная запись входной инФормации в ячейки памяти ОЗУ 1 и ОЗУ 2.Счетчик.64 синхронизации обнуляется входным импульсом, Фиксируяначало и конец интервала преднарительиого суммирования накапливающими сумматорами 3 и 4 корреклятора.Для случая М = 4048 и= 4-8арифметический блок и блок управле,ния реализованы на ИМС 133 серии. Блоки задержки 1 и 2 реализованына ОЗУ 505 Р .Работа цифрового коррелятора происходит следующим образом.В блоки задержки 1 и 2 с памятьюМ непрерывно поступают непрореженные выборки входного и опорного сигналов. За время между двумя соседними выборками, поступающими на входкоррелятора, происходит опрос блоков1 и 2, причем скорость опроса обоихблоков задержки одинакова. С их выходов выборки поступают на соответствующие входы накапливающих сумматоров 3 и 4, которые осуществляют текущее суммирование повыборок изблоков 1, 2 соответственно. Результаты соответствующих суммирований образуют пару выборок, которая поступает в арифметический блок, где вы-.боркиобразующие пару, перемножаютсяс последующим суммированием на интервале усредненияТаким образом, завремя между двумя выборками, последовательно поступающими на вход коррелятора, осуществлен полный опрос памяти блока задержки 1 и 2 и образование М/Й пар выборок, произведеноперемножение выборок составляющихпары,а результат умножения усреднен. Вычисление следующей ординатыВКФ происходит на следующем интервале между входными выборками, поступающими на вход аналогичным методом,при этом самая "старая" выборка впамяти блоков задержки 1 и 2 заменяетсявновь поступившей. Вычисление ВКФ происходит непрерывно, информация .снимается с выхода коррелятора в темпепоступления входных выборок, т е.коррелятор обеспечивает обработкувходного сигнала в реальном масштабевремени. БУ предлагаемого устройстна аналогичен известному. Изменятьзадержку между входным и опорнымсигналами можно с помощью дополнительного устройства задержки (на фиг. 1 .не показано),Использование данного устройствапозволит реализовать более высокиеточностные параметры обнаружения ианализа и расширить функциональныевозможности тракта обработки сигналов.формула изобретенияЦиФровой Коррелятор для обнаружения эхо-сигналов, содержащийпервый и второй блоки задержки, входы которых являются соответственно первым и вторым входами коррелятора, выход второго блока задержки, соединен с входом первого накапливающего сумматора, выход которого подключен к первому входу арифметического блока, входы синхронизации арифметического959091 П "Патент",д, ул.Проектна Филиал г,. Ужг блока и накапливающего сумматора подключены к первому выходу блока управления, второй выход которого соединен с управляющими входами блоковзадержки, о т л и ч а ю щ и й с ятем, что, с целью повышения точности, в коррелятор введен второй накапливающий сумматор, вход которогоподключен к выходу первого блока задержки, выход соединен с вторым входом арифметического блока, а вход 10 ВНИИПИ Заказ 7018/66Тираж 731 Подписное синхронизации второго накапливающегосумматора подключен к первому выходублока управления.Источники информации,принятые во внимание при экспертизе1. Жовинский В.Н., Арховский В.ф.Корреляционные устройства. И,; "Энергия", 1974, с. 142,2, Авторское свидетельство СССРпо заявке В 2876354/18-24,кл. 8 06 Г 15/336, 1979

СмотретьЗаявка

3215910, 11.12.1980

ПРЕДПРИЯТИЕ ПЯ В-2962

АНИСИМОВ ВАЛЕРИЙ ДМИТРИЕВИЧ, ЛИТМАН ЕФИМ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 17/18

Метки: коррелятор, обнаружения, цифровой, эхо-сигналов

Опубликовано: 15.09.1982

Код ссылки

<a href="https://patents.su/3-959091-cifrovojj-korrelyator-dlya-obnaruzheniya-ehkho-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой коррелятор для обнаружения эхо-сигналов</a>

Предыдущий патент: Устройство для моделирования сетевых графов

Следующий патент: Многоканальный статистический анализатор

Случайный патент: Магнитооптический способ регистрации динамических петель магнитного гистерезиса и устройство для его осуществления