Генератор псевдослучайной последовательности

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

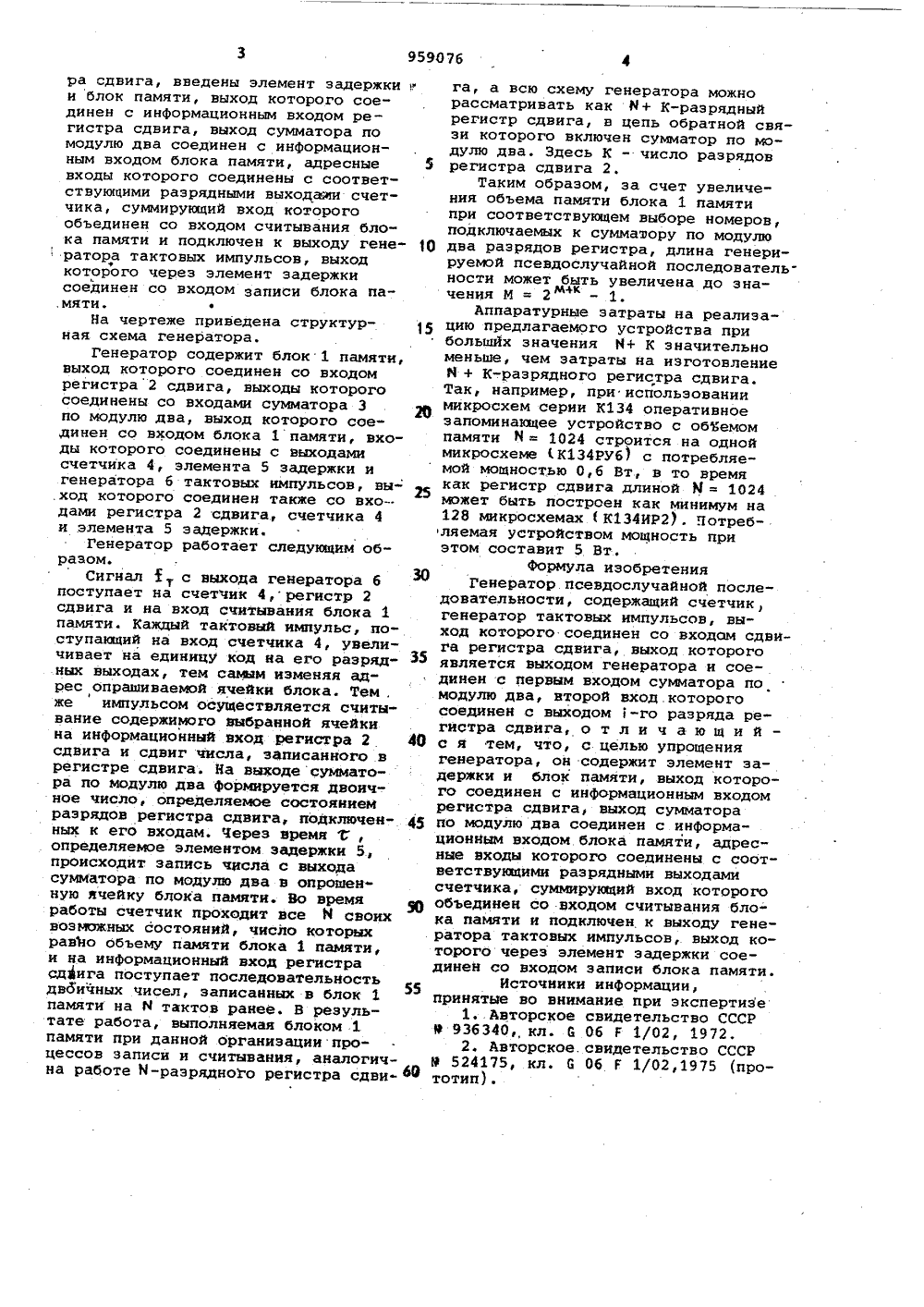

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистическихРеспублик пп 959076 К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(61) Дополнительное к авт. свид-ву -И 11 М.Кп. с присоединением заявки Мф -6 06 Г 7/58 Государственный комитет СССР по делам изобретений и открытийДата опубликования описания 15,09.82 1) Заявитель огодский политехнический институ(54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ 5 2 Изобретениевычислительной ь использовано пр оделировании сис о управления.Известен генератор псевдослучайных двоичных чисел, содержащий регистры сдвига с сумматорами по модулю два в цепях обратной связи и тактовый генератор, выход которого соединен с тактовыми входами регистров сдвига. При этом второй вход сумматора по модулю два каждого последующего .регистра сдвига соединен с выходом одной из ячеек предыдущего регистра сдвига. Длина генерируемой псевдослучайной последовательности определяется разрядностью регистров сдвига и и числом регистров тн тИ =2 и+иНедостатком данного устройства является громоздкость электронной схемы и сложность ее настройки при большой длине генерируемой последовательности, вызванные большим числом регистров сдвига и связей между Наиболее близким техническим ре шением к данному изобретению является генератор псевдослучайной последовательности, содержащий регистр сдвига и сумматор помодулю два в цепи обратной свяи, генератор тактовых импульсов, выход которогосоединен со входом регистра сдвига,а также счетчик и блок сумматоров (,2.Недостатком данного устройстваявляется малое значение периода псевдослучайной последовательности, ограниченное разрядностью регистра сдвига. Максимальная длина последовательности равна 2 - 1. Увеличение периода последовательности эа счет разрядности регистра приводит к усложнению схемы и снижению ее надежностиЦель изобретения - упрощение генератора при заданной длине последовательности.Для достижения поставленной цели в генератор псевдослучайной последовательности, содержащий счетчик,генератор тактовых. импульсов, выходкоторого .соединен со входом "Сдвиг"регистра сдвига, выход которого является выходом генератора и соединен с первым входом сумматора по моцулю два,. второй вход которого соецинен с выходом 1 -го разряда регистра сдвига, введены элемент задержки ги блок памяти, выход которого соединен с информационным входом регистра сдвига, выход сумматора помодулю два соединен с информационным входом блока памяти, адресные 5входы которого соединены с соответствующими разрядными выходки счетчика, суммирующий вход которогообъединен со входом считывания бло"ка памяти и подключен к выходу генератора тактовых импульсов, выходкоторого через элемент задержкисоединен со входом записи блока па.мяти.На чертеже приведена стРуктуРная схема генератора.Генератор содержит блок 1 памяти,выход которого соединен со входомрегистра 2 сдвига, выходы которогосоединены со входами сумматора 3 . рпо модулю два, выход которого соединен со входом блока 1 памяти, входы которого соединены с выходамисчетчика 4, элемента 5 задержки игенератора б тактовых импульсов, вы-.ход которого соединен также со входами регистра 2 сдвига., счетчика 4и элемента 5 задержки.Генератор работает следующим образом,Сигнал 1 т с выхода генератора бпоступает на счетчик 4, регистр 2сдвига и на вход считывания блока 1памяти. Каждый тактовый импульс, поступающий на вход счетчика 4, увеличивает на единицу код на его разрядных выходах, тем саьым изменяя адрес опрашиваемой ячейки блока. Тем .же импульсом осуществляется считывание содержимого выбранной ячейкина информационный вход регистра 2 40сдвига и сдвиг числа, записанного .врегистре сдвига. На выходе сумматора по модулю два формируется двоичное число, определяемое состояниемразрядов регистра сдвига, подключенных к его входам. Через время Г,определяемое элементом задержки 5,происходит запись числа с выходасумматора по модулю два в опрошенную ячейку блока памяти, Во время 6работы счетчик проходит все Й своихвозможных состояний, число которыхравно Объему памяти блока 1 памяти,и на информационный вход регистрасдвига поступает последовательностьдвоичных чисел, записанных в блок 1памяти на Й тактов ранее. В результате работа, выполняемая блоком 1памяти при данной Организации процессов записи и считывания, аналогична работе Й-разрядного регистра сдви- ф га, а всю схему генератора можнорассматривать как Й+ К-разрядныйрегистр сдвига, в цепь обратной связи которого включен сумматор по модулю два. Здесь К - число разрядоврегистра сдвига 2.Таким образом, эа счет увеличения объема памяти блока 1 памятипри соответствующем выборе номеров,подключаемых к сумматору по модулюдва разрядов регистра, длина генерируемой псевдослучайной последователь"ности может быть увеличена до значения М = 2 - 1.Аппаратурные затраты на реализацию предлагаемого устройства прибольшйх значения Й+ К значительноменьше, чем затраты на изготовлениеИ + К-разрядного регистра сдвига.Так, например, при использованиимикросхем серии К 134 оперативноезапоминающее устройство с обЪемомпамяти И -" 1024 строится на одноймикросхеме 1 К 134 РУб) с потребляемой мощностью 0,6 Вт, в то времякак регистр сдвига длиной М = 1024может быть построен как минимум на128 микросхемах ( К 134 ИР 2). потребляемая устройством мощность приэтом составит 5 Вт,Формула изобретенияГенератор псевдослучайной последовательности, содержащий счетчик,генератор тактовых импульсов, выход которого соединен со входом сдвига регистра сдвига, выход которогоявляется выходом генератора и соединен с первым входом сумматора помодулю два, второй вход. которогосоединен с выходом -го разряда регистра сдвига, о т л и ч а ю щ и йс я тем, что, с целью упрощениягенератора, он содержит элемент задержки и блок памяти, выход которого соединен с информационным входомрегистра сдвига, выход сумматорапо модулю два соединен с информационным входом блока памяти, адресные входы которого соединены с соответствующими разрядными выходамисчетчика, суммирующий вход которогообъединен со входом считывания блока памяти и подключен к выходу генератора тактовых импульсов, выход которого через элемент задержки сое"динен со входом записи блока памяти.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРМ 936340, кл. 6 Об Г 1/02, 1972.2. Авторское. свидетельство СССР9 524175, кл. О Об Г 1/02,1975 (прототип).959076 Составитель А, Карасовдактор О. Колесникова Техред З.Палий Гриценко к Зака иал ДПП "Пат 18/ббВНИИПИ Госпо делам113035, Москв Тираж 7 дарственного изобретений , Ж, Рауш 1 Водписноекоиитета СССРи открытийская наб., д. 4/5 г. Ужгород, ул, Проектная, 4

СмотретьЗаявка

3243239, 02.02.1981

ВОЛОГОДСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ВОДОВОЗОВ АЛЕКСАНДР МИХАЙЛОВИЧ, ЛАБИЧЕВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/58

Метки: генератор, последовательности, псевдослучайной

Опубликовано: 15.09.1982

Код ссылки

<a href="https://patents.su/3-959076-generator-psevdosluchajjnojj-posledovatelnosti.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайной последовательности</a>

Предыдущий патент: Многоканальный генератор пачек случайных импульсов

Следующий патент: Устройство для умножения элементов конечного поля размерности 2

Случайный патент: Пресс для изготовления изделий из резины