Устройство защиты от ошибок с решающей обратной связью

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 866766

Авторы: Замрий, Митяков, Рыськов, Феоктистов

Текст

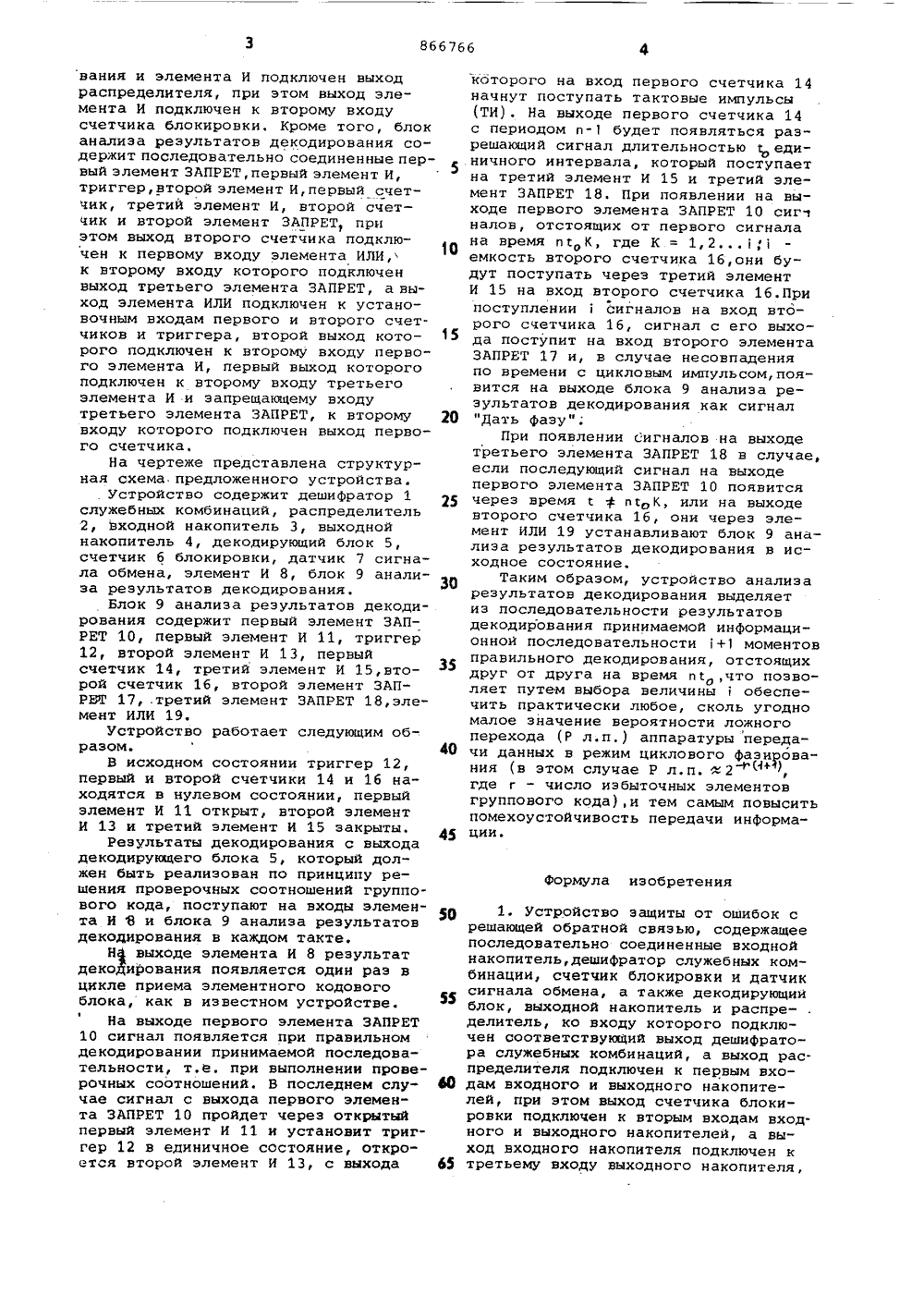

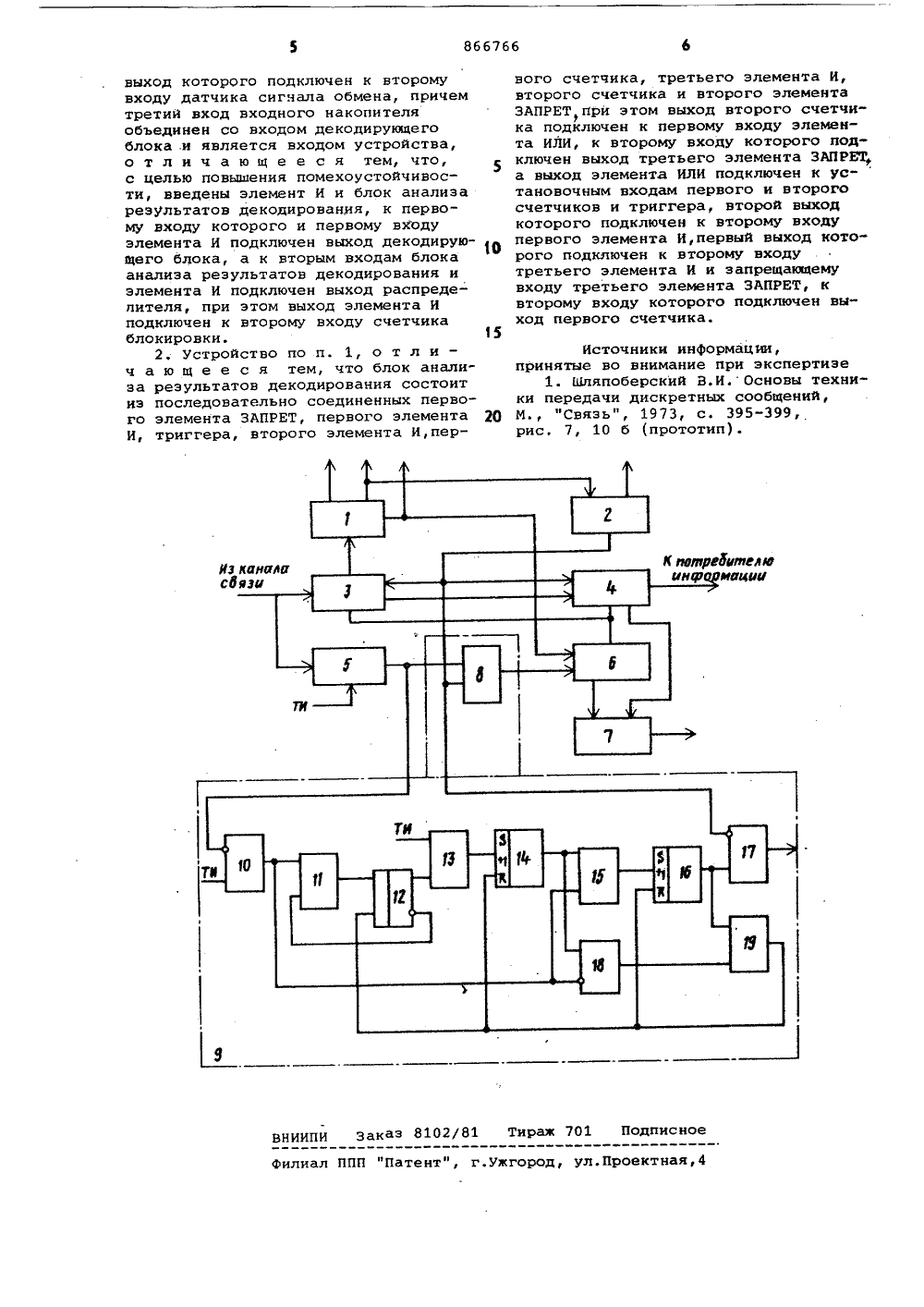

Свез Советских Соцналнстических Реснублнк(5)М. К 2) 3 ено 0201,80 (21) 2863078/18-09мнением заявки йо с присое 41/16 осударствеиный комите СССР по делам изобретений и . открытий(72) Авторь 54) УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК С РЕШАОЦЕЙ ОБРАТНОЙ СВЯЗЬЮ2ия - пов устройство тойчивость известно й помехо Изобретение относится к технике передачи дискретной информации и может быть использовано при модернизации существующей и создании новойаппаратуры передачи данных.Известно устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенныевходной накопитель, дешифратор служебных комбинаций, счетчик блокировки и датчик сигнала обмена, а также декодйрующий блок, выходной накопитель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций,а 15выход распределителя подключен к первымавходам входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входамвходного и выходного накопителей,а 20выход входного накопителя подключенк третьему входу выходного накопителя, выход которого подключен к второму входу датчика сигнала обмена,при" чем третий вход входного накопителяобъединен со входом декодирующегоблока и является входом устройства 11.Однако е обладает низко ус ю. 30 Цель изобретен ышехоустойчивости.Для этого в устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенные входной накопитель, дешифратор служебных комбинаций, счетчик блокировки и датчик сигнала обмена, а также декодирующий блок, выходной накопитель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций, а выход распределителя подключен к первым входам входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей, а выход входного накопителя подключен к третьему входу выходного накопителя, выход которого подключен к второму входу датчика сигнала обмена, причем третий вход входного накопителя объединен со входом декодирующего блока и является входом устройства, введены элемент И и блок анализа результатов декодирования, к первому входу которого и первому входу элемента И подключен выход декодирующего блока, а к вторым входам блока анализа результатов декодиро 86676620 40 45 вания и элемента И подключен выходраспределителя, при этом выход элемента И подключен к второму входусчетчика блокировки. Кроме того, блоканализа результатов декодирования содержит последовательно соединенные первый элемент ЗАПРЕТ, первый элемент И,триггер, второй элемент И,первый счетЧик, третий элемент И, второй счетчик и второй элемент ЗАПРЕТ, приэтом выход второго счетчика подключен к первому входу элемента ИЛИ,к второму входу которого подключенвыход третьего элемента ЗАПРЕТ, а выход элемента ИЛИ подключен к установочным входам первого и второго счетчиков и триггера, второй выход которого подключен к второму входу первого элемента И, первый выход которогоподключен к второму входу третьегоэлемента И и запрещающему входу третьего элемента ЗАПРЕТ, к второму входу которого подключен выход первого счетчика,На чертеже представлена структурная схема. предложенного устройства.Устройство содержит дешифратор 1служебных комбинаций, распределитель2, Входной накопитель 3, выходнойнакопитель 4, декодирующий блок 5,счетчик 6 блокировки, датчик 7 сигнала обмена, элемент И 8, блок 9 анализа результатов декодирования.Блок 9 анализа результатов декодирования содержит первый элемент ЗАПРЕТ 10, первый элемент И 11, триггер12, второй элемент И 13, первыйсчетчик 14, третий элемент И 15,второй счетчик 16, второй элемент ЗАПРЖ 17, .третий элемент ЗАПРЕТ 18,элемент ИЛИ 19.Устройство работает следующим образом.В исходном состоянии триггер 12,первый и второй счетчики 14 и 16 находятся в нулевом состоянии, первыйэлемент И 11 открыт, второй элементИ 13 и третий элемент И 15 закрыты.Результаты декодирования с выходадекодирующего блока 5, который должен быть реализован по принципу решения проверочных соотношений группового кода, поступают на входы элемента И 8 и блока 9 анализа результатовдекодирования в каждом такте.Нф выходе элемента И 8 результатдекоДирования появляется один раз вцикле приема элементного кодовогоблока, как в известном устройстве.На выходе первого элемента ЗАПРЕТ10 сигнал появляется при правильномдекодировании принимаемой последовательности, т.е. при выполнении проверочных соотношений. В последнем случае сигнал с выхода первого элемен"та ЗАПРЕТ 10 пройдет через открытыйпервый элемент И 11 и установит триггер 12 в единичное состояние, откроется второй элемент И 13, с выхода 30 35 50 55 40 Формула изобретения 1. Устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенные входной накопитель, дешифратор служебных комбинации, счетчик блокировки и датчик сигнала обмена, а также декодирующии блок, выходной накопитель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций, а выход распределителя подключен к первым входам входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей, а выход входного накопителя подключен к третьему входу выходного накопителя,866766 НИИПИ Заказ 8102/81 Тираж 701 Подписное Филиал ППП "Патент", г.ужгород, ул.Проектная выход которого подключен к второму входу датчика сигнала обмена, причем третий вход входного накопителя объединен со входом декодирующего блока .и является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены элемент И и блок анализа результатов декодирования, к первому входу которого и первому входу элемента И подключен выход декодирую-щего блока, а к вторым входам блока анализа результатов декодирования и элемента И подключен выход распределителя, при этом выход элемента И подключен к второму входу счетчика блокировки. 152. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок анализа результатов декодирования состоит из последовательно соединенных первого элемента ЗАПРЕТ, первого элемента 2 О И, триггера, второго элемента И,перного счетчика, третьего элемента И,второго счетчика и второго элементаЗАПРЕТ при этом выход второго счетчика подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход третьего элемента ЗАПРЕТа выход элемента ИЛИ подключен к установочным входам первого и второгосчетчиков и триггера, второй выходкоторого подключен к второму входупервого элемента И,первый выход которого подключен к второму входутретьего элемента И и запрещающемувходу третьего элемента ЗАПРЕТ, квторому входу которого подключен выход первого счетчика. Источники информации,принятые во внимание при экспертизе1. Шляпоберский В.И. Основы техники передачи дискретных сообщениЯ,М., "Связь", 1973, с. 395-399,рис. 7, 10 б (прототип).

СмотретьЗаявка

2863078, 02.01.1980

ВОЕННАЯ ОРДЕНА ЛЕНИНА КРАСНОЗНАМЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО

ЗАМРИЙ АНДРЕЙ СЕМЕНОВИЧ, МИТЯКОВ МИХАИЛ ИВАНОВИЧ, РЫСКОВ ЮРИЙ ДМИТРИЕВИЧ, ФЕОКТИСТОВ ВЛАДИМИР ЛАЗАРЕВИЧ

МПК / Метки

МПК: H04L 1/16

Метки: защиты, обратной, ошибок, решающей, связью

Опубликовано: 23.09.1981

Код ссылки

<a href="https://patents.su/3-866766-ustrojjstvo-zashhity-ot-oshibok-s-reshayushhejj-obratnojj-svyazyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство защиты от ошибок с решающей обратной связью</a>

Предыдущий патент: Устройство обнаружения и исправления вставок и выпадений информации

Следующий патент: Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью

Случайный патент: Литейная штамповая сталь