Устройство для приема частотноманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 801298

Автор: Сартаков

Текст

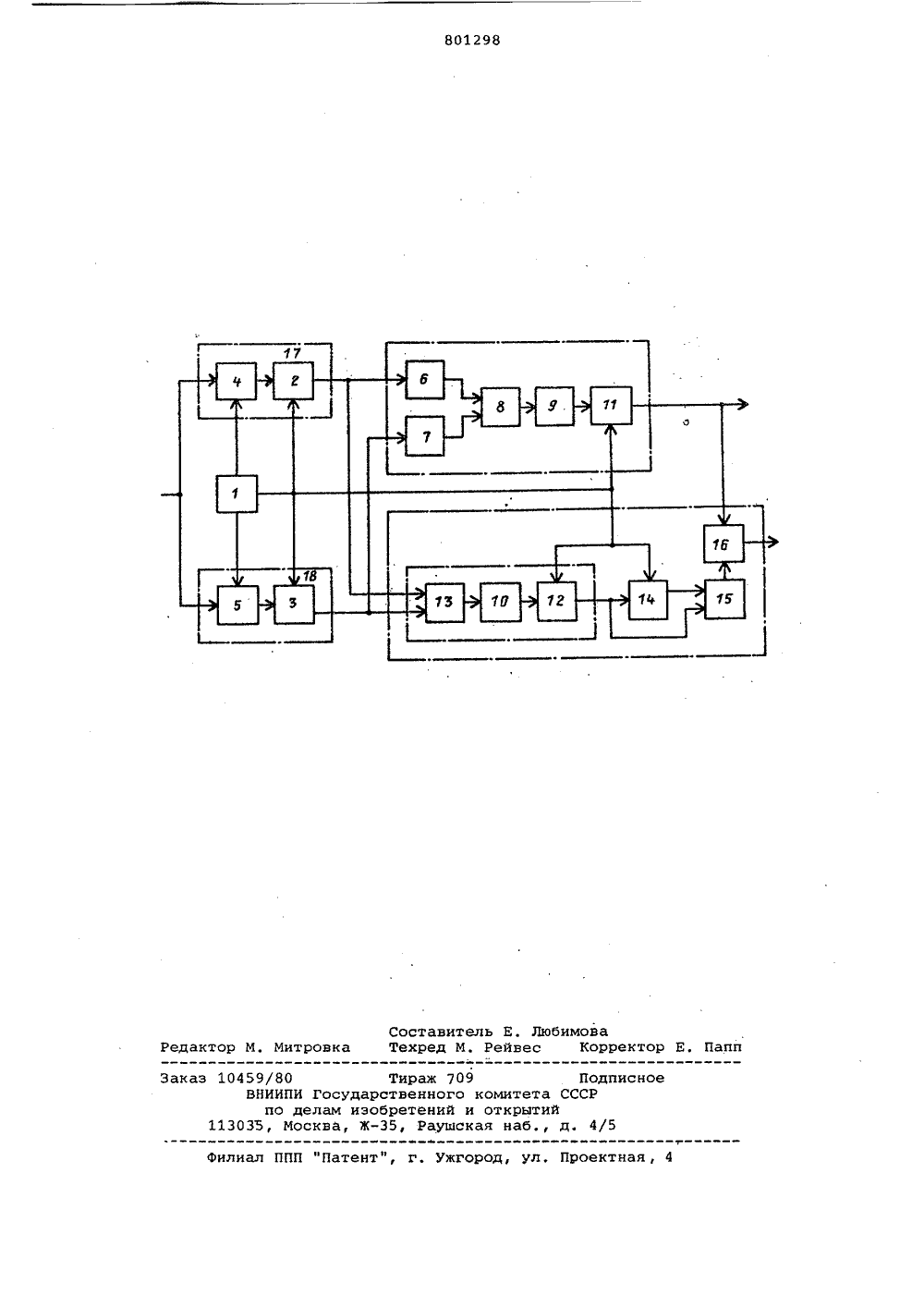

Союз Советских Социапистичесиих РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ н 1801298(22) Заявлено 260279 (21) 2731406/18-09с присоединением заявки Йо(5)М. Кл.з Н 0427/14 Государственный комитет СССР но делам изобретениИ и открытий(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ЧАСТОТНОМАНИПУЛИРОВАННЫХ СИГНАЛОВИзобретение относится к технике связи и может использоваться для приема частотно-манипулированных сигналов без разрыва фазы.Известно устройство для приема частотно- манипулированныхсигналов, содержащее блок формирования опорных сигналов и сигналов тактовой синхронизации, выходы которого подключены к первым входам интеграторов и перемножителей, выходы которых соединены со вторыми входами интеграторов, выходы которых подключены ко входам соответствующих блоков вычисления модуля сигнала, выходы 15 которых соединены со входами блока вычитания, выход которого через первый компаратор подключен к первому входу первого триггера, второй вход которого соединен с выходом блока 20 формирования опорных сигналов и сигналов тактовой синхронизации, а вторые входы перемножителей объединены 11.Одйако верность сигналов, прини маемых данным устройством, невысока.Цель изобретения - повышение верности принимаемых сигналов.Укаэанная цель достигается тем, что в известное устройство введены 30 последовательно соединенные сумматор, второй компаратор, второй триггер, элемент задержки, первый сумматор по модулю два и второй сумматор по модулю два, ко второму входу которого подключен выход первого триггера, второй вход которого соединен со вторыми входами элемента задержки и второго триггера, выход которого подключен ко второму входу первого сумматора по модулю два, при этом выходы интеграторов соединены со входами сумматора.На чертеже представлена структурная электрическая схема предлагаемого устройства.Устройство для приема частотноманипулированных сигналов содержит блок 1 формирования опорных сигналов и сигналов тактовой синхронизации, интеграторы 2 и 3, перемножители 4 и 5, блоки 6 и 7 вычисления модуля сигнала, блок 8 вычитания, первый и второй компараторы 9 и 10, первый и второй триггеры 11 и 12, сумматор 13, элемент 14 задержки, первый и второй сумматоры 15 и 16 по модулю два, причем интеграторы 2 и 3 и перемножители 4 и 5 объединены в корреляторы 17 и 18 соответственно, 801298Устройство работает следующим образом.На входы корреляторов 17 и 18 поступают частотно-манипулированные сигналы. В перемножителях 4 и 5 осуществляется перемножение входного сигнала с опорными сигналами. Результаты перемножения интегрируются в интеграторах 2 и 3. По сигналу тактовой синхронизации осуществляется разряд интеграторов 2 и 3 и устроЯство подготавли-о вается к приему следующей посылки. В момент, предшествующий разряду, сигнал на выходе одного из интеграторов 2 или 3 достигает максимальной величины, по абсолютному значению, а на выходе другого интегратора - равен нулю. Эти сигналы поступают на блоки 6 и 7, где определяются их абсолютные значения. Блок 8 вычисляет разность. полученных абсолютных значений сигналов, Первый компара тор 9 формирует уровень логической единицы при положительной полярности выходного сигнала блока 8 и уровень логического нуля - при отрицательной. С приходом сигнала такто вой синхронизации первый триггер 11 устанавливается в соответствующее состояние и сохраняет его до прихода следующего сигнала тактовой синхронизации. Таким образом, на выходе первого триггера 11 восстанавливается исходная информация, закодированная частотой посылки.Выходные сигналы интеграторов 2 и 3 суммируются н сумматоре 13, Полярность выходного сигнала сумматора 13 в момент, предшествующий сигналу тактовой синхронизации, определяется полярностью наибольшего по абсолютному значению из суммируемых сигналов, которая, н свою очередь, зависит от 49 конечной Фазы посылки. Второй компаратор 10 формирует уровень логической единицы при положительной полярности выходного сигнала сумматора 13 и уровень логического нуля - при отрицательной, С приходом сигнала ,тактовой синхронизации второй триггер 12 устанавливается в соответствующее состояние и сохраняет его до прихода следующего сигнала тактовой синхронизации. С помощью элемента 14 и первого сумматора 15 Фиксируется изменение конечной фазы очередной посылки по сравнению с предыдущей или отсутствие этого изменения. При отсутствии искажений посылка с 55 четным количеством полупериодон колебания имеет конечную фазу, одинаковую с предыдущей посылкой, а посылка с нечетным количеством полупериодов колебания - противоположную. Проверка этого условия осуществляется вторым сумматором 16. Если условие не ныполняется, на выходе второго сумматора 16 появляется сигнал единичного уровня, свидетельствующий о наличии ошибки в принятой последовательности посылок.Таким образом, предлагаемое устройство позволяет обнаруживать фактические ошибки приема, не вводя в сообщение избыточную проверочную информацию. Формула изобретенияустройство для приема частотноманипулированных сигналов, содержащее блок формиронания опорных сигналов и сигналов тактовой синхронизации, выходы которого подключены кпервым входам интеграторов и перемножителей, выходы которых соединенысо вторыми входами интеграторов, выходы которых подключены ко входамсоответствующих блоков вычислениямодуля сигнала, выходы которых соединены со входами блока вычитания,выход которого через первый компаратор подключен к первому входу первого триггера, второй вход которогосоединен с выходом блока формирования опорных сигналов и сигналов тактовой синхронизации, а вторые входыперемножителей объединены, о т л ич а ю щ е е с я тем, что, с цельюповышения верности принимаемых сигналов, в него введены последовательносоединенные сумматор, второй компаратор, второй триггер, элемент задержки, первый сумматор по модулюдва и второй сумматор по модулю два,ко второму нходу которого подключенныход первого триггера, второй входкоторого соединен со вторыми входами элемента задержки и второго триггера, выход которого подключен ковторому нходу первого сумматорапо модулю два, при этом выходы интеграторов соединены со входами сумматора.Источники информации,принятые во внимание при экспертизе1. Финк Л.М. Теория передачидискретных сообщений. М., "Советское радио", 1970, с. 155-156 (прототип),801298 бимова Составитель Е.Техред М. Рейве апп Мит тор Е. едакт каэ е Филиал ППП "Патент", г. Ужгород, ул. Проектная 10459/80ВНИИПИ Гопо делам13035 у Москв Тираж 709дарственного киэобретений иЖ, Раушска Подписмитета СССРткрытийнаб., д. 4/5

СмотретьЗаявка

2731406, 26.02.1979

ПРЕДПРИЯТИЕ ПЯ В-8145

САРТАКОВ АНАТОЛИЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: H04L 27/14

Метки: приема, сигналов, частотноманипулированных

Опубликовано: 30.01.1981

Код ссылки

<a href="https://patents.su/3-801298-ustrojjstvo-dlya-priema-chastotnomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема частотноманипулированных сигналов</a>

Предыдущий патент: Цифровой частотный детектор

Следующий патент: Приемник сигналов с угловоймодуляцией

Случайный патент: Способ регенерации отработанной серной кислоты