Преобразователь логического уровня

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 786006

Авторы: Артеменко, Белый-Ткач

Текст

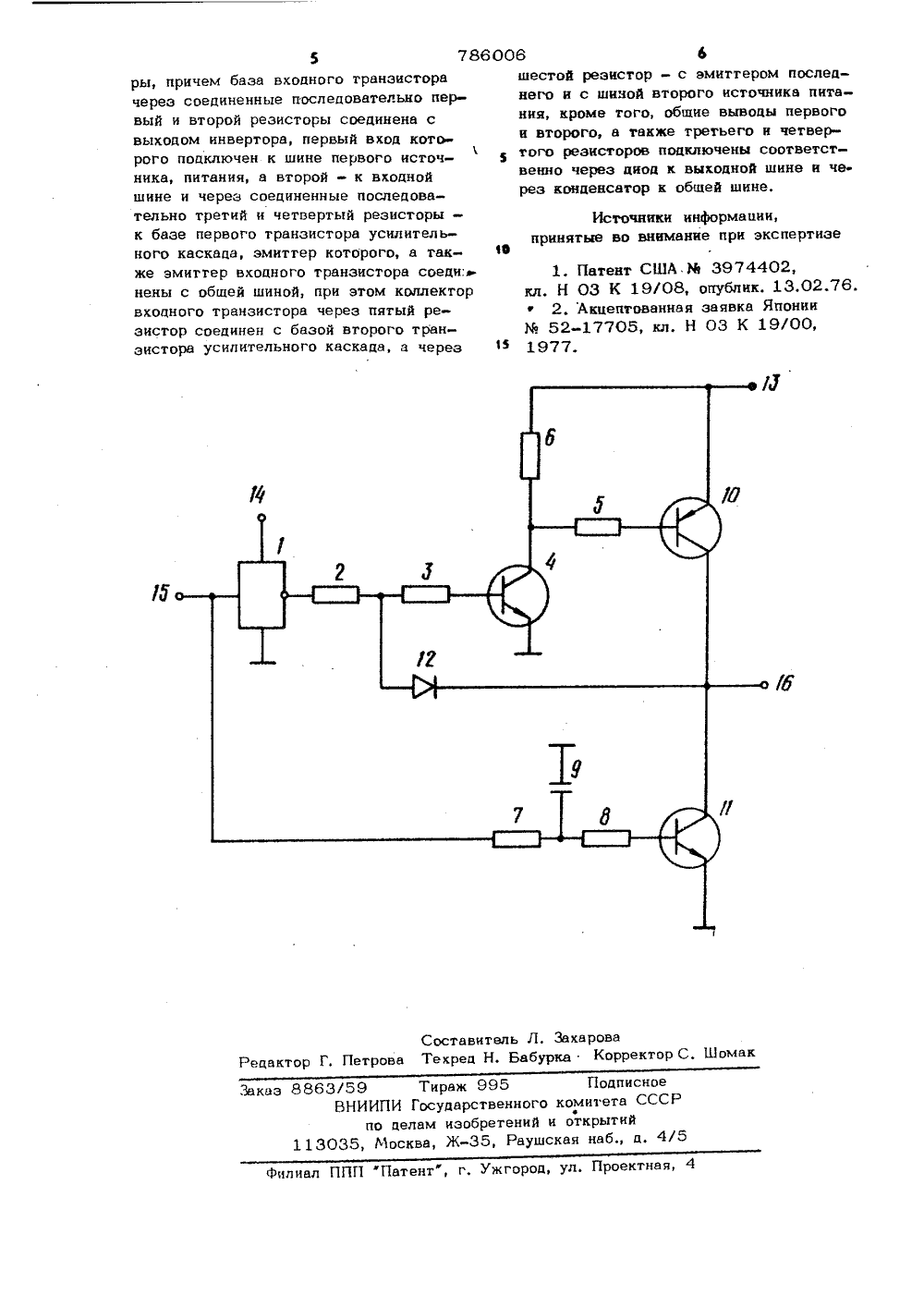

О П И С А Н И Е о 1)786006ИЗОБВЕТЕН ИЯ Союз Советски нСоциалистическихРеспублик(23) Приоритет ва делам изобретений и открытийВата опубликования описания 10,12,80(54) ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ Изобретение относится к импульсной технике, может быть использовано при проектировании радиоэлектронной аппаратуры.Известны устройства преобразования уровней логических сигналов для их после 5 дующей передачи по линиям связи, содержащие токовый переключатель, принимающий логические сигналы первого уровня и управляемый им выходной усилитель1 а сигналов второго, более высокого уровняИ.Недостатками известного устройства являются изменение уровня выходного сигнала с изменением сопротивления нагрузки и не оптимальное использование мощности выходных сигналов для образования помехоустойчивого канала.Кроме того, известны преобразователи логического сигнала, содержащие вход- ной и управляю пий транзисторы, а также усилительный каскад на транзисторах 2.Недостатками этого устройства являются зависимость уровня выходного сигнала от величины сопротивления нагрузки и низкая помехоустойчивость и надежность прп случайных длительных замыканиях на линии передачи.Цель изобретения - повышение помехоустойчивости и стабильности выходных параметров преобразования.Для этого в преобразователь содержаший входной транзистор, усилительный каскад, выполненный на транзисторах, коллекторы которых соединены с выходной шиной, резисторы, диод и источники питания, введены инвертор, конденсатор и дополнительные резисторы, причем база входного транзистора через соединенные последовательно первый и второй резисторы соединена с выходом инвертора, первый вход которого подключен к шине первого источника питания, а второй - к входной шине и через соединенные последовательно третий и четвертый резисторы - к базе первого транзистора усилительного каскада, эмиттер которого, а также эмиттер входного транзистора сое20 3 78600динены с общей шиной, при.этом коллектор входного транзистора через пятыйрезистор соединен с базой второго транэистора усилительного каскада, а черезшестой резистор - с эмиттером послед 5него и с шиной второго источника питания, кроме того, общие выводы первогои второго, а также третьего и четвертого резисторов подключены соответственно через диод к выходной шине и через щоконденсатор к общей шине.На чертеже представлена принципиал 1 ьная электрическая схема устройства,Инвертор 1 через резисторы 2 и 3соединен с базой транзистора 4, резисторы 5-8, конденсатор 9, усилительныйкаскад, выполненный на транзисторах10 и 11, диод 12, шины 13 и 14 источников питания, входная шина (вход)15, выходная шине (выкод) 16,Инвертор 1, резисторы 2 и 3, транзистор 4, резисторы 5 и 6, шина 13составляют канал управления транзистором 10 с задержкой Г, где Г - суммарное время задержки сигнала в инверторе 1 транзисторе 4.Резисторы 7 и 8, конденсатор 9составляют канал управления транзистором 11 с задержками (,2 на отпираниеи Т не запирение транзистора 11,При этом задержкиинаходятся2 3в соотношении2ЪВыбором величины резистора 7 и конденсатора 9 устанавливается неравенст 35воГ 6 фустанавливается логическая единица второго, более высокого уровня. При этом не диод 12 подается обратное смешаюшее напряжение, при этом выходное сопротивление становится равным сопротивлению насыщенного транзистора 10. При поступлении не вход 15 сигнала логическая "единица" с задержкой 7; закрывается транзистор 10, с задержкой Я Я;, открывается транзистор 11; на выходе 16 устанавливается состояние логический нуль", При этом выходное сопротивление становится равным сопротЬлению насыщенного транзистора 11.При случайном замыкании на линии в интервале времени, когда на входе 15 имеет место состояние логической единицы", изменений в состоянии компонентов устройства не происходит.При случайном коротком замыкании на линии в интервале времени, когда на входе 15 имеет место состояние логический "нуль", обший вывод резисторов 2 и 3 соединяется с общей шиной через диод, смещенный в прямом направлении, транзистор 4, закрываясь, закрывает транзистор 10, ток транзистора 10 падает до нуля.После снятия короткого замыкания устройство приходит в состояние, соответствуюшее уровню логического сигнала на входе 15.При возникновении в линии индуцированных помех последние подавляютсяуровня выходного сигнала от величины сопротивления нагрузки и высокая степень45 подавления индуцированнык в линии помех,50 При передече логических сигналов устройство работает следующим образом.При поступлении не вход 15 сигнала55 логический нуль первого уровня с задержкой "зекрьвеется транзистор 11, с задержкой Т, )Р открывается транзистор 10, не выходе 16 устройства исключающее возможность одновременного нахождения в открытом состояниитранзисторов 10 и 1 1,Устройство работает следующим образом.Зе исходное состояние принято состояние, при котором логической единице" не входе 15 соответствует логический "нуль" на выходе 16. При этом навыходе инвертора 1 и базе транзистора4 имеет место состояние логическогонуля, транзистор 4 закрыт, на базетранзистора 1 1 - логическая единица,транзистор 10 закрыт, транзистор 11открыт. низкоомным сопротивлением одного изнасышенных транзисторов 10 или 11.При этом уровень полезного сигнала влинии существенно не изменяется,Таким образом, в преобразователеобеспечиваются минимальная зависимость Формула изобретения Преобразователь логического уровня, содержащий входной транзистор, усилительный каскад, выполненный не транзисторах, коллекторы которых соединены с выходной шиной, резисторы, диод и источники питания, о т л и ч а ю ш и йс я тем, что, с целью повышения помехоустойчивости и стабильности выходных параметров, в него введены инвертор, конденсатор и дополнительные резисто786006 Составитель Л. ЗахароваРедактор Г. Петрова Текред Н. Бабурка Корректор С. Шома Подписноеомитета СССРоткрытийя наб. д. 4/ Тираж 995 ИПИ Государственного к о делам изобретений и Москва, Ж 35, Раушска3/5 ВН 13035,Филиал ППП "Патент", г. Ужгород, ул, Проектная ры, причем база входного транзисторачерез соединенные последовательно первый и второй резисторы соединена свыходом инвертора, первый вкод которого подключен к шине первого источника, питания, а второй - к входнойшине и через соединенные последовательно третий и четвертый реэисторы -к базе первого транзистора усилительного каскада, эмиттер которого, а также эмиттер входного транзистора соеди.иены с общей шиной, при этом коллекторвкодного транзистора через пятый резистор соединен с базой второго транзистора усилительного каскада, а через шестой резистор - с эмиттером последнего и с шиной второго источника питания, кроме того, общие выводы первого и второго, а также третьего и четвертого резисторов подключены соответственно через диод к выходной шине и через конденсатор к общей шине,Источники информации,принятые во внимание при экспертизе1 Э1. Патент США.М 3974402,кл. Н 03 К 19/08, опублик. 13,02.76.ф 2. Акцептованная заявка ЯпонииМф 52-17705, кл. Н 03 К 19/00,1 1977.

СмотретьЗаявка

2709422, 08.01.1979

ПРЕДПРИЯТИЕ ПЯ А-7438

АРТЕМЕНКО ВИКТОР АЛЕКСАНДРОВИЧ, БЕЛЫЙ-ТКАЧ ЕВГЕНИЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: H03K 19/08

Метки: логического, уровня

Опубликовано: 07.12.1980

Код ссылки

<a href="https://patents.su/3-786006-preobrazovatel-logicheskogo-urovnya.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь логического уровня</a>

Предыдущий патент: -входовой универсальный многозначный логический элемент

Следующий патент: Устройство запрета

Случайный патент: "зубная щетка "валентина"