Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

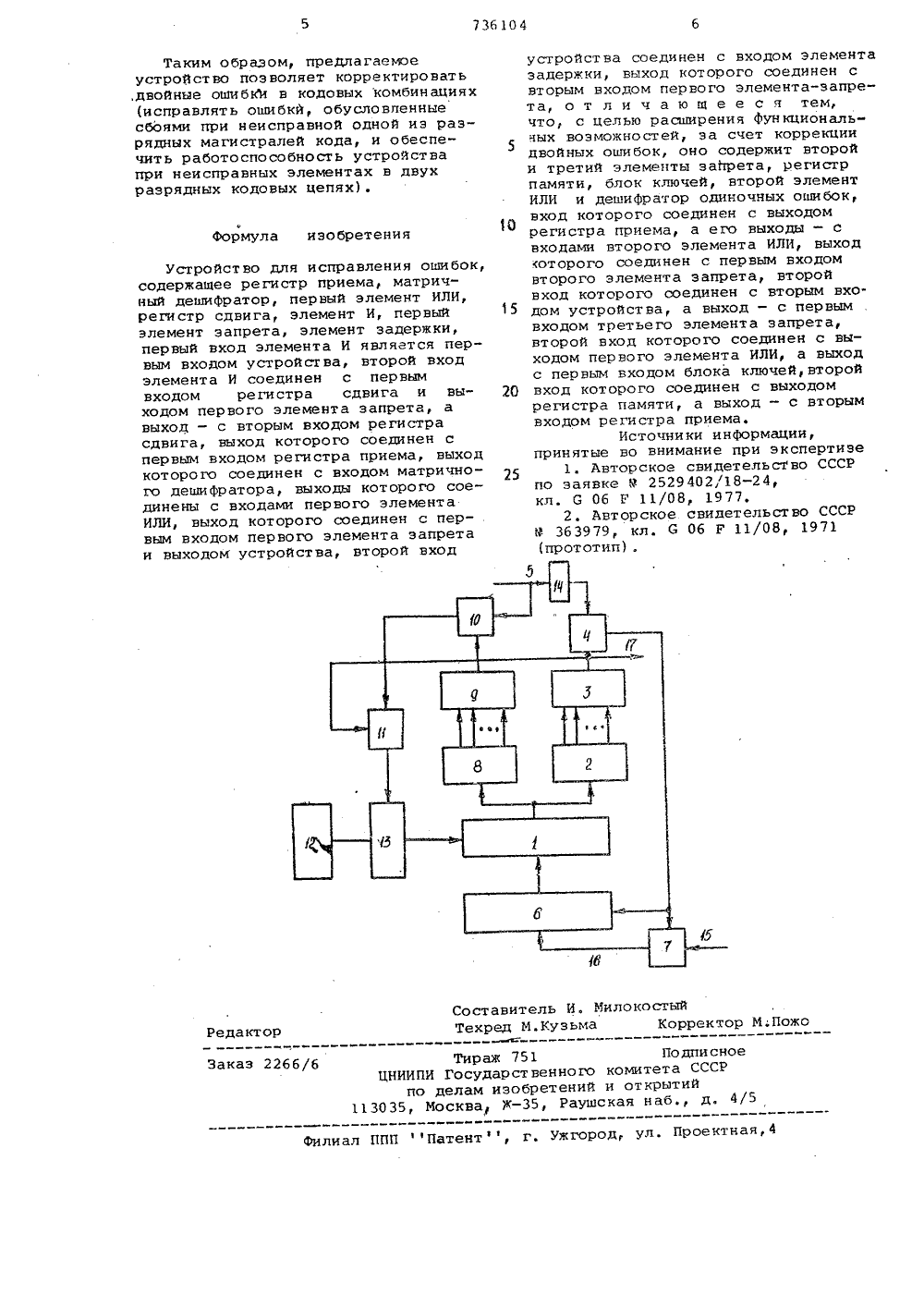

Союз Советских Социалистических РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(23) Приоритет Государственный комитет СССР по дедам изобретений и открытий(54) УСТРОЙСТВО ДЛЯ ИСПРЛВЛЕНИЯ ОШИБОК Изобретение относится к вычислительной технике и может быть использовано в устрой ст вах пер ера бог ки и передачи дискретной информации,Из ве ст но у строй ст во, содержащее реги стр приема, дв ухст упен чатую матрицу и элементы ИЛИ, позволяющее эффективно корректировать одиночные ошибки (1.Недостаток устройства - невозмож ность исправления двойных ошибок.Наиболее близким к изобретению является устройство, содержащее регистр приема, матрицу, регистр сдвига, элемент И, элемент ИЛИ, элемент 15 запрета, элемент фиксации окончания приема кодовой комбинации, выход которого соединен с первым входом элемента запрета, второй вход которого соединен с выходом элемента 20 ИЛИ, а выход с первыми входами регистра сдвига и элемента И, второй вход которого соединен со входом устройства, третий вход - с выходом регистра сдвига, а выход - с вторым 25 входом регистра сдвига, группа выходов последнего соединена с группой входов регистра приема, выходы которого соединены с соответствующими входами матрицы, выходы кото рой соединены со входами элементаИЛИ,Не дост ато к устрой ст ва - возмОжность исправления лишь одиночныхоши бок,Цель изобретения - расширениефункциональных возможностей, заключающихся в коррекции двойных ошибок.Поставленная цель достигается тем,что в устройство, содержащее регнстрприема, матричный дешифратор, первыйэлемент ИЛИ, регистр сдвига, элементИ, первый элемент запрета,элеменгзадержки, первый вход элемента Иявляется первым входом устройства,второй вход элемента И соединен спервым входом регистра сдвига ивыходом первего элемента запрета, авыход - с втбрым входом регистрасдвига, выход которого соединен спервым входом регистра приема, выходкоторого соединен с входом матричного дешифратора, выходы которого,соединены с входами первого элементаИЛИ, выход которого соединен с первым входом первого элемента запретаи выходом усгройства, второй входустройства соединен с .входом элемента задержки, дополнительно введе.ны второй и третий элементы запретарегистр памяти, группу ключей, второй элемент ИЛИ и дешифратор одиночных ошибок, вход которого соединенс выходом регистра приема, а еговыходы - с входами второго элемента,ИЛИ, выход которого соединен с первым входом второго элемента запрета,второй вход которого соединен с вторым входом устройства, а выход - спервым входом третьего элементазапрета, второй вход которого соединен с выходом первого элемента ИЛИ,а выход - с первым входом группыключей, второй вход которого соединен с выходом регистра памяти, авыход - с вт орым входом р е ги страприема,На черт еже при веден а структ урн аясхема устройства,Устройст во содержит ре ги стр 1 приема, матричный дешифратор 2, первыйэлемент ИЛИ 3, первый элемент 4 запрета, шину 5 начало коррекции,регистр б сдвига, элемент И 7, дешифратор 8 одиночных ошибок, второйэлемент ИЛИ 9, - второй и третий элемзнты 10 и 11 запрета, регистр 12памяти, группу ключей 13, элемент 14задержки, шину 15 тактовых импупьсов,сдвигающую шину 16 и шину 17 окончание коррекции.Дешифратор 8 одиночных ошибок построен аналогично матричному дешифратору 2, представляющий собой фактически дешифратор рабочих кодовыхкомбинаций.Регистр 12 памяти предназначендля запоминания номера разряда, искажение информации в котором наблюдается уст ойчи во, Регистр 12 кодо вымяшинами через ключи 13 соединен .сРегистром 1 приема. Управляющий сигнал на открытие ключей 13 поступаетиз третьего элемента 11 запрета,Элемент 14 задержки предназначендля задержки сигналаначало коррекциина время, необходимое дляпересылки содержимого регистра 12памяти на регистр приема в случае,когда в коцовой комбинации содержитсядва и более искаженных символа.Устройство работает следующим об-разом.Перед приемом кодо вой комби к ации ре ги стр 1 приема уст ан авли вает ся в ноль. Если принятая кодовая комбинация ошибки не содержит, то на выходе матричного дешифратора 2 возбуждается шина, соответствующая принятой рабочей кодовой комбинации. На выходе элемента ИЛИ 3 формируется единичный сигнал, который запрещает прохождение сигналаначало коррекциичерез элемент запрета, На шике 17окончание коррекцииустанавливается единичный сигнал,Пусть поступила кодовая комбинация, имеющая одиночную ошибку, В этом случае возбуждается одна из шик20 25 ЗО 40 дешифратора 8 одиночных ошибок 8, навыходе элемента ИЛИ 9 формируется(единичный сигнал, который запрещаетпрохождение сигналаначало коррекциичерез элемент 10 запрета. Сигналначало коррекциипроходитчерез элемент 4 запрета, переводитв единичное состояние младший разряд регистра б сдвига и обеспечивает прохождение тактовых импульсовчерез элемент И 7. Тактовые импульсы,поступающие по шине 16 как импульсысдвига, обеспечивают перемещениеединицы в регистре сдвига, последовательно инвертируя содержимое разрядоврегистра 1. Каждый приемный элемент регистра 1 изменяет свое состояние при записи 1 в связанный с ним разряд регистра сдви га и воз вращает ся в исходное состояние при записи в этот разряд О, Как только в результате этой корре кции будет получен правильный код (рабочая кодовая комбинация), возбуждается одна из шин матричного деши фр атора 2, н а выходе ло гиче ской схемы ИЛИ 3 устанавливается единичный сигнал, а ка выходе элемента 4 запрета - нуле ной си гнал. Последний прекращает прохождекие тактовых импульсов с шины 15 через элемент И ка шину 16 сдвига. На шикеокончание коррекцииуст анавли вается единичный си гн ал. Если ошибка в одНом и том же разряде повторяется несколько раз, что свидетельствует о наличии устойчивого отказа (неиЕ- правности кодовой шины), то в соответствующий разряд регистра 12 памяти заносится единица.При наличии единицы в одном из разрядов регистра 12 памяти и отсутствии ошибок в кодовой комбинации или в других разрядах кодовой комбинации, работа устройства не отличается от изложенного выше. В том случае, когда имеет местодвойная ошибка, ни одна из шин матричного дешифратора 2 и дешифратора8 не возбуждаются. Сигналначалокоррекциис шины 5 через элементы10 и 11 запрета поступает на управляющие входы ключей 13. Ключи 13открываются и содержимое регистра 12памяти поступает в регистр 1 приемных элементов, изменяя состояниесоответствующего элемента памяти(выполняется операция поразрядногосложения по модулю 2). В результатедвойная ошибка сводится к одиночной.Этот же сигкал с шины 5, задержанный элементом 14 задержки навремя коррекции кода в регистре 1,поступает через элемект 4 запрета нарегистр 6 сдвига и схему И 7. Далееустройство работает так же как и приналичии одиночной ошибки в кодовойкомбинации,736 104 Таким образом, предлагаемое устрой ст во поз воляет корр е ктиро ват ь ,двойные ошибКИ в кодовых комбинациях (исправлять ошибкй, обусловленные сбоями при неисправной одной из разрядных магистралей кода, и обеспечить работоспособность устройства при неисправных элементах в двух разрядных кодовых цепях). Устройство для исправления ошибок, содержашее регистр приема, матричный дешифратор, первый элемент ИЛИ, регистр сдвига, элемент И, первый элемент запрета, элемент задержки, первый вход элемента И является первым входом устройства, второй вход элемента И соединен с первым входом регистра сдвига и выходом первого элемента запрета, а выход - с вторым входом регистра сдвига, выход которого соединен с первым входом регистра приема, выход которого соединен с входом матричного дешифратора, выходы которого соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента запрета и выходом устройства, второй вход Составитель И. МилокостыйТехред М.Кузьма Корректор М.Пожо едакто Тираж 751сударст венного кам изобретений и ва 7-35, Раушск каз 2266/ Подпимитета ССоткрытийя набс д ое ПНИИПИ Г по де 30 35, Мос4/5 ППатент ф ф, г, Ужгород, ул. Проектная л Формула изобретения устройства соединен с входом элементазадержки, выход которого соединен свторым входом первого элемента-запрета, отличающееся тем,что, с целью расширения функциональяых воэможностей, за счет коррекциидвойных ошибок, оно содержит второйи третий элементы за)трета, регистрпамяти, блок ключей, второй элементИЛИ и дешифратор одиночных ошибок,вход которого соединен с выходомрегистра приема, а его выходы - свходами второго элемента ИЛИ, выходоторого соединен с первым входомвторого элемента запрета, второйвход которого соединен с вторым входом устройства, а выход - с первымвходом третьего элемента запрета,второй вход которого соединен с выходом первого элемента ИЛИ, а выходс первым входом блока ключей, второйвход которого соединен с выходомрегистра памяти, а выход - с вторымвходом регистра приема,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельсвво СССРпо заявке Р 2529402/18-24,кл. С 06 Г 11/08, 1977,2. Авторское свидетельство СССРФ 363979 кл. 6 06 Р 11/08, 1971

СмотретьЗаявка

2584890, 28.02.1978

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

БАРАНОВ ИГОРЬ АЛЕКСЕЕВИЧ, БРИТВИН АНАТОЛИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/08, H03M 13/51

Метки: исправления, ошибок

Опубликовано: 25.05.1980

Код ссылки

<a href="https://patents.su/3-736104-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Устройство для получения диагностических тестов логических блоков

Следующий патент: Устройство для сопряжения основной памяти с процессором

Случайный патент: Грузоподъемное устройство