Демодулятор сигналов с фазоразностной модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

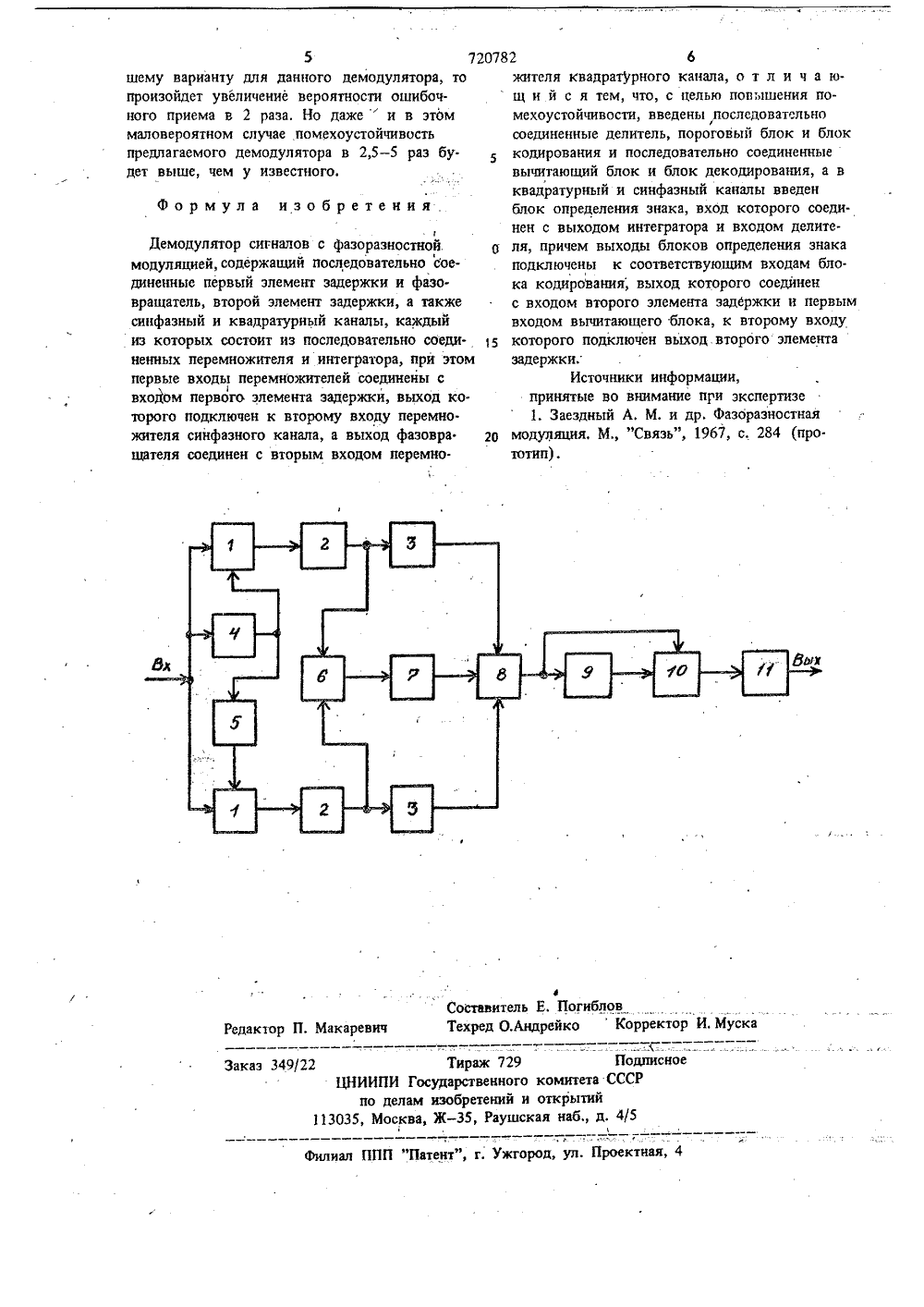

Союз СоветскихСоцивлкстыческихРеспублик 0782 рстзвнхьй комитет СССР 23 о левам нзобратеи н втхрытнйИзобретение относится к связи и можетиспользоваться в каналах связи с неопределен.ной частотой и фазой.Известен демодулятор сигналов с фазораз.постной модуляцией, содержащий последователь 5но соединенные первый элемент задержки и.фазовращатель, второй элемент задержки, а также синфазный и квадратурный каналы, каждыйиз которых состоит иэ последовательно соеди.пенных перемножителя и интегратора, при этом16первые входы перемножителей соединены свходом первого элемента задержки, выход которого подключен к второму входу перемножителя синфазного канала, а выход фазовра.щателя соединен с вторым входом перемно.15жителя квадратурного канала 1),Однако в известном демодуляторе второе"перемножение сигнала после интегратора с последующим суммированием результата перемножения двух каналов приводит к снижениюотношения сигнал/помеха на выходе сумматора,чЫ приводит к снижению помехоустойчивости.Цель изобретения - повышейие помехоустойживости,Для достижения указанной цели в демоду.лятор сигналов с фаэоразностной модуляцией,содержащий последовательно соединенные пер.вый элемент задержки и фазовращатель, вто.рой элемент задержки, а также синфазный иквадратурный каналы, каждый из которыхсостоит из последовательно соединенных перемножителя и интегратора, при этом первыевходы перемножителей соединены с входомпервого элемента задержки, выход которогоподключен к второму входу перемножителясинфаэного канала, а выход фазовращателв,соединен с вторым входом перемножителяквадратурного канала, введены последовательно соединенные делитель, пороговый блок иблок кодирования и последовательно соединенные вычитающий блок и блок декодирования,а в квадратурный и синфаэный каналы введенблок определения знака, вход которого сое..инеи с выходом интегратора и входом делителя, причем выходы блоков определениязнака подключены к соответствующим входамблока кодирования, выход которого соединенс входом второго элемента задержки и пер.4о7К, сом Ч 720782 3вым входом вычигающего блока, к второмувходу которого подключен выход второгоэлемента задержки.На чертеже представлена структурная электрическая схема предложенного демодулятора.Демодулятор содержит синфазный и квадратурный каналы, каждьш из которых включает перемножитель 1, интегратор 2 и блок 3определения знака. Демодулятор содержит так.же первый элемент 4 задержки, фазовращатель 105, делитель 6, пороговый блок 7, блок 8 кодирования, второй элемент 9 задержки вычитаюший блок 10 и блок 11 декодирования.Демодулятор работает следующим образом,Известно, что информационным параметром 5цри фазоразностной модуляции является раз-,ность фаз Лр = рп - р где р,- фазасигнала (и - 1)-ной посылки; р - фаза сигнала. ц-ной посыЛки.Вычисление Ьр в демодуляторе сводится к 20определению знаков созЛу и а 1 пЛд через скалярное произведение( ХХ,) =Х ХЮХ,(И дЛ.=. сомЧ //7////7,/гд Х- принятая п-ная посылка в виде 25вектора;Х// в , норма вектора. ХгЕсли один из векторов например, Х по.вернуть на ПЙ и обозначить его через Х,то -:Ю - Эф, - Ф -Ф 30Х Х )=/Х /Х /ьчЧ, Таким образом, вычислив на выходах инте:Изаторов 2 скалярные произведения (ХХ,) и (Х,Х) и взяв отношение йхмодулей, можно получить значение тдЬр и по Э 5нему, с помощью знаков скалярных произведений, восстановить непосредственное значениеЬр, которое будет соответствовать некоторомупереданному элементарному символу. Сигнал,проходящий ца вход демодулятора, поступает 40на вход перемножителец 1 и элемента 4 задержкц. Элемент 4 задержки осуществляетзадержку сигнала на время, равное длительюсти одной элементарной посылки. Выходэлемента 4 -задержкИ соединен"со "входной " 45перемцожителя 1 сицфаэного канала непосред ственно, а со входом перемножителя 1 квадратурцого канала через фаэовращатель 5 наП/2. Перемножители 1 и включенные последо.вательцо с ними интеграторы 2 выполняют опе.рщию скалярного умножения (Хх Хд ),Напряжение на выходе интегратора 2 синфазного канала будет равно//Х /Х //соььа ца выходе интегратора 2 квадратурногоканала ХХ ъщЧ . Делитель 6выполняет операциюделейия Напряжение, пропорциональное тдЬр, пода.ется на пороговый блок 7, где выставляетсяряд фиксированных порогов, величина которыхсоответствует определенным значениям Ьр.Число порогов определяется заданной точ.ностью определения Ьр. Блок 8 кодированияс учетом знаков скалярных произведений,которые вырабатывают блоки 3 определениязнаков, каждому значеншо ставит в соответствие." "двоичное чиСло, которое поступает на вычитающий блок 10 и элемент 9 задержки.Элемент 9 задержки хранит это число до прихода следующего. Вычитающий блок 10 вы.числяет вторую разность фаз, которая поступает в блок 11 декодирования, В блоке 11каждому значению вторых разйостей фаз ставится, в соответствие определенный двоичныйсимвол принятой информации.Помехоустойчивость демодулятора при воздействии флуктуационной помехи можнооценить уменьшением отношения сигнал/номе;ха на выходе сумматора демодулятора посравнению с отношением сигнал/помеха навыходе интеграторов. Это уменьшение составляет не менее, чем, в т 2 раз, что приводит к значительному увеличению вероятности ошибки (приблизительно в 5 - 10 раз),.Уменьшение сигнал/помеха в прототипе вызвано вторичным перемножением напряжений,снимаемых с выходов интеграторов, соответ.ствующих проекциям сигнала синфазного иквадратурного каналов для текущей и пре.дыдущей посылок, и последующим суммированием результатов перемножения по двумканалам,В предлагаемом демодуляторе решение о первой разности фаз выносится на основании значения тдЬр, вычисленного при помощи деления проекции сигнала в синфазном кана. ле на проекцию сигнала в квадратурном канале, Значения проекций соответствуют на.пряжениям на выходах интеграторов соответствующих каналов. Решение о первой разности фаз выносится в виде знака блоком кодирования, а дальнейшая обработка сигнала сво. дится к обработке знаков, Благодаря тако.мупостроению схемыдемодулятора второе перемножение и суммирование сигналов, сни. маемых с интеграторов и соответствующих текущей и предыдущей посылкам, исключает. ск, а аналопщная операция со знаками может привести только лишь к сдваиванию одиночных ошибок, или к частичному исправлению сгруппированных ошибок. Если предположить все о 1 цибки одиночными, что соответствует наихуд.4Составитель Е. ПогибловРедактор П, Макаревич Техред О,АндрейкоКорректор И, Муска сное Подпиитета СССрытийаб д, 4/5 каэ 349/22 Тираж 729 ЦНИИПИ Государственного по делам изобретений и 113035, Москва, Ж, Раушс. Проектная, 4 ал ППП "Патент", г. Ужгоро 5 7 шему варианту для данного демодулятора, то произойдет увеличение вероятности ошибочного приема в 2 раза, Но дажеи в этом маловероятном случае помехоустойчивость предлагаемого демодулятора в 2,5 - 5 раз бу. дет выше, чем у известного. Формула изобретения Демодулятор сигналов с фазоразностной модуляцией, содержащий последовательно соединенные первый элемент задержки и фазовращатель, второй элемент задержки, а также синфазный и квадратурный каналы, каждый из которых состоит из последовательно соединенных перемножителя и интегратора, при этом первые входы перемножителей соединены с входом первого элемента задержки, выход ко. торого подключен к второму входу перемножителя синфаэного канала, а выход фазовра. щателя соединен с вторым входом перемно 20782 6жителя квадратурного канала, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости, введены последовательно/соединенные делитель, пороговый блок и блоккодирования и последовательно соединенныевычитающий блок и блок декодирования, а вквадратурный и синфазный каналы введенблок определения знака, вход которого соединен с выходом интегратора и входом делите.о ля, причем выходы блоков определения знакаподключены к соответствующим входам блока кодирования, выход которого соединенс входом второго элемента задержки и первымвходом вычитающего блока, к второму входу 15 которого подключен выход второго элементазадержкиИсточники информации,принятые во внимание при экспертизе1. Заездный А. М. и др. Фазоразностная гО модуляция, М., "Связь", 1967, с, 284 (прототип).

СмотретьЗаявка

2636912, 03.07.1978

ПРЕДПРИЯТИЕ ПЯ Р-6510

ЕВДОКИМОВ ВЛАДИМИР КУЗЬМИЧ, СИДОРОВ НИКОЛАЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: H04L 27/227

Метки: демодулятор, модуляцией, сигналов, фазоразностной

Опубликовано: 05.03.1980

Код ссылки

<a href="https://patents.su/3-720782-demodulyator-signalov-s-fazoraznostnojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор сигналов с фазоразностной модуляцией</a>

Предыдущий патент: Способ формирования сигналов относительной фазовой манипуляции

Следующий патент: Способ параллельной передачи дискретной информации многочастотными сигналами

Случайный патент: Гидроцилиндр