Устройство синхронизации по битам систем передачи цифровой информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

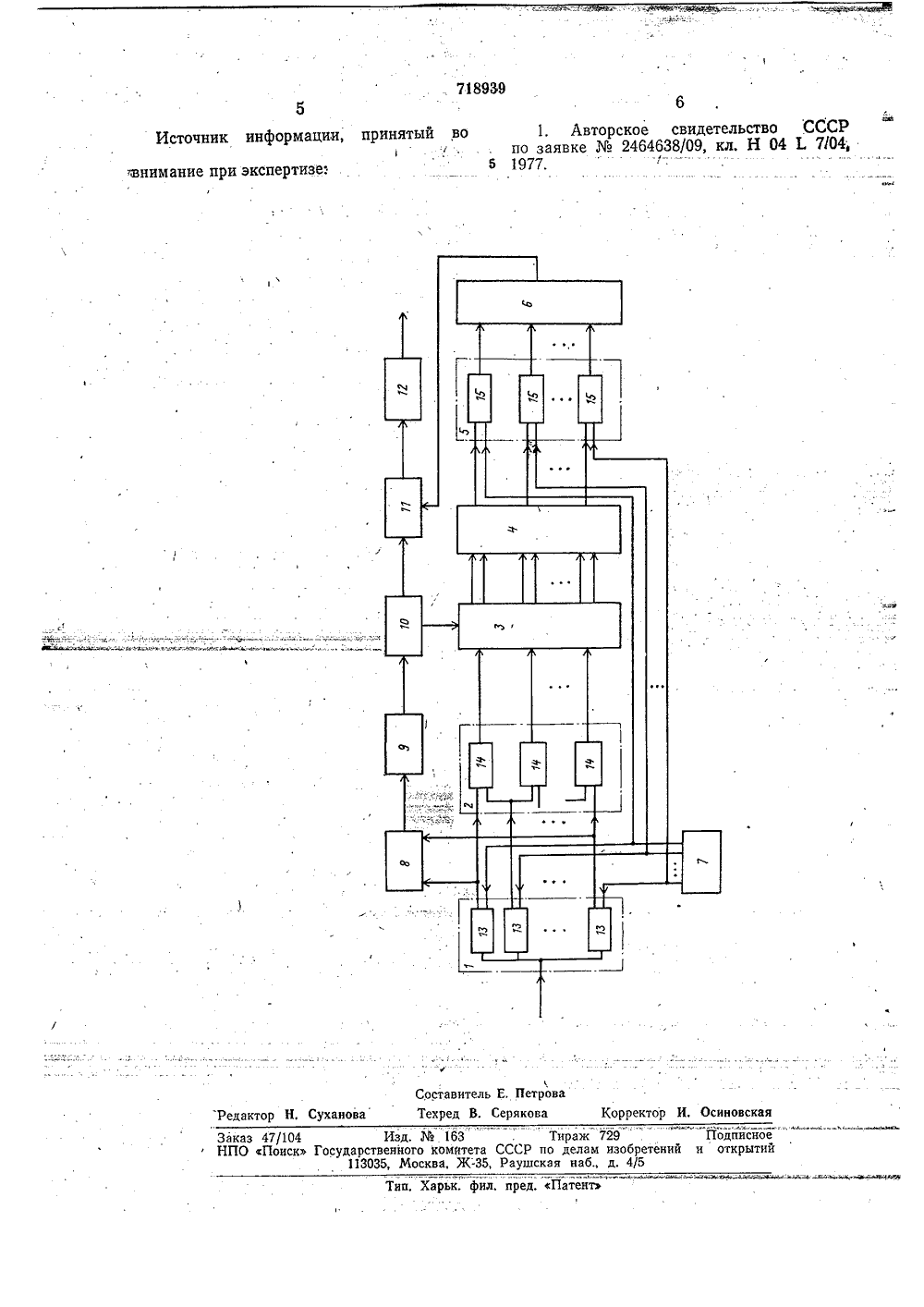

ИЗОБРЕТЕНИЯ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 61) Дополнит 22) Заявлено ельное к альт.сви 22,06.78 (21) 26 213/18-09 1. 7/04 присоединением заявки Государственный комитет СССР5 елам изобретении и открытий я 28.02.8 45) Дата опубликования описа Авторыобретени ко и А, Г, Гонч) Заявитель Всесоюзный заочный электротехнический институт связ 54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО БИТАМ ИСТЕМ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ язи и может едачи цифванием синшеств ю их Изобретение относиться к свиспользоваться в системах перровой информации с использохропоследовательностей, пред у щ информационным битам.5Известно устройство синхронизации по битам систем передачи цифровой информации, содержащее блок корреляторов, выходы которых подключены к входам блока вычитания, причем два соответствующих 10 выхода блока корреляторов подключены к входам сумматора, причем выходы генератора опорного сигнала подключены к дру; гим входам блока корреляторов и входам блока элементов И, а также пороговый 15 блок 11.Однако известное устройство обладаетзначительной сложностью.Целью изобретения является упрощение устройства путем уменьшения числа корре ляторов.Для этого в устройство синхронизации по битам систем передачи цифровой информации, содержащее блок корреляторов, выходы которых подключены к входам блока 25 вычитания, прячем два соответствующих выхода блока корреляторов подключены к входам сумматора, причем выходы генератора опорного сигнала подключены к другим входам блока коррелятороВ и входам 30 блока элементов И, а также пороговыиблок, введены блок памяти, блок дешифраторов, элемент ИЛИ, элемент И, триггер ивыходной формирователь, причем выходыблока вычитания через последовательносоединенные блок памяти, блок дешифраторов, блок элементов И, элемент ИЛИ иэлемент И подключены к входу выходногоформирователя, а выход сумматора черезпоследовательно соединенные пороговыйблок и триггер подключен к другому входу элемента И, а другой выход триггераподключен к другому входу блока памяти, -.-.:,На чертеже приведена структурная электрическая схема предложенного устройства,Устройство синхронизации по битам систем передачи цифровой информации содержит блок 1 корреляторов, блок 2 вычитания, блок 3 памяти, блок 4 дсшифраторов,блок 5 элементов И, элемент ИЛИ б, генератор 7 опорного сигнала, сумматор 8,пороговый блок 9, триггер 10, элемент И11 и выходной формирователь 12.Кроме того, в блок 1 входят корреляторы 13, в блок 2 - компараторы 14, в блок5 - элементы И 15. Устройство работает следующим обра-, -ЩЩфящф .71В исхбдном состояниями на вход устройст-ва поступают обусловленные шумом"посылки со случайной длительностью и фазой.Выходные напряжения корреляторов 13блока 1, пропорциональные взаимнокорреляционным функциям таких шумовых пав сьйоки"опбрййХ сйгЗГаЛов; посТйаюйих" свыходов генератора 7, имеют малую величйну.При"-поступленйи на вход устройствасинхропоследовательности на выходе каждого коррелятора 13 блока 1 начинает на "раСтать напряжение,"пропорцйональйое абсолютной величине взаимнокорреляционной фуйкции входной синхропоследовательности " " и опорного колебанй 3 Г 3 аййогоЙбфййФора13., Велйчина вьЫЬдногонапряжеййя "коррелятора 13 меняется взависимости от рассогласования по фазе бита прицимаемой синхропоследовательности и опорной сйн"" хропоИФбва 1 ельносУЙ"=1 аййбго-хоррелятора 13. Поскольку поступающие на корреляторы 13 опорные колебания ймеют определенную задержку по фазе бита относительно друг друга, то величины выходных напряжений корреляторов 13 в зависимости от фазы бйта йрййимаемои сийхропоследо" вательноСти относительно опорйого сигналаменяются определенным образом,однознач-но соответствующим взаимным"задержкам по фазеВыходные напряжения соседних корреляторов 13 блока 1 сравниваются между собой компараторами 14 блока 2, причем, если выходное напряжение 1-го коррелятора 13 больше выходного напряжения + 1-гокоррелятора 13, то сравнивающий их компаратор 14 вырабатывает сигнал 1, а в про тйвоположйом случае - сигнал О, Приизменении фазы бита входной скнхройосле"довательности отнооительйо первого "бйорногосигнала от О до Т на"вйбодаМ Лйа"- раторов 14 блока 2 вырабатываются соот" - - "Ъетствующиевеличине"рассогла сов айиядво"ичные парал.чельные коды;-.: .-,:;.=.: - =:." ==.Эти коды поступают в блок 3; а=с=йего="- 1 в блок 4, который определяет номер тогоэлемента И 15 блока 5, который в данный момент должен быть подключен к элементу ИЛИ б.На входы элементов И 15 блока б подаются опорные сигналвг с "соответствующих выходов генератора 7, различные по фазе бита в пределах от О до Т, В результате к входу элемента И 11 подключается тот опорный сигнал, "моменты смены симво"лов вЧотороммйййййй но оЪЯйчаФ"ЛГИМоментовсменысимволов во входной син- хропоследовательй 5 с"г.: " -===-. .= -Сумма выходных сигналов первого и У-гокорреляторов 13 блока 1 не зависит от фа- зы бита принимаемой синхропоследователь 4"ности; "азависит только от отношения сигнал/шум в принимаемой синхвопосЛедовательности, поэтому при достижеяии выходным -напряжением сумматора 8" определенйого "уровйя пороговый блок 9 вырабатывает сигнал 1, который перебрасывает триггер 10 вединичное состояние. Выход единичного плеча триггера 10 управляет элементом И 11, который с этого момента. на чинает пропускать синхропоследовательность определенной фазы на вход выходного формирователя 12, осуществляющегоформирование тактовых импульсов, синхронизированных с началом каждого бита.С момента переброса триггера 10 ведФИМное состояние выходной сигнал с другого выхода триггера 10 (нулевое плечо) управляет блоком 3, который запоминает записанный в нем код до конца сеанса 20 связи. По окончании сеанса связи триггер10 перебрасывается в нулевое состояние и устройство опять находится в ожидании следующего сеансасвязи,Таким образом, до начала сеанса связиобеспечивается режим, когда устройство не вырабатывает тактовых импульсов, и только после накопления входного аигнала синхропоследовательности, когда синхронный 30 по фазе битов режим устанавливается сбольшой вероятностью, устройство генери рует тактовые импульсы, необходимые дляприема цифровой информации.Предложенное устройство обеспечивает З 5 возможйость получения высокой точности"синхройизации, помехоустойчивости и быстродействия при коротких синхропоследовательностях.40, Формула изобретеннаяУстройство синхройизации по битам систем передачи цифровой информации, содержащее блок корреляторов выходы кото рых подключены к входам блока вычитания,причем два соответствующих выхода блокакорреляторов йодключейй квходам сумма.тора, причем выходы генератора опорного сйгнала подключены к другим входам бло ка корреляторов и входам блока элементовИ, а также пороговый блок, о т л и ч а ющ ее ся тем, что, с целью упрощения устройства путем уменьшения числа корреляторов, в него введены блок памяти, блок дешифраторов, элемент ИЛИ, элемент И, триггер и выходной формнрователь, причем выходы блока вычитания через последова" тельно соединенные блок памяти блок дешифраторов, блок элементов И, элементИЛИ и элемент И подключены к входу выходногоформирователя, а выход сумматора через последоватемьйо "соединенные пороговый блок "и триггер подключен к другому входу элемента И, а другой выход триггера 05 подключен к другому входу блока памяти,718939 оставитель Е. ПетровТехред В. Серякова Корректор И, О вская анов дактор Изд. Ив 163 . Тсударственного комитета СССР по 113035, Москва, Ж, Раушска Подпйсноеиоткрытий аж 729елам изобретеннаб д. 4/5 каз 47/104ПО Поиск ип. Х ил. пред, Патент Источник информации, принятый во/квнимание при экспертизе,3 61. Авторское свидетельство СССРпо заявке2464638/09, кл. Н 04 1, 704, 5 1977.

СмотретьЗаявка

2634213, 22.06.1978

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

МУЛЕНКО СЕРГЕЙ ГРИГОРЬЕВИЧ, ГОНЧАРОВ АЛЕКСЕЙ ГАВРИЛОВИЧ

МПК / Метки

МПК: H04L 7/04

Метки: битам, информации, передачи, синхронизации, систем, цифровой

Опубликовано: 29.02.1980

Код ссылки

<a href="https://patents.su/3-718939-ustrojjstvo-sinkhronizacii-po-bitam-sistem-peredachi-cifrovojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство синхронизации по битам систем передачи цифровой информации</a>

Предыдущий патент: Устройство для формирования импульсов синхронизации

Следующий патент: Ячейка асинхронного распределителя

Случайный патент: Способ посола мясаjj иаш; . ьо44 tkxf«hrr. kafi €: lt; "к; тгил