Дельта-модулятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

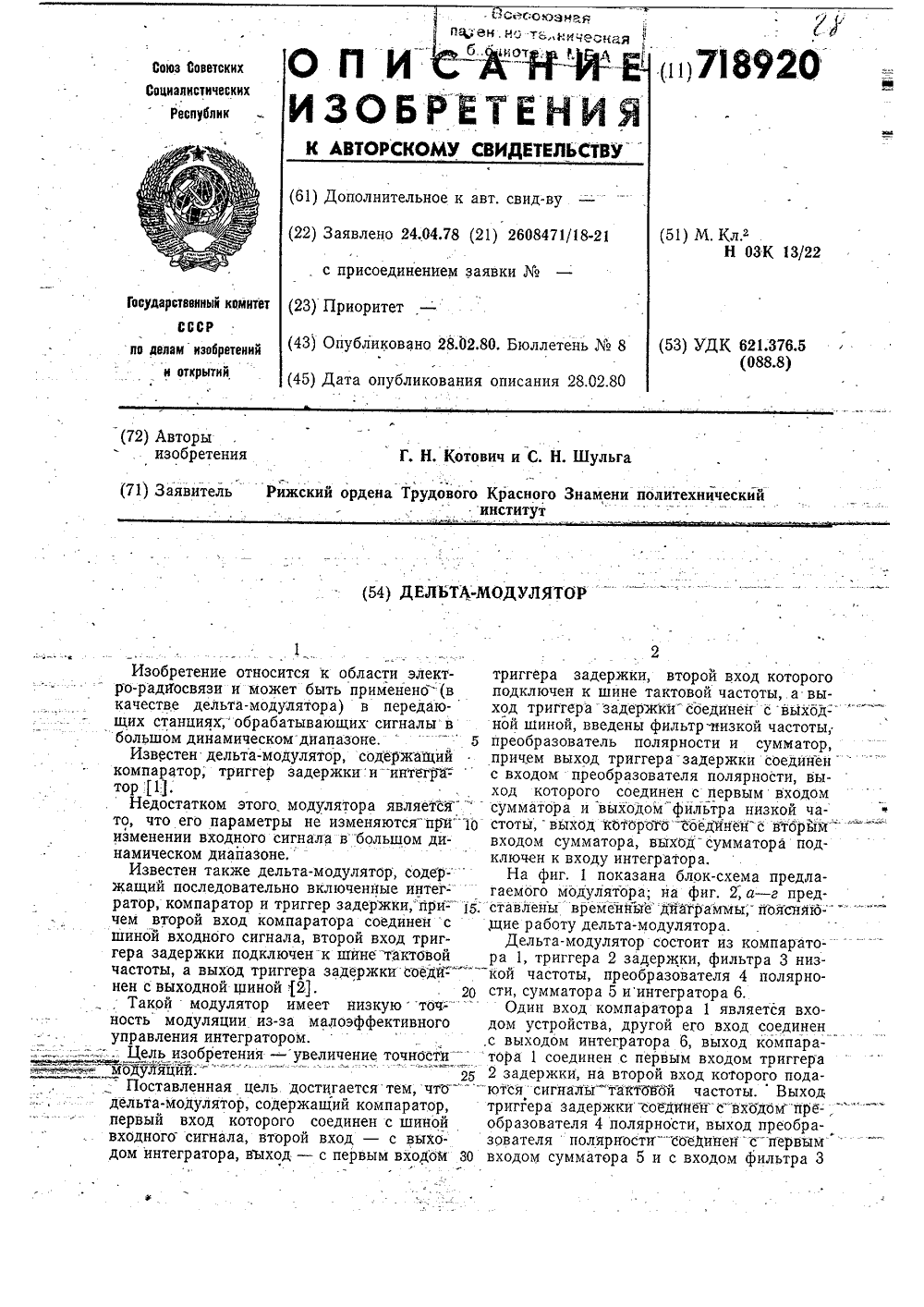

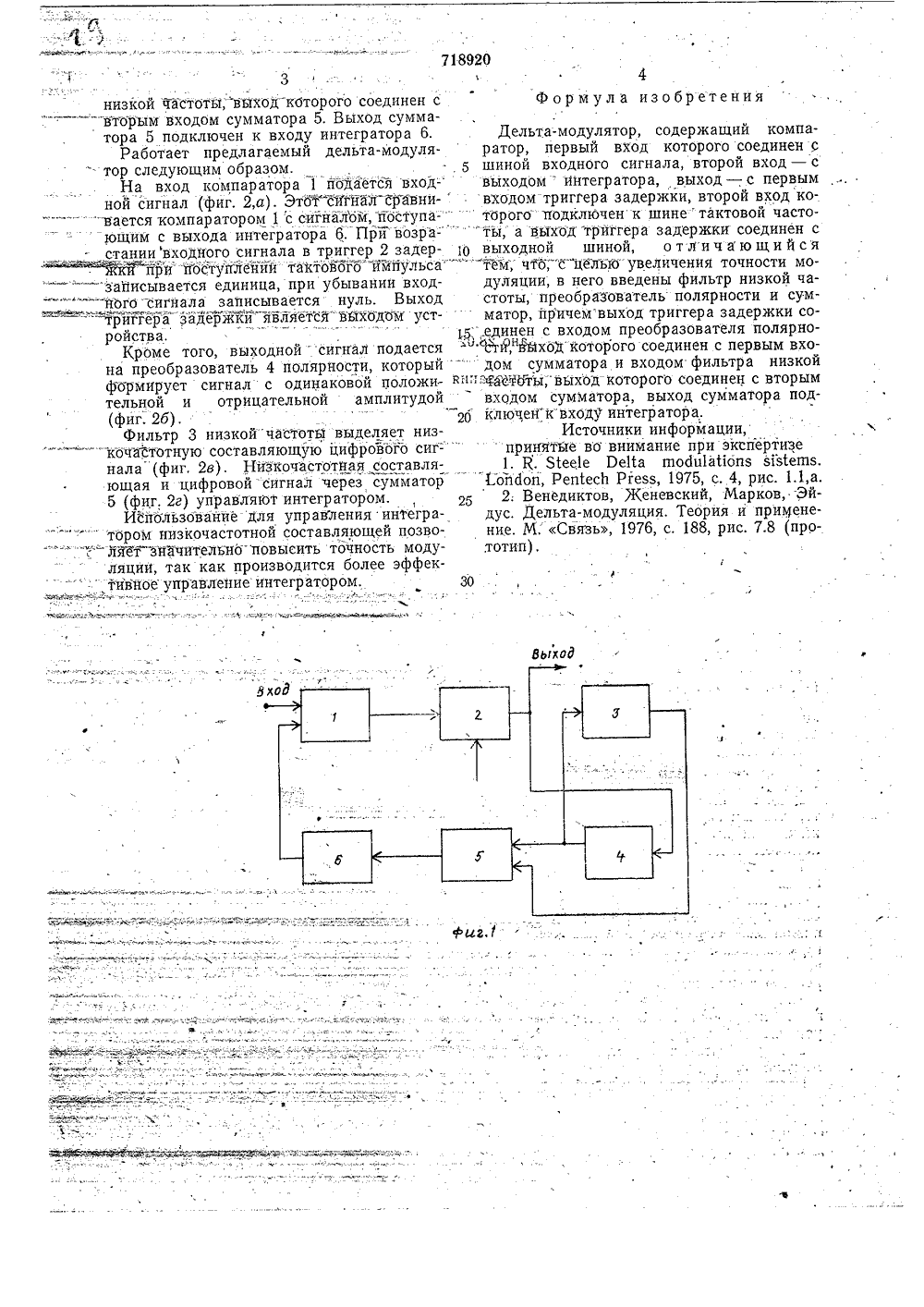

ет 43) Опубликовано 28.02.80, Бюллетень8 45) Дата опубликования описания 28.02.8072) Авторы изобретени Г. Н. Котович и С. Н. Шульга Рижский ордена Трудового Красного Знамени политехнический институт(54) ДЕЛЪТА-М ТОР 12кЪИзобретение относится к области элект- триггера задержки, второй вход которогоро-радтосвязи и может быть применено-:(в подключен к шине тактовой частоты, а выкачестве дельта-модулятора) в передаю- ход триггера задержки споединен с выход-""щих станцияхобрабатывающих сигналы в ной шиной, введены фильтр-низкой частоты,большом динамическом диапазоне," 5 преобразователь полярности и сумматор,Известен дельта-модулятор, содержащий причем выход триггера-задержки соединенкомпаратор; триггер задержкии интегра=с входом преобразователя полярности, вытор 11. ход которого соединен с первым входомНедостатком этого, модулятора является "сумматора и выходом фильтра низкой чато, что его параметры не изменяютсяпрн 10 стоты, выход кЬторогб соединен с вторым=изменении входного сигнала в большом ди- входом сумматора, выход сумматора поднамическом диайазоне.ключен к входу интегратора,Известен также дельта-модулятор, содер-На фиг, 1 показана блок-схема предлажащий последовательно включенные интег- гаемого модулятора; на фиг. 2,а - г предратор, компаратор и триггер задержки,при- -л. ставлены временньге дЪгаграммы поясняю-чем второй вход компаратора соединен с щие работу дельта-модулятора.шиной входного сигнала, второй вход триг- Дельта-модулятор состоит из компарато-" " " "- гера задержки подключен к шине"тактбвой ра 1, триггера 2 задержки, фильтра 3 низчастоты, а выход триггера задержкисоедй-" =кой частоты, преобразователя 4 полярнонен с выходной шиной 121. 20 сти, сумматора 5 иинтегратора 6.Такой модулятор имеет низкуюточ:-" "Один вход компаратора 1 является вхоность модуляции из-за малоэффективного дом устройства, другой его вход соединенуправления интегратором.,с выходом интегратора 6, выход компараЦель изобретения - увеличение точности-" тора 1 соединен с первым входом триггерамквЖ" модуляций --"яд 2 задержки, на второй вход которого пода.Поставленная цель достигается тем, чтп" ются -сигналы-таитбпй частоты, Выходдельта-модулятор, содержащий компаратор, триггера задержки соединей-свходом"пре-,"=.первый вход которого соединен с шиной образователя 4 полярности, выход преобравходного сигнала, второй вход - с выхо- зователя полярноспти"соединен с"первымдом интегратора, вЪход - с первым входоМ 30 входом сумматора 5 и с входом фильтра 37189203, 4низкой частоты;вяход которого соединен с Формула изобретения "вторым входом сумматора 5. Выход сумматора 5 подключен к входу интегратора 6. Дельта-модулятор, содержащий компаРаботает предлагаемый дельта-модуля- ратор, первый вход которого соединен с . тор следующим образом 5 шиной входного сигнала, второй вход - сНа вход компаратора 1 йадается вход- выходом интегратора, выход - с первымной сигнал (фиг. 2,а). Зтобтсйгнал сравни-входом триггера задержки, второй входко"вается компаратором 1 с сигналом, -поступа- - торого подключен к шинетактовой частоющим с выхода интегратора 6. Привозра- "ты, а выход триггера задержки соединен с станин входного сигнала в триггер 2 задер выходной шиной, о т ли ч а ю щ и й с я Ъй фюйуЮВВ ВВАЛЮяйг": и;тФж" у . изайисывается единица, при убывании вход- дуляции, в него введены фильтр низкой ча - його сигнала записывается нуль. Выход стоты, преобразователь полярности и сум- "-трйггера задержкй является"выходом уст- матор, причемвыход триггера задержки соройства."-15; единен с входом преобразователя полярноКроме того, выходной сигпал подается %ЫЯйход которого соединен с первым вхона преобразователь 4 полярности, который -" дом сумматора и входом фильтра низкой формирует сигнал с одинаковой положи- впп ЖФИЬты выход которого соединен с вторым тельной и отрицательной амплитудойвходом сумматора, выход сумматора под(фиг. 2 б). 20 ключен квходу интегратора.Фильтр 3 низкойчастотй выделяет низ- Источники информации, ="="-"кочастотную составляющую цифрового сиг-"принятые во внимание при экспертизе нала (фиг. 2 в). Низкочастотная составля. К 51 ее 1 е Рейа гподц 1 а 11 опз з 1 Ыегпз. ющая и цифровой сигнал через сумматор Еопйоп, Реп 1 есЬ Ргезз, 1975, с. 4, рис. 1.1,а. 5 (фиг. 2 г) управляют интегратором., 25 2. Венедиктов, Женевский, Марков, ЭйИспользование для управления интегра- дус. Дельта-модуляция. Теория и применетором низкочастотной составляющей позво- ние, М; Связь, 1976, с. 188, рис. 7.8 (про- "Т ляет значительно"повысить точность моду- тотип). ляции; так как производится более эффективное управление интегратором. ЗОВыходгЛография, пр. Сапунова,каз 126/12 Изд.174 Тираж 995НПО Поиск Государственного комитета СССР по делам изобретсни 113035, Москва, Ж, Раушская наб., д, 4/5 Подписно открытий

СмотретьЗаявка

2608471, 24.04.1978

РИЖСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, ШУЛЬГА СТАНИСЛАВ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 13/22

Метки: дельта-модулятор

Опубликовано: 29.02.1980

Код ссылки

<a href="https://patents.su/3-718920-delta-modulyator.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-модулятор</a>

Предыдущий патент: Частотный преобразователь

Следующий патент: Многоканальное переключающее устройство

Случайный патент: Амортизирующий водяной затвор стоков санитарно-бытового оборудования