Генератор цифровых и аналоговых испытательных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

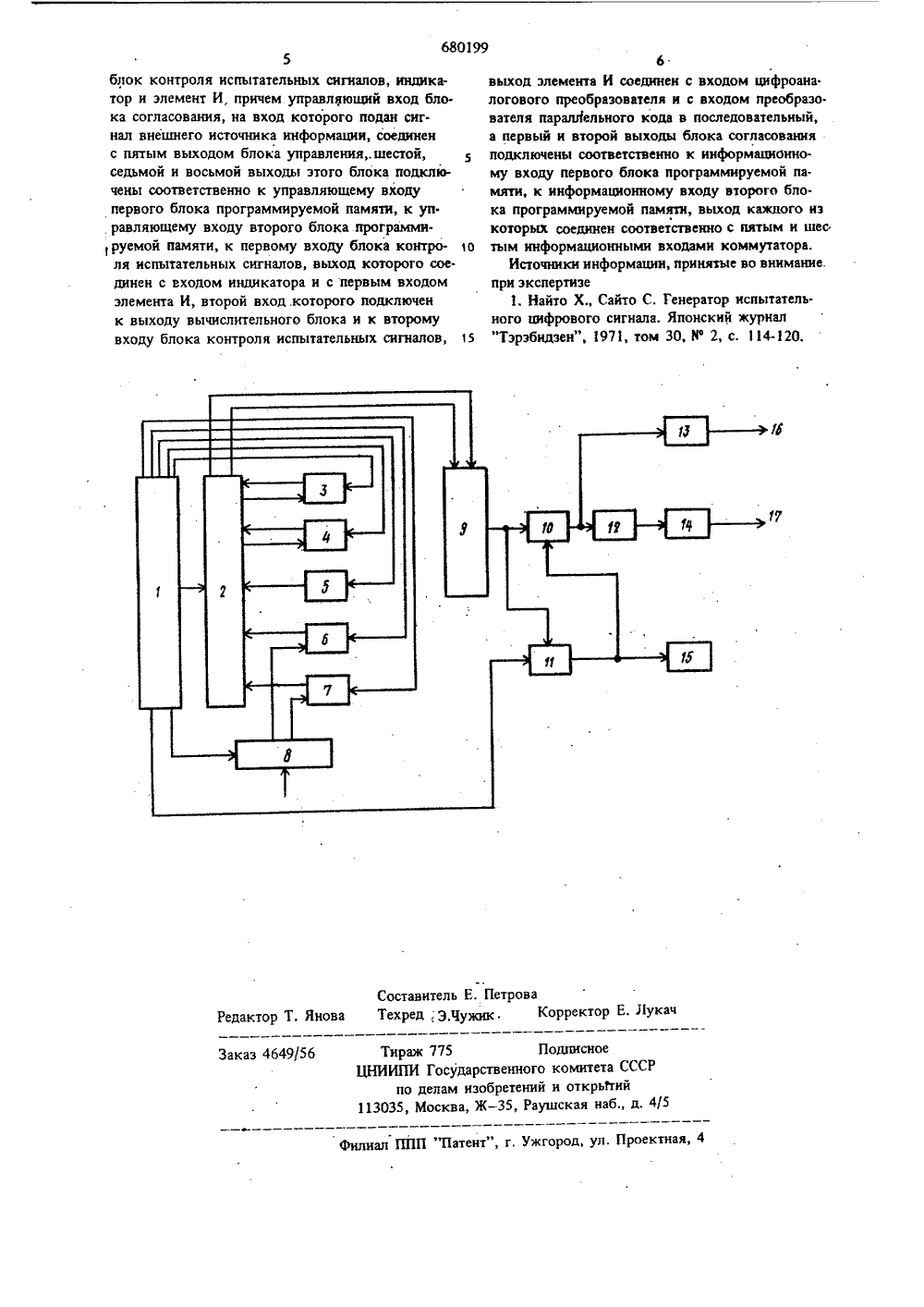

Союз Советсеа Соцмалмстнцескик РеспубпмкОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пи 680199(6) Дополнительное к авт. свнд.ву 51) М, Кл,) Заявлено 21.09.77 121) 2529365/18-09 присоединением з 1 ч 7 Яе ударетвенный иеетет СССР на д ам изобретений етнрытнй(71) Заявител ГЕНЕРАТОР ЦИФРОВЫХ И АНА ИСПЫТАТЕЛЬНЫХ СИ ГНАЛ ГОВЫХВ нные цифроаналоговыйтр низкой частоты,последовательно вклю ил преобразователь и фвыход которого явлгенератора 11.Однако известныйтельной сложностью иконтроль работоспособлоков. выход тся вт нератор обладает значие позволяет производитьости входящих в него 10 тветственно мутатора, к упр оперативной па яти, и и вых иными входо вторым выходаляюшему входуформационныйим входом ком рмационн ходами вычисараллельногокоторого явля Изобретение относится к связи и может и льзоваться для контроля качества каналов связи,Известен генератор цифровых и аналоговыхиспытательных сигналов, например, для контроля каналов связи, содержаший блок управления,первый, второй, третий и четвертый выходы которого подключены соответственно к управляюшему входу коммутатора, к управляюшему вхо.ду первого блока оперативной памяти, подключенного информационнымн входом и выходом м выходу и входу ком. шему входу второго блок одключенного информаци. одом соответственно к м и входу коммутатора, к уп блока постоянной памяти, ин выход которого соединен с трмутатора, третин и четвертыи е выходы этого коммутатора соединены соответственно с первым и вторь ительного блока, преобразователода в последовательный, выходтся первым выходом генератора Шлайн и М. А. Рабинович Целью изобретения является упрощение уст. ройства за счет сокрашения объема блоков пос. тоянной памяти и самоконтроля его работы.Для этого в генератор цифровых и аналоговых испытательных сигналов, например, для контроля каналов связи, содержащий блок управ ления, первый, второй, третий н четвертый вы. ходы которого подключены соответственно к управляюшему входу коммутатора, к управляющему входу первого блока оперативной памяти, подключенного информационными входом и вы. ходом соответственно к первым выходу н входу коммутатора, к управляюшему входу второ. го блока оперативной памяти, подключенного информационными входом и выходом соответ. ственно к вторым выходу и входу коммутато.6801993ра, к управляюшему входу блока постояннойпамяти, информационный выход которого соединен с третьим входом коммутатора, третий.и четвертый информационные выходы этого коммутатора соединены соответственно с первым ивторым входами вычислительного блока, преобразователь параллельного кода в последовательный, его выход является первым выходом генератора, последовательно включенные цифроана.логовый преобразователь и фильтр низкой часто Оты, выход последнего является в 1 орым выходом генератора, введены блок согласования, дваблока программируемой памяти, блок контроляиспытательных сигналов, индикатор и элементИ, причем управлявший вход блока согласова 15ния, на вход которого подан сигнал внешнегоисточника информации, соединен с пятым вы/ходом блока управления, шестой, седьмой ивосьмой выходы этого блока подключены соответственно к,управляющему входу первого бло- э 0ка программируемой, памяти, к управляющемувходу второго блока программируемой памяти,к первому входу блока контроля испытательныхсигналов, выход которого соединен с входоминдикатора и с перВым входом элемента И, второй вход которого подключен к выходу вычислительного блока и к второму входу блокаконтроля испытательных сигналов, выход эле.мента И соединен с входом цифроаналоговогопреобразователя и с входом преобразователя з 0параллельного кода в последовательный, а пер.вый и второй выходы блока согласования подключены соответственно к информационномувходу первого блока программируемой памяти,к информационному входу второго блока программируемой памяти, выход каждого из кото.рых соединен соответственно с пятым и шестыминформационными входами коммутатора, .На чертеже приведена структурная электричес.кая схема предложенного генератора. 40Генератор цифровых и аналоговых испытатель.ных сигналов содержит блок 1 управления, коммутатор 2, первый блок 3 оперативной памяти,второй блок 4 оперативной памяти, блок 5 постоянной памяти, два блока 6 и 7 программируе 45мой памяти, блок 8 согласования, вычислитель.ный блок 9, элемент И 10, блок 11 контроляиспытательных сигналов, цифроаналоговый преобразователь 12, преобразователь 13 параллельного кода в последовательный, фильтр 14 низкой частоты, индикатор 15, соответственно первый и второй выходы 16 и 17,Генератор работает следующим образом.Блок 1 управления задает цикл работы всегогенератора, а также при необходимости включает блок 8, который служит для обновления информации, записанной в блоках 6 и 7, а так какпоследние имеют низкое быстродействие, то. информация через коммутатор 2 поступает на пер 4вый и второй блоки 3 и 4. В блок 5 информацйя записывается при изготовлении прибора.В соответствии с циклом работы генератора информация считывается с требуемой скоростью с первого и второго блоков 3 и 4 и блока 5 и через коммутатор 2 подается на вычислитель- ный блок 9, затем информация через элемент И 10 поступает на цифроаналоговый преобразователь 12, преобразующий цифровой код в аналоговую величину, и на фильтр 14, с выхода ко 1 орого испытательный сигнал поступает в аналоговый канал - второй выход 17 генератора.Преобразователь 13 преобразует параллельный код в последовательный, с его выхода испытательный сигнал поступает в цифровой канал - первый выход 16. генератора. Блок 11 контро: лирует цифровые испытательные сигналы, индикатор 15 ицпицирует режим неправильной работы генератора и предотврашает выдачу неправильного сигнала. Блок 11 контроля может быть выполнен по любой известной схеме контроля цифровых сигналов,Предложенный генератор отличается простотой и позволяет исключить возможность выдачи нс. пытательных сигналов, не соответствуюших заданным.Формула изобретенияГенератор цифровых и аналоговых испытательных сигналов, например, для контроля каналов связи, содержащий блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющему входу коммутатора, к управляюшему входу первого блока оперативной памяти, подключенного информационными входами и выходом соответственно к первым ввходу и входу коммутатора, к управляюшему входу второго блока оперативной памяти, подключенного информационными входом и выходом соответственно к вторым выходу и входу коммутатора, к управляющему входу блока постоянной памятн,.информационный выход которого соединен с третьим входом коммутатора, третий и четвертый информационные выходы которого соединены соответственнос первым и вторым входами вычислительного. блока, преобразователь параллельного кода в последовательный, его выход является первым выходом генератора, последовательно включенные цифроаналоговый преобразователь и фильтр низкой частоты, выход последнего является вторым выходом генератора, отличаюшийся тем, что, с целью упрощения устройства за счет со-. крашения объема блоков постоянной памяти исамоконтроля его работы, введены блок согла.сования, два блока программируемой памяти,аказ 4649/56 Подписноеого комитета СССний и открьггийРаушская наб., д. по 13035, филиал ород, ул. Проектн 5блок контроля испытательных сигналов, индикатор и элемент И, причем управляющий вход блока согласования, на вход которого подан сигнал внешнего источника информации, соединен с пятым выходом блока управления,.шестой, седьмой и восьмой выходы этого блока подключены соответственно к управляющему входу первого блока программируемой памяти, к уп.равляющему входу второго блока лрограмми.руемой памяти, к первому входу блока контро ля испытательных сигналов, выход которого сое. динен с входом индикатора и с первым входом элемента И, второй вход. которого подключен к выходу вычислительного блока и к второму входу блока контроля испытательных сигналов, 15 6выход элемента И соединен с входом цнфроана логового преобразователя и с входом преобразо. вателя паралйльного кода в последовательный, а первый и второй выходы блока согласования подключены соответственно к информационному входу первого блока программируемой памяти, к информационному входу второго бло. ка программируемой памяти, выход кажного из которых соединен соответственно с пятым и шее тым информационными входами коммутатора.Источники информации, принятые во внимание. при экспертизе1. Найто Х Сайто С. Генератор испытатель. ного цифрового сигнала, Японский журнал "Тэрэбидзен", 1971, том 30, Н 2, с. 114-120,

СмотретьЗаявка

2529365, 21.09.1977

ПРЕДПРИЯТИЕ ПЯ А-7306

КРИВОШЕЕВ МАРК ИОСИФОВИЧ, ШЛАЙН АЛЕКСАНДР ИСААКОВИЧ, РАБИНОВИЧ МИХАИЛ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H04N 7/02

Метки: аналоговых, генератор, испытательных, сигналов, цифровых

Опубликовано: 15.08.1979

Код ссылки

<a href="https://patents.su/3-680199-generator-cifrovykh-i-analogovykh-ispytatelnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор цифровых и аналоговых испытательных сигналов</a>

Предыдущий патент: Устройство формирования сигнала изображения

Следующий патент: Формирователь стробирующего сигнала

Случайный патент: Анализатор спектра непериодических сигналов