Способ выделения ошибок из испытательного псевдослучайного сигнала в виде м-последовательности и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

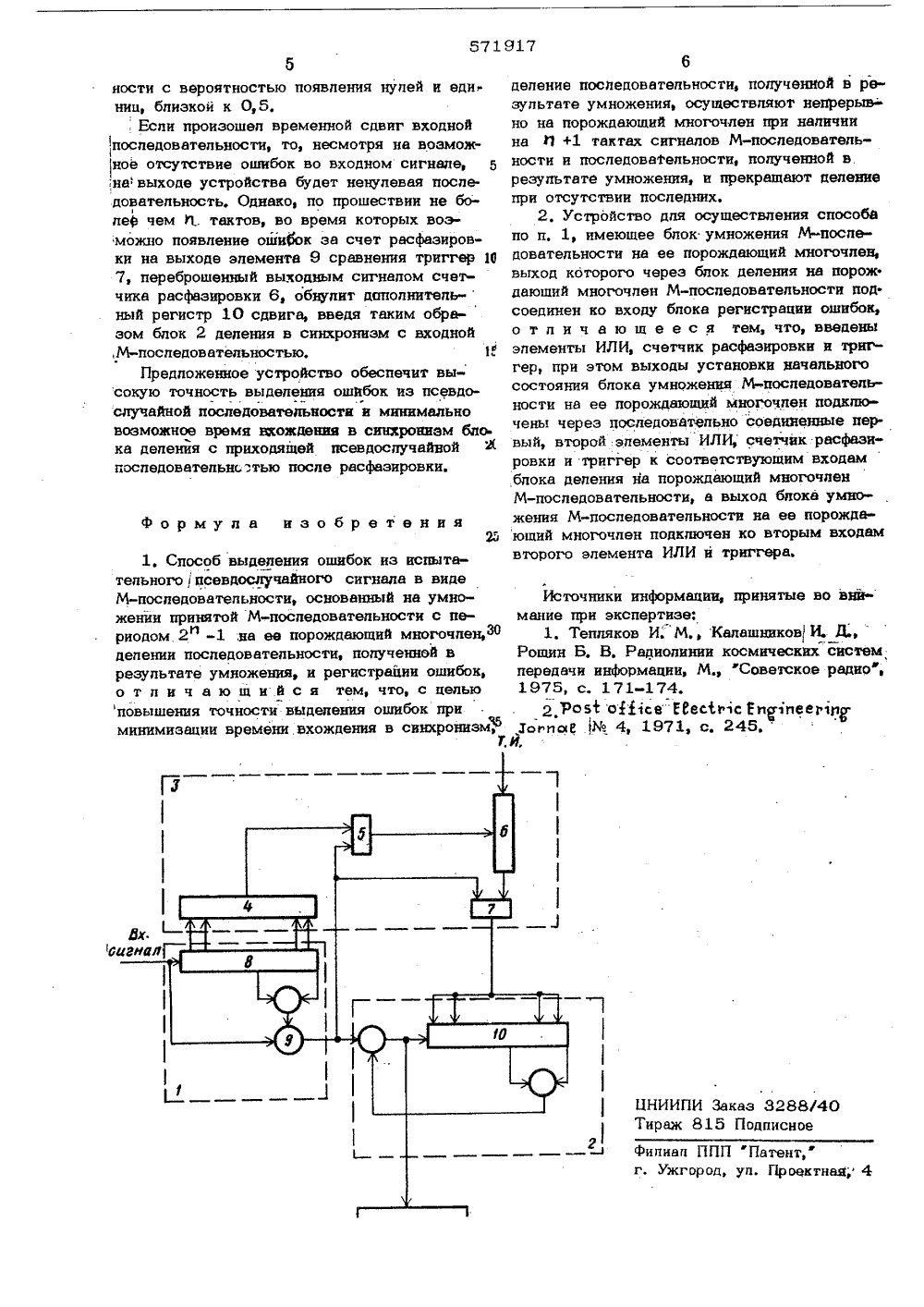

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДОВДЬСТВУ Союз СоветскихСоциал истицескихРеспублик(5) 4 В 3 присоединением заявки3) Приоритет Государственный кометеСовете Мнннстров СССРоо делам изобретенийн открытий,77 исания,1 12) Авторы изобретения никин и А В л Заявитель(54) СПОСОБ ВЪДЕЛЕНИЯ ОШИБОК ИЗ ИСПЫ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА В ВИДЕ М-ПОСИ УСТРОЙСТВО, ДЛЯ ЕГО ОСУШЕ АТЕЛЬНОГОЛЕДОВАТЕЛЬНОСТИВЛЕНИЯ едаче цифроьэоваться в ти при переакже в устро Известно устройство дпя осуществления способа выделения ошибок иэ псевдослучайного сигнала, содержащее ключ, регистр сдвига, селектор, полусумматоры н,счетчик сов- щ падений. Вход устройсзьа соединен со входом одного полусумматора и с: одйнм полтосом ключа, выход которого связан со: входом регистра сдвига, К выходам ячеек. регистра сдвига подсоединены входы инолусумматоров,со ц единение которых между собой.и ячейками регистра образует цепь обратной связи,. а.также входы селектора, выход которого:под-. ключен параллельно к входу счетчйка и к ключу. Выход цепи обратной связи, являющий-Ю ся выходом одного иэ полусумматоров цепи обратной связи, соединен со вторым полюсом ключа и другим входом того полусумма-. тора, на который также подается входной сит, нап. Выход этого попусумматора подключен 5 го нно Изобретение относил:я к вой информации и может исп измерителях потери доставер дачи цифровой информации, а ствах синхронизации. к другому входу счетчика, причем выхо последовательно подсоединен к ключу 1.Однако такое устройство обацеает й 1 етязотаточной точностью выделения ошибок.Наиболее .близким по технической сущности к предлагаемому изобретению являетсяспособ выявления ошибок иэ.испытательногосигнала ввиде Я-Последовательности, основанный, ю: умножениа принятой М-последовательности 2 -Х:не ее норождающий многоттчлен, делении последовательности, подключееной в результате умножения на три и регвст,рации ошибок, и устройство для осуществления этого способа, снабженное блоком умножения М-последовательности на ее порождающий многочлен, выход которого через блокделения на три подсоединен ко входу блокерегистрации ошибок ),2,Однако этот способ и устройство дляалнзапии неь обеспечивают высокой то выделения ошибок, так как одновремсходным псевдослучайным сигналомождающий многочлен умножителя пряхоток ошибок, а деление числа ошибо57 1917, 3три приводит лишь к приближенной оценкечисла действительных ошибок.Цель изобретения - йовышение точностивыдепения ошибок при минимизации временивхождения в синхронизм. 5йаю етого в способе выделения ошибокиз испытательного сигнапа в виде М-поспедовательности, основанном на умножениипринятой М-последовательности с периодом2 -1 на ее порождающий многочлен, депеВнии последовательности, полученной в результате умножения, и регистрации ошибок, депение носпедовательности, подученной в ре:зупьтате умножения, осуществляют непрерыв 1но на порождающий многочлен при наличиина . П +1 тактах сигналов М-последовательности и последовательности, полученной в реэультате умножения, и прекращают делениепри отсутствии поспеднихВ устройство дляооуществления способа, имеющее блок умноженим М-последовательности на ее порождающий многочлеи, выход которого через блокделения на порождающий многочлен М-после-доватепьности подсоединен ко входу блокарегистрации ошибок, введены элементы ИЛИрсчетчик расфазировки и триггер, при этомвыходы установки начального состояния блока умножения М-последовательности на еепорождающий многочпен подкпючены черезпоследовательно соединенные первый, второй,ЗОэлементы ИЛИ, счетчик расфазировки и триггер к соответствующим входам бпока деденияна порождающий многочлен М-последоватепьности, а выход блока умножения М-поспедовательнооти не ее порожпаощий многочпен попоНИипочен ко вторым входам второго элементаИЛИ и триггера,На чертеже представлена структурная электрическая схема устройства для осуществления способа выделения ошибок из испытательно)ного сигнала в виде М-последовательности.Устройство содержит блок 1 умно 1 кения М 1последовательности на ее порождающий многочпен, выход которого через блок 2 деления на порождающий многочлен М-поспе- чбдовательности подсоединен ко входу блока 3регистрации ошибок, а также элементы ИЛИ4, 5, счетчик 6 расфазировки и триггер 7,при этом выходы установки начального сос- .тояния блока 1 умножения М-последоватепьбОности на ее порождающий многочлен подключЕны через последовательно соеднненнье пер.вый 4, второй 5 элементы ИЛИ, счетчик 6расфазировки и триггер 7 к соответствующимвходам бпока деления 2 на порождающий многочлен М-последовательно, а выход блокаумножения 1 М-последовательности на еепорождающий многочлен подкдючен - ко вторым входам второго элемента ИЛИ 5 и триг,гера 7, М, 4Сигнал М-последовательности, приходя: щий с исследуемого тракта, умножается йа" многочлен, порождаюший 1 эту М-последовательность.,По прошествии ц тактов (где И - максимальный показатель степени порождающего многочлена) после подачи входного сигнала вти с момента расфаэировки сдвигам входной М-последовательности во времени - на выходе блока 1 умножения остается лишь последовательность ошибок,умно- женная на порождающий многочлен, Если прй наличии М-последовательности на входе бл 6 ка 1 после укаэанного выше момента в течение К тактовых интервалов (где КЪИ) на выходе бпока 1 множения не будет ни одной ошибки, то значительно возрастет вероятность отсутствия ошибки в течение того же промежутка времени и во входном сигнале.: С увеличением К эта вероятность возрас- тает, однако с достаточной для практики тснностью можно принять К = М + 1, Если в этот момент установить блок 2 деления в нулевое состояние, т.е. задать нулевые начапьные условия, то последующие ошибки, пройдя блок 1 умножениян будут правильно выдепяться блоком 2 деления.Устройство, реализующее предложенныйспособ, работает следующим образом.В случае отсутствия ошибок во входной,М-последовательности, поступающей на входрегистра 8 сдвига и вход алемента 9 сравнения блока 1 умножения на входе элемента 9 сравнения сохраняется состояние логического нуля, При этом отсутствует сигналсброса счетчика 6 расфазировки, устанавливающего триггер 7 в состояние, при которомон нобнуляет все ячейки дополнительного регистра 10 сдвига, блоком 2 депения. Очевидно, что на выходе всего устройства сохраня-ется логическое состояние нуля.При наличии во входном сигнале ошибокпервая иэ них, выделенная элементом 9 срав.нения, сбрасывает счетчик 6 расфаэировкии устанавливает триггер 7 таким образом,что снимается сигнал обнупения дополнительного регистра 10 сдвига,После чего начинает работать блок 2 деления на порождающий многочлен, который,должен произвести правильное выдепение имеющегося во входном сигнале потока ошибок,При перерыве связи сигнал с выхода элемента ИЛИ 4 через элемент ИЛИ 5 сброситсчетчик 6 расфаэировки, а триггер 7 останется в нулевом состоянии, в которое он будет установлен ошибками, выделяющимися втечение И тактов с момента возникновенияперерыва на выходе элемента 9 сравнения.В этом спучае блок деления 2 будет работать в режиме генерации М-послелователь571917 аи ИПИ Заказ 3288/40аж 815 Подписное г ности с вероятностью появления нулей и еди ниц, близкой к 0,5.: Если произошел временной сдвиг входнойпоследовательности, то, несмотря на возможное отсутствие ошибок во входном сигнале, 5 на выходе устройства будет ненулевая поспедовательность. Однако, по прошествии не боле 9 чем И., тактов, во время которых возможно появление ошибок за счет расфазировки на выходе элемента 9 сравнения триггер 10 7, переброшенный выходным сигналом счет чика расфазировки 6, обнулит дополнитель-ный регистр 10 сдвига, введя таким образом блок 2 деления в сннхрониэм с входной , М-последоватеельностью, 1 сПредложенное устройство обеспечит высокую точность выделения ошибок из псевдоРслучайной последовательности и минимально возможное время нхождения в сиихровнэм блока деценйя с приходящей псевдослучайной последовательн:тью после расфазировки,формула изобретения25 1. Способ выделения ошибок иэ испытательного,псевдослучайного сигнала в виде М-поспедовательности, основанный на умно женйи принятой М-последовательности с периодом 2 -1,на ее порождающий многочлен ЗО делении последовательности, полученной в результате умножения, и регистрации ошибок, о т л и ч а ю щ и й с я тем, что, с целью повышения точности выдепения ошибок при минимизации времени вхождения в синхронизм 7Т,6депение посцедовательности, попученной в результате умножения, осуществляют непрерывно на порождающий многочлен при наличийна 11 +1 тактах сигналов М-последовательности и последовательности, подученной в.результате умножения, и прекращают делениепри отсутствии цоследних,2, Устройство дця осуществления способапо п. 1, имеющее блок умножения М-поспедовательности на ее порождающий многочпен,выход которого через блок деления на порождающий многочлен М-последовательности под.соединен ко входу блока регистрации ошибок,о т л и ч а ю щ е е с я тем, что, введеныэлементы ИЛИ, счетчик расфазировки и триггер, при этом выходы установки начальногосостояния блока умножения М-последоватецьности на ее порождающий многочлен подкпючены через последовательно соединенные первый, второй эпементы ИЛИ, счетчик расфаэировки и триггер к соответствующим входамблока деления на порождающий многочленМ-поспедовательности, а выход блока умножения М-последовательности на ее порождающий многочлен подкпючен ко вторым входамвторого элемента ИЛИ и триггера. Источники информации, принятые во внймание при экспертизе:1, Тепляков И; М., Калашников И. Й.,Рощин Б, В, Рариолинии космических системпередачи информации, М., Советское радиоф,1975, с. 171-174.2,1 рой ой 1 се- Иес 1 мс РирпеегюХогпоб Ио 4, 1971, с. 245.И,фипиап ППП Патент, Ужгород, ул. Проектная,

СмотретьЗаявка

2192056, 21.11.1975

ПРЕДПРИЯТИЕ ПЯ А-7306

МИНКИН ВЛАДИМИР МАРКОВИЧ, УГЛОВ АЛЕКСАНДР БОРИСОВИЧ

МПК / Метки

МПК: H04B 3/46

Метки: виде, выделения, испытательного, м-последовательности, ошибок, псевдослучайного, сигнала

Опубликовано: 05.09.1977

Код ссылки

<a href="https://patents.su/3-571917-sposob-vydeleniya-oshibok-iz-ispytatelnogo-psevdosluchajjnogo-signala-v-vide-m-posledovatelnosti-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ выделения ошибок из испытательного псевдослучайного сигнала в виде м-последовательности и устройство для его осуществления</a>

Предыдущий патент: Радиоприемное устройство для приема сигналов с “плавающей” несущей частотой

Следующий патент: Устройство для контроля канала связи

Случайный патент: Устройство для очистки масляных фильтров двигателей внутреннего горения