Устройство для сопряжения аналоговых и цифровых вычислительных машин

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

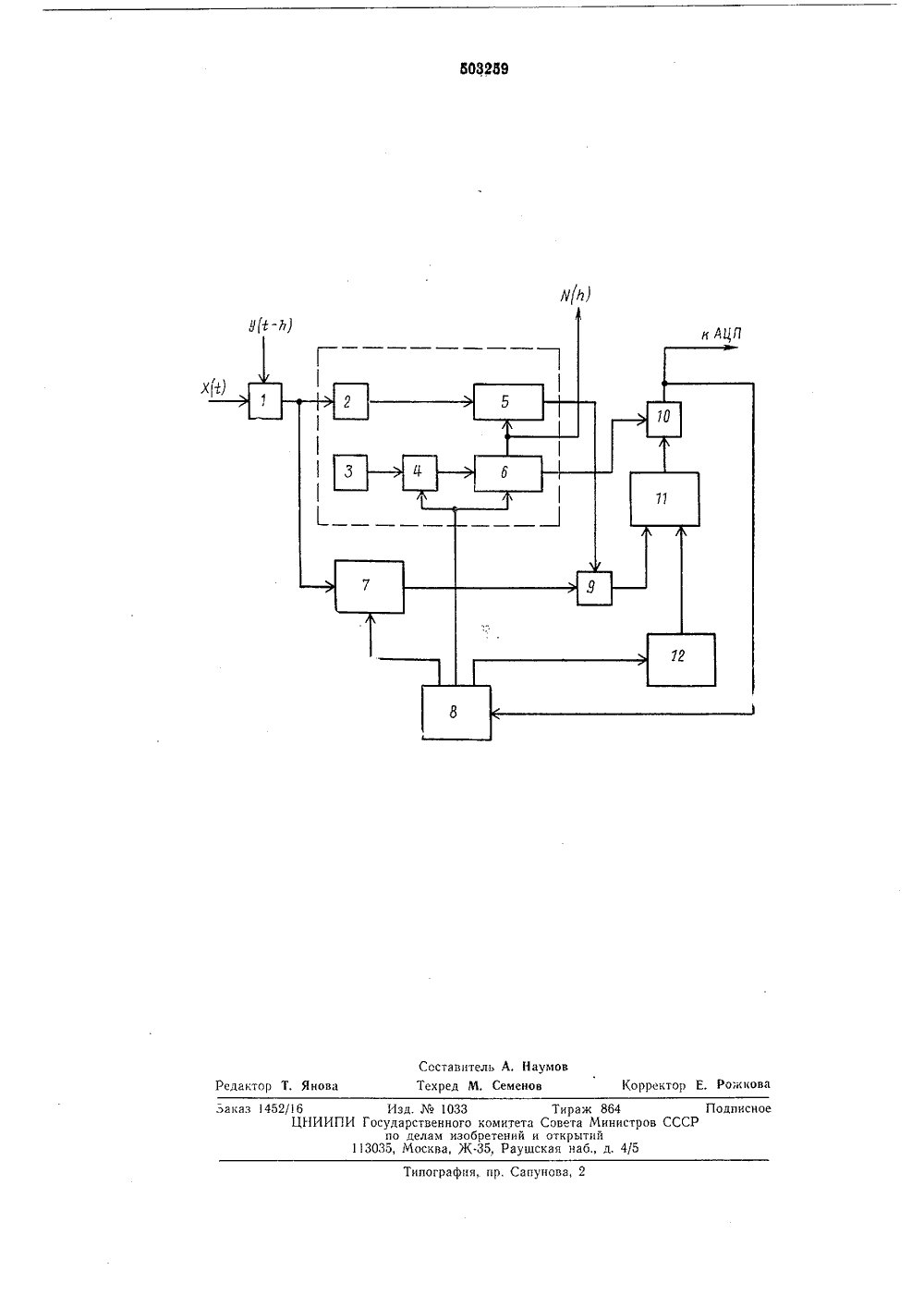

О П И С А Н И Е р) 03259ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советскив Социалистических Республик(22) Заявлено 05,10.73 ( 61472 18-2 рис нием заявкиГосударственный комитет Совета Министров СССР 3) Приоритетубликовано 15,02,76. Бюллетеньта опубликования описания 27.07.76(53) УДК 681,34(088.8) лам изобретенийи открытий 2) Авторы изобретени, Д. Михотин, К, В. Сафрон В нди 71) Заявитель Пензенский политехнический институ 4) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АНАЛОГОВЬ И ЦИ ФРО ВЪХ ВЫЧ И СЛ ИТЕЛ ЬНЫХ МАШ И Н- максх 1 о.:г .ну 1 м второй производной изны х 11), взятый внутри инирования о, Й;ордината времени;тизации,ы остолагае Л, -максим вел ичи нтер пол щая ко дискре величин предп- модуль меряемой тервала и1 - теку 6 - шаг Оценка муле (1) аточного члена по форт дифференцирование Предлагаемое устройство относится к области преобразования и кодирования информации.Известны устройства для сонряжения аналоговых и цифровых вычислительных машии, 5содержащие генератор, логический элементИ, счетчик импульсов, управляющий входкоторого соединен с выходом блока управления, а первый выход - с первым входом логического элемента ИЛИ, блок управления 10через последовательно соединенные генераторпилообразного напряжения и блок сравнениясоединен со вторым входом логического элемента ИЛИ, вход блока управления соединен с выходом устройства и выходом логического элемента ИЛИ,Такие устройства сложны и не обладаютдостаточной помехозащищенностью.Предлагаемое устройство отличается от известных тем, что в,него введены усилитель, 2преобразователь код-напряжения, интеграторвычитающий блок и блок выделения разности,входы которого соединены с выходными клеммами устройства, а выход - с входом усилителя и первым входом интегратора, второй 2вход которого соединен с выходом блока управления, а выход интегратора - с первымвходом вычитающего блока, второй вход которого соединении с выходом преобразователякод-напряжение, его первый вход соединен с 3 выходом усилителя, а второи вход - с вторым выходом сче гчика импульсов, второй вход последнего соединен с выходом логического элемента И, вход которого соединен с выходом генератора, а управляющий вход - с блоком управления, что позволяет значительно упростить устройство,Предлагаемое устройство для сопряжения аналоговых и цифровых вычислительных машин обеспечивает выбор узлов интерполяции таким образом, что при воспроизведении измеряемой величины по ее дискретным значениям при помощи полинома Лагранжа первой степени максимальная абсолютная погрешность воспроизведения на всех участках близка к допустимому значению Яоп,При линейном интерполировании измеряемой величины значение остаточного члена в форме Коши определяется выражением220 25 зо 35 входного сигнала. Избежать это становится возможным, используя связь между модуль- максимумом второй производной и интегральным значением функциии л, =,х ф) - ) о й, 2) н где 1.(1) - интерполирующий полином Лагранжа первой степени.Из выражений (1) и (2) находится связь между максимальным значением остаточного члена и интегральным значением входного сигнала Устройство непрерывно следит за интегралом от разности измеряемой величины и интерполирующего полинома и сравнивает его с линеино-растущей функцией а, Й, определяющеи величину допустимои погрешности интерполяции, а в момент их равенства вырабатывает сигнал на измерение.На чертеже дана структурная схема предлагаемого устройства.Устройство содержит блок 1 выделения разности, усилитель , генератор 3, логический элемвнт И 4, преобразователь 5 код-напряжение, счетчик О импульсов, интегратор 7, блок 8 управления, вычитающий блок 9, логический элемент ИЛИ 10 блок 11 сравнения и генератор 12 пилообразного напряжения,Устройство работает следующим образом, Измеряемая величина х поступает на вход блока 1 выделения разности, где из нее вычитается результат предыдущего измерения у(, - Й), который снимается с 11 КН аналого-цифрового преобразователя. С выхода блока 1 выделения разности разность подается на интегратор 7 и блок моделирования интеграла от полинома 1.,(Г), в состав которото входит усилитель 2, генератор 3, логический элемент И 4, преобразователь 5 код-напряжение и счетчик 6 импульсов, В начальный момент в счетчике б записан О. По команде с блока 8 управления открывается схема И 4 и начинают поступать импульсы в счетчик б. Таким образом на выходе преобразователя 5 код-напряжение вырабатывается сигнал, описываемый выраже- нием С =. 1 х(1) - у(1 - Й) К ", (4)(7, К 1 х(1) - у(1 - Й) И,огде К, - коэффициент пропорциональности. Напряжения Уи с), подаются на вычитающий блок 9, сигнал с выхода которого поступает на блок 11 сравнения, где сравнивается с линейно-растущим напряжением ЯопЙ, получаемым с генератора 12 пилообразного напряжения. В момент, когдаЯЙ = Кхсй - К Е, (1) сй (6)о о происходит срабатывание блока 11 сравнения и через логический элемент ИЛИ 10 подается сигнал на измерение к АЦП и сигнал на блок 8 управления, возвращающий интегра. тор 7 и генератор 12,пилообразного напряжения в исходное состояние, а также счетчик б импульсов на нуль. В момент выдачи сигнала на измеренне числа ХЯ в счетчике б импульсов пропорционально размеру шага дискретизации.Подбирая величины К, и Я, можно задавать допустимое значение погрешности интерполяции. Ф ор мул а изобр етен ия Устройство для сопряжения аналоговых и цифровых вычислительных машин, содержащее генератор, логический элемент И, счетчик импульсов, управляющий, вход которого соединен с выходом блока управления, а первый выход - с первым входом логического элемента ИЛИ, блок управления через последовательно соединенные генератор пилообразного напряжения и блок сравнения соединен со вторым входом логического элемента ИЛИ, вход блока управления соединен с выходом устройства и,выходом логического элемента ИЛИ, отличающееся тем, что, с целью упрощения устройства, в него введены усилитель, преобразователь код-напряжение, интегратор, вычитающий блок и блок выделения разности, входы которого соединены с входными клеммами устройства, а выход - с входом усилителя и первым входом интегратора, второй вход которого соединен с выходом блока управления, а выход и 1 нтегратора - с первым входом вычитающего блока, второй вход которого соединен с выходом преобразователя код-нап)ряжение, его первый вход соединен с выходом усилителя, а второй вход - с вторым выходом счетчика импульсов, второй вход последнего соединен с выходом логического элемента И, вход которого соединен с выходом генератора, а управляющий вход - с блоком управления.5 аказ 1452/6 Изд.1033 Тираж 864 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж.35, Раушская наб., д. 4/5 Типография пр. Сапунова, 2

СмотретьЗаявка

1961472, 05.10.1973

ПЕНЗЕНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

МИХОТИН ВЛАДИМИР ДМИТРИЕВИЧ, САФРОНОВА КЛЕРА ВАСИЛЬЕВНА, ШЛЯНДИН ВИКТОР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06J 3/00

Метки: аналоговых, вычислительных, машин, сопряжения, цифровых

Опубликовано: 15.02.1976

Код ссылки

<a href="https://patents.su/3-503259-ustrojjstvo-dlya-sopryazheniya-analogovykh-i-cifrovykh-vychislitelnykh-mashin.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения аналоговых и цифровых вычислительных машин</a>

Предыдущий патент: Цифро-аналоговое вычислительное устройство

Следующий патент: Аналого-цифоровое устройство для возведения в куб

Случайный патент: Способ автоматического учета основных показателей работы драглайна