Запоминающее устройство аппаратуры передачи данных с автоматическим запросол ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 425369

Автор: Изобретен

Текст

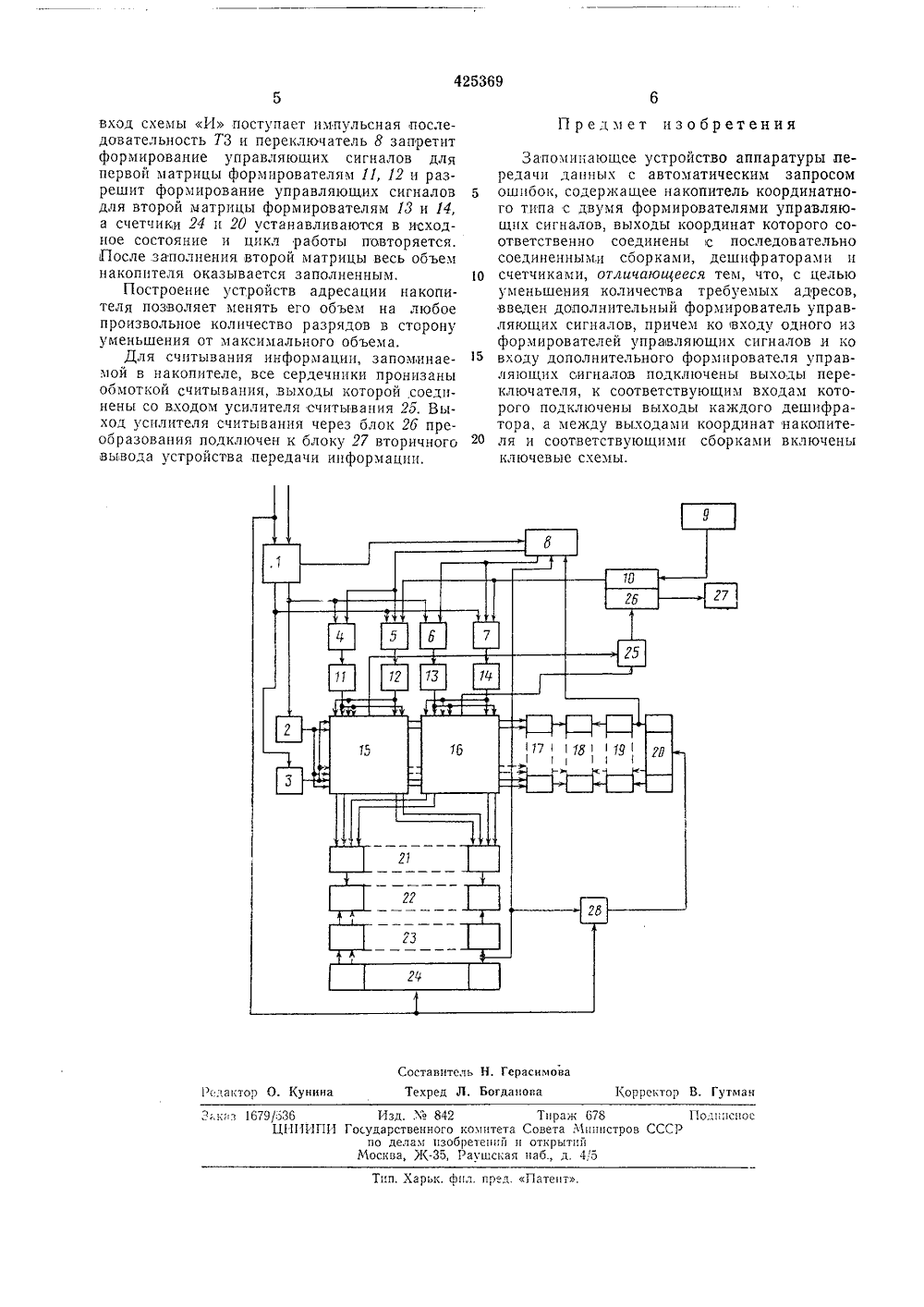

Союз СоветскихСоциалистическихРеспублик ОПИСАНИЕ ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ тельства - 1728153 26-9 1) Зависимо вт. св,12,7 51) Ч, КлН 041250 явки осударстевнный ивмн Совета Министров СС пв делам изобретениин открытий ДК 621.394.395 08 М),04.74. Бюллетень М 15 ата опубликования описания 15,1.7 72) Авторы иэобретени 71) Заявитель. Дуничева, К. каров и Ю, Д, Халезов ЗАПОМИ НАЮЩЕЕ УСТРОЙСТВО АП ПЕРЕДАЧИ ДАННЫХ С АВТОМАТИЧЕЗАПРОСОМ ОШИБОК РАТУРЫИМ Изобретение относится к области телеграфной связи, а именно к запоминающимустройствам аппаратуры передачи данных с автоматическим запросом ошибок.Известно запоминающее устройство, содержащее накопитель координатного тила сдвумя формирователями управляющих сигналов, выходы координат которого соответственно соединены с последовательно соединенными сборками, дешцфраторами и счетчиками.Цель изобретения - уменьшение количества требуемых адресов,Для этого в предлагаемое запоминающееустройство введен дополнительный формирователь управляющих сигналов, причем ко входу одного из формирователей управляющихсигналов и ко входу дополнительного формирователя управляющих сигналов подключенывыходы .переключателя, к соответствующимвходам которого, подключены выходы каждогодешифратора, а между выходами координатнакопителя и соответствующими сборкамивключены ключевые схемы,На чертеже приведена функциональнаясхема запоминающего устройства.Выходы распределителя 1 подключены кформирователям 2 и 8 управляющих сигналовпо осц У, к схемам И 4 -ц ко входу переключателя 8. Выходы переключателя 8 подключены ко второму входу схем И 4 - 7. Третий вход схем И 5 и 7 связан с источником 9 кодовых комбинаций через схему 10 ввода; Выходы схем 1 Л 4 - 7 соединены с формирователями 11 - 14 управляющих сигналов по оси Х. Формирователи 2 й 3 подключены к горизонтальным (ось ) шинам записи и чтения матриц 15 ц 16, соединенным последовательно (на чертеже условно показаны перваявторая ц последняя группа шиц) с накопителем координатного тцпаВыходы шци соединены со сборками ИЛИ 17 ца два входа каждая, выходы которых поступают на ключевые схемы И 18.На второй вход ключевой схемы И поступают сигналы с дешцфратора 19 состояшй счетчика 20. Выходы вертикальных шцн матриц 15 и 16 соединены со сборками 1 Л,Ч 1 Л 21 ца четыре входа, выходы которых подключены к ключевым схемам И 22, ца второй вход ключевых схем И поступают сигналы с дешцфратора 28 состояний счетчцка 24. Обмотка считывания матриц подключена к усилителю считьнвания 25, выход которого соединен с блоком 26 преооразовацця. Выход блока преобразования подключен к блоку 27 вторичного вывода. Счетчики 24 и 20 соединены последовательно через схему И 28.Тактовые импульсы высокой частоты инизкой частоты поступают ца распределитель ЗО 1, ца выходе которого формируются цмпуль5 1 О 15 20 25 30 35 40 45 50 55 60 Б 5 сные последовательности Т 1, Т 2, Т 3, сдвинутые друг относительно друга на семь лксек.Тактовые импульсы низкой частоты, кроме того, поступают ца четырехразрядный счетчик 24 адресов.,Весь объем накопителя координатного типа разделен на две матрицы 15 и 16 для упрощения схемы,и уменьшения количества активных элементов. По оси У шины чтения и записи матриц соединены последовательно. На вход формирователя 2 поступает импульсная последовательность Т с выхода распределителя 1. Сформированный управляющий сигнал с выхода формирователя 2 поступает параллельно ца все шины чтения по оси У.На вход формирователя 3 поступает импульсная последовательность Т 2 с выхода распределителя 1, Сформированный управляющий сигнал с выхода формирователя 3 поступает параллельно на все шины записи по осцДля формирования управляющего сигнала Чтение Х для первой матрицы импульсная ,последовательность Т 1 поступает на вход схемы И 4, на,другой вход которой поступает сигнал Разрешение цз переключателя 8.С выхода схемы И 4 сигнал поступает ца вход формирователя 11 управляющего сигнала Чтение Х 1. С выхода формирователя сигнал поступает параллельно на все шины чтения первой матрицы.Для формирования управляющего сигнала Чтение Х 2 для второй матрицы импульсная последовательность Т 1 поступает на вход схемы И 6, на другой вход которой поступает сигнал Разрешение из переключателя 8. С выхода схемы И 6 сигнал поступает на вход формирователя 13 управляющего сигнала Чтение Х 2.С выхода формирователя сигнал поступаетна все шины чтения второй матрицы.Для формирования сигнала Запись Х 1для первой матрицы импульсная последовательность Т 2 с выхода распределцтеля 1 поступает на вход схемы И 5, На второй вход схемы И 5 поступает сигнал Разрешение из переключателя 8. На третий вход схемы И 5 поступает сигнал Информация из источника 9 кодовых комбинаций через схему 10 ввода информации. С выхода схемы И 5 сигнал поступает на вход формирователя 12, с выхода которого сформированный сигнал Заспись Х поступает параллельно на все шины записи первой матрицы 15.Для формирования сигнала Запись Х 2для второй матрицы импульсная последовательность Т 2 с выхода распределителя 1 поступает ца вход схемы И 7. На второй входсхеьы И поступает сцпал Разрешение цз переключателя б. На третий вход схемы И 7 поступает сигнал Информация из источника 9 кодовых комбинаций через схему 10 ввода ицфсрмации. С выхода схемы И 7 сигнал поступает:а вход формирователя 14, с выхода которого сфорироваццы сигнал Запись Х 2 поступает параллельно на все шины записи второй матрицы 16,Такое построенне устройств формирования управляющих сигналов позволяет отказаться от использования обмоток компенсации в матрицах, что зцачительно улучшает помехоустойчивость и сиикает требования к схеме усилителя воспроизведения, а также, позволяет значительно упростить усгройство адресации.Для формирования адресов Х первой и второй матриц тактовые импульсы низкой ча стоты поступают на вход счетчика 24, Выходы разрядов счетчика 24 поступают в дешифратор 23, Сигналы с выходов дешифраторов 23 поступают на ключевые схемы И 22, Количество разрядов счетчика, схем И в дешцфраторе и ключевых схем определяется количеством столоцов Х одной матрицы.Шины Запись и Чтение Х первого столбца матрицы 15 соединены со сборкой ИЛИ 21, ца четыре входа для каждого столбца Х. На другие два входа поступают шины Заспись и Чтение Х 2 первого столоца матрицы 16. Ооъединенный сигнал с выхода сборки ИЛИ 21 поступает на ключевые схемы И 22. При наличии сигнала с дешцфратора 23 ключевая схема открывается ц создается цепь для прохождения сигналов Записи и Чтеция по столбцу Х в первую илц вторую матрицу в,зависимости от того, работают формирователи 11 и 12 или 13 и 14.Аналогичным образом формируются адреса на оси У. Счетчик 20 адресов У соединен последовательно со счетчиком Х через схему И 28. На один вход схемы И 28 поступает последнее состояние счетчика 24 с дешифратора 23. На другой вход - тактовые импульсы низкой частоты. Таким образом после заполнения счетчика 24 (т. е. отработки всех столбцов Х) идет сигнал на переключение счетчика У. Выходы разрядов счетчика 20 поступают в дешифратор 19 счетчика. Сигналы с выходов дешцфратора 19 поступают ца ключевые схемы И 18, Количество разрядов счегчика, схем И в дешифраторе и ключевых схем определяются количеством строк У в матрице. Шины Запись и Чтение У матрицы 16 соединены со сборкой ИЛИ 17 на два входа для каждой из строк У. Объединенный сигнал с вывода сборки ИЛИ 17 поступает на ключевую схему И 18. При наличии сигнала с дешифратора 19 ключевая схема открывается и создается цепь для прохождения сигналов Чтения и Записи по строке У.Из всего колчества сердечников только для одного произойдет суммированиеуправляющих сигналов. С приходом следующего такта ццзкои частот. счетчик переключится и будет работать следующий сердечник. После того, как полностью отработает первая матрица 15, т. е. досчитают до заполнения счетчики 24 и 20 на схему И, расположенную в переключателе 8, поступают сигналыпереполнения счетчиков 24 и 20, на третий425369 Предмет изобретения Составитель Н. ГерасимоваТехред Л. Богданова Корректор В. Гутман 1 едактор О, Кунина Вьказ 1679/336 Изд. М 842 Тираж 678 Поди испое Ц 11 ИИПИ Государственного комитета Совета Министров СССР по делам изобретений п открытий Москва, Ж, Раугискап наб., д. 4,5Тип, Харьк. фил. пред. Патент. вход схемы И поступает импульсная последовательность ТЗ и переключатель 8 запретит формирование управляющих сигналов для первой матрицы формирователям 11, 12 и разрешит формирование управляющих сигналов для второй матрицы формирователям И и 14, а счетчики 24 н 20 устанавливаются в исходное состояние и цикл работы повторяется. После заполнения второй матрицы весь объем накопителя оказывается заполненным.Построение устройств адресации накопителя позволяет менять его объем на любое произвольное количество разрядов в сторону уменьшения от максимального объема.Для считывания информации, запоминаемой в накопителе, все сердечники пронизаны обмоткой считывания, выходы которой соединены со входом усилителя считывания 2 о. Выход усилителя считывания через блок 26 преобразования подключен к блоку 27 вторичного вывода устройства передачи информации. Запоминающее устройство аппаратуры передачи данных с автоматическим запросом ошибок, содержащее накопитель координатного типа с двумя формирователями управляющих сигналов, выходы координат которого соответственно соединены с последовательно соединенными сборками, дешифраторами и 1 О счетчиками, отличающееся тем, что, с цельюуменьшения количества требуемых адресов, введен дополнительный формирователь управляющих сигналов, причем ко входу одного из формирователей управляющих сигналов и ко 15 входу дополнительного формирователя управляющих сигналов подключены выходы переключателя, к соответствующим входам которого подключены выходы каждого дешифратора, а между выходами координат накопите ля и соответствующими сборками включеныключевые схемы.

СмотретьЗаявка

1728153, 23.12.1971

Л. К. Дуничева, К. Е. Макаров, Ю. Д. Халезев

изобретен

МПК / Метки

МПК: H04L 25/00

Метки: автоматическим, аппаратуры, данных, запоминающее, запросол, ошибок, передачи

Опубликовано: 25.04.1974

Код ссылки

<a href="https://patents.su/3-425369-zapominayushhee-ustrojjstvo-apparatury-peredachi-dannykh-s-avtomaticheskim-zaprosol-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство аппаратуры передачи данных с автоматическим запросол ошибок</a>

Предыдущий патент: Устройство для формирования биортогональныхкодов

Следующий патент: Маркер автоматической междугородной телефонной станции

Случайный патент: Прибор для измерения сопротивления сдвигу сыпучих материалов